基于System Generator中实现算法的FPGA设计方案详解

可编程逻辑

描述

0 引言

由于数字调制信号越来越多地应用于通信信号处理领域,因此对数字信号调制识别的研究也越来越多。传统的调制识别的判决方法有:决策判决法、高阶累积量算法和人工神经网络算法等。但是决策判决法在低信噪比环境中识别率不高,而基于人工神经网络的识别方法计算复杂度较高。信号的高阶累积量算法具有很好的抗噪性能,故对基于高阶累积量的通信信号调制识别算法的研究受到了广泛重视。文献利用高阶累积量实现了对 2ASK/BPSK,4ASK,4PSK,2FSK,4FSK信号的分类。文献利用四阶和六阶累积量实现了对 2ASK,4ASK,8ASK,QPSK,8P-SK,16QAM信号的分类。文献利用二、四、六阶累积量实现了对 2ASK/BPSK,4ASK,QPSK,2FSK,4FSK,8FSK,16QAM信号的分类。文献对高阶累积量的四阶、五阶累积量进行了优化和仿真,但是在低信噪比的环境下,对信号的识别率都不高。

在寻找更优识别算法的过程中,以往的研究更多的把注意力放在了识别算法上,而没注重算法的硬件设计与实现。System Generator for DSP是Xilinx公司开发的一款理想的DSP开发软件,它对数字信号处理单元进行系统建模,并将模型转换成可靠的硬件实现,是连接数字信号处理高层系统设计与Xilinx FPGA实现的桥梁。针对上述问题,本文提出了高阶累积量的改进算法,并在System Generator中实现了算法的FPGA设计。

1 高阶累积量的改进算法

数字信号的调制识别通常经过三个步骤:接收信号预处理、特征参数提取和调制方式识别。然而实现信号调制识别的关键环节是从接收信号中提取出用于识别的特征参数。下面首先介绍高阶累积量算法是如何提取用于调制识别的特征参数的。

1.1 特征参数的提取

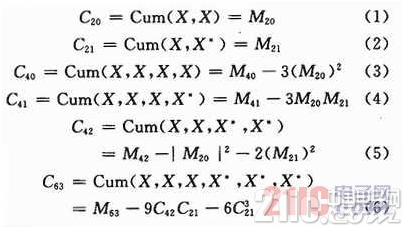

首先给出高阶矩的定义,对于一个具有零均值的复随机过程X(t),其p阶混合矩可表示为:Mpq=E[X(t)p-qX*(t)q]。其中,*表示函数的共轭。然后定义高阶累积量如下:

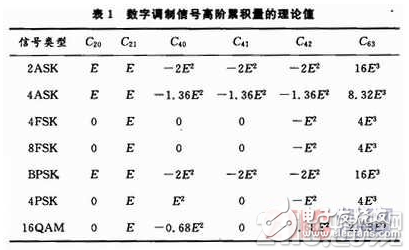

设信号的能量为E,利用文献中提出的算术平均来代替统计平均的方法,计算各种数字调制信号的高阶累积量,得到高阶累积量的理论值,如表1所示。

从表1中可以看出,从信号的高阶累积量中提取特征参数,可以实现大部分信号的分类,而由于2ASK和BPSK信号的各累积量值相同,故利用高阶累积量无法实现其分类。MFSK的高阶累积量也相同,直接利用累积量无法实现其类内识别。

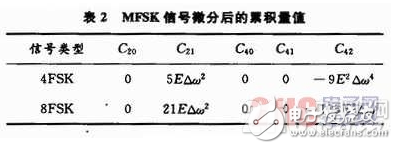

由文献知,对MFSK信号求导,再经中值滤波,在滤除含有冲激函数的项后,再计算所得信号的高阶累积量值,如表2所示。

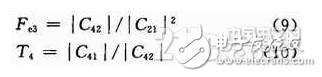

由以上分析可知,为了实现数字调制信号的调制识别,利用不同的累积量组合,从中提取了以下4个特征参数,定义如下:

1.2 信号的调制识别流程

在低信噪比环境中,基于高阶累积量的数字调制信号识别算法对2ASK和4ASK信号的识别率普遍较低。针对此问题,本文提出了高阶累积量的改进算法。文中在高阶累积量算法的基础上,对四个特征参数的判决顺序稍作调整,将MASK信号与其他信号分离,取得了较好的效果。具体识别过程如下:

(1)用编程工具编程产生各种数字调制信号,并加入信噪比已知的噪声,作为待识别的信号。

(2)将接收到的待识别信号通过下变频直接变换到零频,然后利用正交下变频技术得到复基带调制信号。

(3)计算各种待识别信号的二、四、六阶累积量,并计算其特征参数Fe1,Fe2,T4。

(4)利用特征参数T4的识别,可以将信号分为两组:第一组为MASK信号,第二组为MPSK,16QAM,MFSK信号。利用Fe2的阈值(t1)实现

第一组组内识别;再利用Fe2的另一个阈值(t2)和Fe1从第二组中识别出16QAM,MPSK信号。

(5)将待识别信号进行微分后再经中值滤波器,计算变换信号的高阶累积量,并计算特征参数Fe3,利用Fe2实现MFSK类内识别。

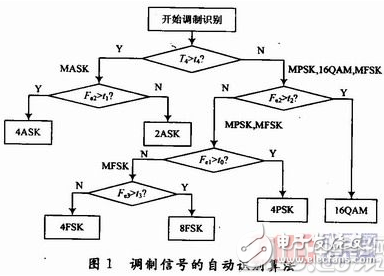

在信号的调制识别过程中,主要是根据决策树方法进行分类和识别。本文在提取上述四个特征参数的基础上,根据不同的决策规则建立决策树。经过多次性能的仿真和比较,最终得到一种比较好的识别算法,如图1所示。其中t0,t1,t2,t3,t4都是阈值。

1.3 仿真结果

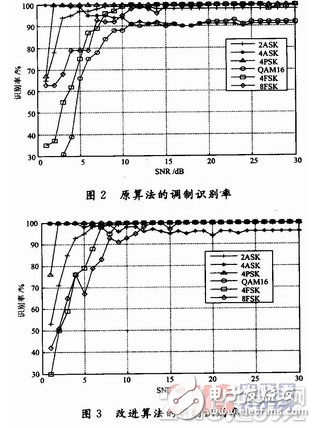

文中采用高阶累积量的改进方法,对算法识别性能做蒙特卡洛仿真。给阈值t0,t1,t2,t3,t4设置合适的值后,再将1 000次独立实验得到的仿真结果取平均。在每次试验中,设置信号的载波频率为12 kHz,码元速率为1 200 b/s,其中4FSK,8FSK的频偏分别为1.5 kHz,3.5 kHz,码元个数为200。图2为原算法仿真结果,图3为本文算法的仿真结果。

对图2和图3进行比较,可以看出本文算法的识别效果有了显著提高。在信噪比为2 dB时,本文算法对16QAM信号和4PSK信号识别率达到100%,而原算法几乎不能识别16QAM信号;在信噪比为4 dB时,对2ASK,4ASK信号的识别率分别为93%,100%。在信噪比为8 dB时,所有信号的识别率都可以达到90%以上,原算法有的信号识别率低于90%。比较后可知,在低信噪比环境下本文的算法对2ASK,4ASK,4PSK,16QAM信号的识别率有了显著提高。

2 算法的System Generator设计

目前,FPGA芯片已成为数字信号处理系统的核心器件。由于DSP设计者通常对C语言或Matlab工具很熟悉,却不了解硬件描述语言VHDL,使得FPGA并未在数字信号处理领域获得广泛应用。System Generator在很多方面扩展了MathWorks公司的Simulink平台,提供了适合硬件设计的数字信号处理建模环境,加速、简化了FPGA的DSP系统级硬件设计。通过Simulink的设计,System Generator即可自动完成硬件比特流的产生,从而高效的实现FPGA设计。

在FPGA调试和开发过程中,采用Xilinx公司的系统级建模工具System Generator构建信号调制识别的算法模块,开发板选用Virtex-4。算法模块主要由信号产生模块,信号参数提取模块和信号判决模块构成。

2.1 调制信号的产生

在System Generator设计过程中,各种调制信号是利用Matlab语言编程提供的,并叠加上已知信噪比的高斯白噪声。文中测试了2ASK,4ASK,4PSK,16QAM,4FSK和8FSK信号的识别率。

2.2 微分前参数提取模块

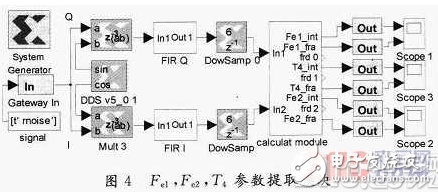

提取特征参数Fe1,Fe2,T4的模块,如图4所示。其中,signal是信号源,DDS,FIR,DowSamp共同实现复基带信号的同向分量和正交分量的提取,calculatmodule是计算Fe1,Fe2,T4三个特征参数的模块,且这三个特征参数的结果分别由三个示波器输出。

2.3 微分后参数提取模块

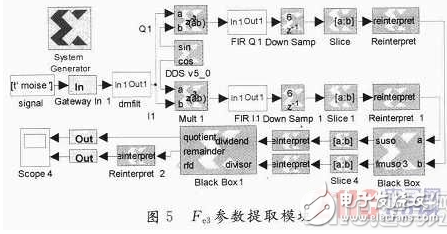

提取特征参数Fe3的模块,如图5所示。其中,dmfilt是微分中值滤波模块,两个Black Box是计算特征参数Fe3的模块。待识别调制信号经过dmfilt模块后,然后由DDS,FIR,DowSamp等提取同向分量和正交分量,再通过计算Fe3的模块计算参数,最后结果由Scope输出。

图6是当信号为4FSK时,计算得到的Fe3值。其中,O.03~O.1 s是模块计算参数的过程,O.1 s时对应的数据是计算的最终结果。将结果输出到Matlab变量空间workspace中,可以得到在0.1 s时计算的Fe3值为12.4。

3 实验结果

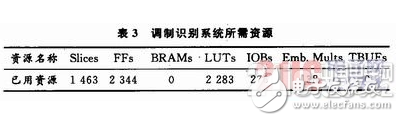

为了验证调制识别系统的可行性,分别在Simulink和目标开发板上运行该设计。在产生硬件协同仿真模块之前,先调用Resource Esti-mator模块对本系统所需资源进行估测。估测结果见表3。

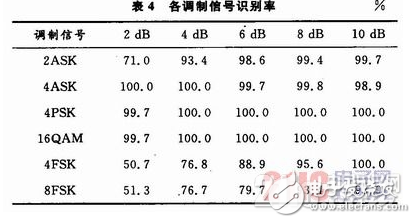

由于所需芯片内部资源较多,所以选用Virtex4-xc4vlx200芯片。然后在System Generator模块中点击Generate产生硬件协仿真模块,并将它拖入到设计文件当中。给Virtex-4目标板上电,连接好JTAG口,启动硬件协同仿真。当信号分别为2ASK,4ASK,4PSK等调制信号时,测试整个设计系统判决的结果,并将1 000次独立试验得到的仿真结果取平均,得到各种调制信号的识别率,如表4所示。从试验结果来看,调制识别系统设计的FPGA硬件协同实现与Simulink仿真的结果基本一致,达到了设计的要求,从而也说明了System Generator有很高的精度。

4 结语

本文采用高阶累积量改进算法对各种数字信号进行调制识别,大大提高了低信噪比环境下2ASK,4ASK,4PSK和16QAM信号的识别率,并在 System Generator中实现了高阶累积量改进算法的FPGA设计,从模型的建立到FPGA的实现都是在图形化设计环境下完成的,避开了编写复杂VHDL语言的环节,且转化到FPGA上实现的性能好,设计过程简便灵活,从而为调制方式识别算法的设计提供了一种新的方案。利用System Generator提供的图形化建模环境和自动转换成VHDL代码的能力,设计者可以将更多的时间和精力放在算法的优化上,同时又能显著缩短设计开发周期。

- 相关推荐

- FPGA

-

ISE 与matlab连接 问题 system generator for DSP simulink2013-10-05 0

-

altera与matlab是否有system generator做硬件协仿真?2015-01-14 0

-

System Generator中的PID控制器是如何设计的?2021-04-08 0

-

基于System Generator的Gardner算法设计2010-07-21 703

-

基于System Generator的数字下变频设计2013-01-10 1147

-

System Generator的设计实例2016-06-07 817

-

Xilinx System Generator大幅简化无线系统设计2017-02-09 288

-

System Generator实现串口通信(一行HDL代码都不用写)2017-02-10 2672

-

基于System Generator的FPGA开发总结2017-02-11 8206

-

FPGA开发之算法开发System Generator2017-11-17 7394

-

基于System Generator的Rife算法设计实现与仿真分析2017-11-18 2252

-

如何使用Vivado System Generator for DSP进行以太网硬件协同仿真2018-11-23 4315

-

基于System Generator for DSP工具实现FPGA系统的设计方案2020-09-24 1360

-

GPIO模拟UART的算法实现与设计方案2021-07-07 775

-

求一种FPGA实现图像去雾的实现设计方案2023-06-05 893

全部0条评论

快来发表一下你的评论吧 !