麦姆斯咨询:3D堆叠技术正成为图像传感器和高端IC应用的新标准

描述

微访谈:Xperi公司3D互联和封装研发副总裁Paul Enquist

凭借更高的性能、更低的功耗和更小的占位面积,3D堆叠技术正成为高端应用和成像应用的新标准。《2.5D/3D硅通孔(TSV)和晶圆级堆叠技术及市场-2019版》报告作者、Yole先进封装技术和市场分析师Mario Ibrahim,近日有幸采访了Xperi公司3D互联和封装研发副总裁Paul Enquist。

据麦姆斯咨询介绍,Xperi是一家上市高科技集团公司,旗下DTS、FotoNation、Invensas和Tessera四个子公司均在各自领域拥有领先的科技专利和超过20年的运营经验。其中,Tessera和Invensas是提供半导体封装和互联解决方案的先驱,采用其技术的芯片已经出货超过1000亿颗。

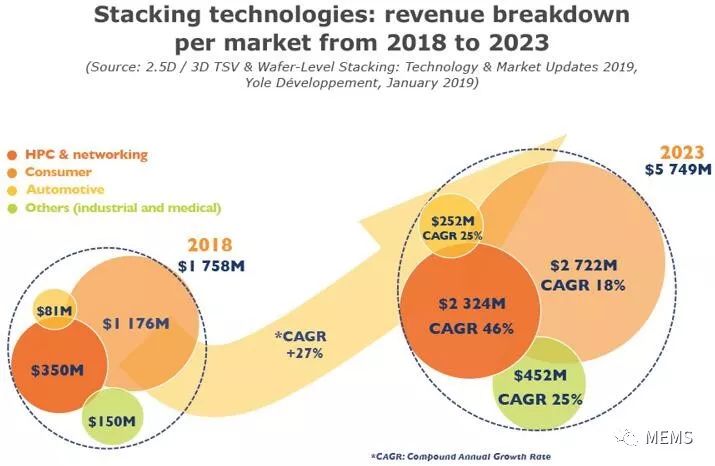

2018~2023年按市场细分的堆叠技术营收

数据来源:《2.5D/3D硅通孔(TSV)和晶圆级堆叠技术及市场-2019版》

混合键合技术包含直接堆叠的两片晶圆,这些晶圆具有平面绝缘表面和隔离的铜互联。混合键合已经在CMOS图像传感器(CIS)中取代了硅通孔(TSV)互联,在该应用中达到了占位面积、TSV成本缩减以及混合键合工艺成本之间的盈亏平衡点。它现在被三星、苹果和华为广泛用于高端智能手机的CIS。Xperi是一家技术开发和许可公司,为混合键合工艺的开发和应用做出了贡献,并为主要代工厂和集成器件制造商(IDM)提供DBI混合键合技术许可。

到2023年,80%的CIS制造将基于3D堆叠技术。混合堆叠CIS的市场份额将相应增长,预计2017~2023年期间的复合年增长率(CAGR)将超过43%。

消费类市场(主要是CIS应用),是2018年堆叠封装营收的最大贡献者,占据了65%以上的市场份额。尽管如此,高性能计算(HPC)是推动3D封装技术创新的主要应用,到2023年期间,该应用增长速度最快,市场份额预计将从2018年的20%增长到2023年的40%。

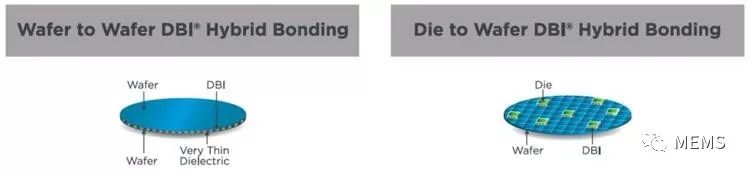

Yole在晶圆到晶圆(Wafer to Wafer,W2W)和芯片到晶圆(Die to Wafer,D2W),3D堆叠NAND,3D堆叠DRAM存储器和3D片上系统等领域看到了混合键合技术的进一步应用。

Mario Ibrahim(以下简称MI):作为一家技术开发和许可公司,您能否简要介绍一下Xperi及其商业模式?Xperi及其子公司展示了悠久的工艺开发历史,包括一些最早的使能型技术,如Shellcase、ZiBond和DBI技术。请您介绍一下Xperi即将商业化的新解决方案。你们是否在继续开发新的工艺?你们在和研究机构合作吗?

Paul Enquist(以下简称PE):Xperi及其子公司(DTS、FotoNation、Invensas和Tessera等)致力于打造创新的技术解决方案,为全球客户提供卓越的用户体验。Xperi的解决方案已许可给数百家全球领先的合作伙伴,并已出货数十亿量级的产品,包括优质音频、汽车、广播、计算成像、计算机视觉、移动计算和通信、内存、数据存储以及3D半导体互联和封装等应用领域。关于2.5D/3D技术解决方案,Xperi专注于Invensas ZiBond直接键合和DBI混合键合技术的开发和商业化,适用于各种半导体应用。我们和从材料供应商和设备供应商,到半导体制造商和代工厂,以及优秀研究机构(如Fraunhofer IZM-ASSID)等整个供应链展开合作。

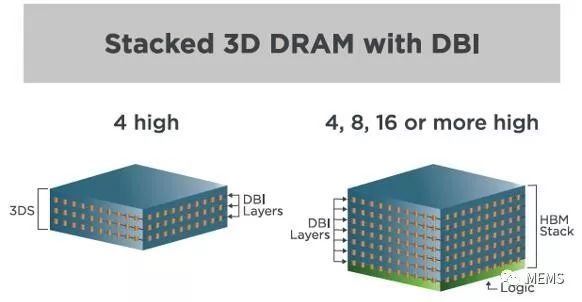

采用Xperi公司DBI技术的3D堆叠DRAM

MI:2.5D和3D堆叠技术被认为是摩尔定律放缓背景下最有希望的两种替代方案。预计2023年的堆叠(封装)营收将超过57亿美元。Xperi如何看待这些集成解决方案的未来?

PE:对于半导体封装行业来说,这是一段非常激动人心的时期。随着摩尔定律的放缓,通过缩小工艺节点以改善性能、功能、功耗和成本的历史规律大致走向尽头,业界越来越关注2.5D/3D堆叠和集成技术以满足市场需求。Invensas 2.5D和3D集成技术使半导体行业超越了摩尔定律。现在,通过Invensas ZiBond和DBI堆叠技术在背照式(BSI)图像传感器中的应用,已经可以看出这种转变。最近,这些技术已经在堆叠BSI图像传感器中实现了亚微米级像素扩展,以及光电二极管、逻辑和存储器的异构集成。我们相信,我们堆叠技术基本的成本和性能优势,将广泛传递至许多其他应用。例如,3D NAND和DRAM内存市场已准备好在不久的将来采用DBI混合键合技术。

MI:Xperi以授权ZiBond和DBI工艺而闻名,Xperi的主要细分市场和应用是什么?

PE:Xperi专注于进一步开发和商业化Invensas ZiBond直接键合和DBI混合键合技术,用于各种半导体应用,包括图像传感器、RF、MEMS、3D NAND、DRAM和2.5D和3D-IC配置的逻辑器件。最后,我们注意到DBI混合键合正在赋能一大波新半导体器件,从一开始就以3D思维重新设计,而不是简单地堆叠传统的2D架构。

ZiBond直接键合也已经在射频(RF)器件中应用,用于将CMOS开关从高RF损耗原生SOI衬底,转换到低RF损耗俘获感应硅或低RF损耗的非硅晶圆。随着5G的上市及其所提出的高要求,我们预计ZiBond直接键合技术的价值和适用性将在RF领域大幅增长。

MI:您如何看待从使用TSV的ZiBond到DBI的过渡?您是否看到这些工艺的进一步应用?

PE:多年来,ZiBond和DBI都被用于制造BSI图像传感器。刚开始ZiBond用于在硅处理晶圆或在具有TSV互联的CMOS逻辑晶圆上堆叠光电探测器晶圆。在光电探测器晶圆堆叠之前,TSV还与ZiBond一起用于CMOS逻辑器件与存储器晶圆的堆叠和电气互联。使用DBI替代ZiBond进行堆叠,已经证明通过简单的焊盘切割替换TSV,可以非常有效地进一步缩小芯片并节省工艺成本。我们预计将看到向DBI混合键合的持续过渡,尤其是在图像传感器领域,因为行业需要像素到像素级互联。也就是说,我们预计ZiBond和DBI将在未来多年内持续共存。

MI:2018年末,Xperi宣布与三星达成了新的专利许可协议。Yole预计在基于DRAM的3D堆叠存储器中将使用混合键合技术。这是否会为混合键合技术在高带宽存储(HBM)和3D堆叠DRAM市场打开大门?

PE:我们非常高兴与三星达成协议,并期待在未来几年实现互利关系。

关于在HBM和3D堆叠DRAM中使用Invensas DBI混合键合,我们认为这是一种出色的解决方案,特别是在D2W配置中,因为它可以实现更低的电寄生效应,更低的热阻抗,在JEDEC(电子器件工程联合委员会)高度限制内实现更多堆叠的芯片,以及与热压键合相比减少键合周期。此外,DBI混合键合本身可以在低温下进行,并且不需要底部填充,这是相比替代键合方案的显著优势。我们正积极与客户合作,展示这些优势,并期待近、中期的商业化产品。

我们还将3D NAND视为W2W DBI混合键合的重要机遇。微米级DBI互联可以支持将I/O和存储器单元构建在单独的晶圆上实现独立优化的工艺节点,然后堆叠,从而实现显著的性能、密度和成本优势。这是我们具有近、中期商业化潜力的另一个重要业务。

W2W和D2W DBI混合键合晶圆示意图

MI:除了三星之外,一家总部位于中国的新存储厂商长江存储(YMTC),在2018年底发布了其Xtacking技术(不使用TSV)。DBI和W2W组装工艺是否与NAND晶圆兼容?Xperi在不断增长的中国存储市场的计划是什么?会很快商业化吗?

PE:Invensas DBI技术兼容DRAM和NAND晶圆。Invensas DBI键合工艺的热预算可以限制在150℃,这为广泛的应用打开了大门。

就中国而言,“中国制造2025”计划正在推动中国对先进半导体技术的需求。因此,我们认为即将兴起的中国半导体制造商和代工厂,代表了ZiBond和DBI等3D集成技术的重要机遇。我们正在这个快速增长的市场与各类厂商合作,期待很快将有产品商业化。

MI:在低温键合中加入的缩放和低间距技术是混合键合的一些优点。所需的极低表面粗糙度可能是该技术的难点/缺点。您能否详细介绍一下混合键合技术的优缺点?

PE:与其他技术相比,缩放互联间距是DBI技术的一个基本优势。虽然Invensas ZiBond直接键合和DBI混合键合在表面粗糙度和表面清洁度方面具有严苛的要求,但行业标准的亚微米特征尺寸“大马士革”(Damascene)工艺和洁净室环境,已被用于多代CMOS工艺节点后端工艺的多级互联堆叠,已被证明能够满足这些技术的要求,已经出货数十亿颗的BSI图像传感器便是有力证明。

MI:工艺改进的下一步是什么?

PE:我们不断参与自己内部和客户的工艺改进,以满足特定应用中出现的特定需求。过去几年的一个重点领域是D2W DBI混合键合,我们认为这对于DRAM和异构逻辑器件和存储器集成应用非常重要。我们的研究重点是优化切割、清洁和高通量芯片键合,已经取得了显著进展。我们对这种特定方案的前景及其对半导体行业的影响感到非常兴奋。

MI:由于更小的特征尺寸,W2W对准精度要求更高。目前在HVM应用中可行的精度是多少,未来几年的路线图将如何发展?

PE:目前量产的晶圆键合设备能够达到+/- 250nm的对准精度,3 sigma,并且在HVM中支持3.7um间距DBI混合键合。设备供应商表示,他们的路线图中有100nm甚至50nm,3 sigma对准能力,我们很期待到时利用这种性能。

MI:高端细分领域的先进封装正变得多样化,包括各种采用或不采用TSV的先进封装技术,其中包括英特尔的Foveros和EMIB、三星的RDL技术、Chip-on-Wafer-on-Substrate(CoWoS)、台积电的基板上的3D SoC和集成扇出型封装(InFO),以及安靠(Amkor)的SWIFT等技术。您是否认为它们是现有TSV和W2W技术的真正挑战者?Xperi如何看待这些技术?Xperi会支持这些技术吗?

PE:我们预计会有各种各样的封装技术可供选择,因为市场和应用需求变化很大。现实情况是,行业需要一种包含各种封装和互联解决方案的工具集,可以从中选择以解决市场不断变化的需求。虽然,随着应用的成熟,可能会对这些解决方案进行一些整合,但我们预计各种封装和互联解决方案将在未来几年共存。需要注意的是,这些技术中的一些是互补关系,而不是竞争关系。例如,DBI混合键合是一种多功能互联解决方案,可与各种2.5D和3D封装组装技术结合使用。

MI:Yole认为,随着台积电作为代工厂,3D SoC技术将在2019年进入市场。混合键合作为所使用的互联技术处于有利位置。你们的技术是否适用于逻辑W2W或D2W堆叠的存储?

PE:W2W和D2W方案中的Invensas ZiBond直接键合和DBI混合键合技术,都适用于逻辑堆叠应用中的3D SoC和存储器。早期的一个例子还是图像传感器市场,其中存储已经与三层堆叠图像传感器中的逻辑堆叠,ZiBond直接键合提供了机械键合,TSV提供了电气互联。DBI混合键合也已经可以用于实现这种类型的集成。我们目前重点关注的3D堆叠DRAM的D2W研究,实际上与3D SoC直接相关。

DBI混合键合为3D SoC提供的令人兴奋的功能,是能够以与芯片内互联间距相媲美的间距,连接堆叠中的每个芯片。这可以消除I/O接口,实现芯片间与芯片内互联相当的芯片级互联。这对功耗、占位面积和金属层减少具有积极意义。实现这种新设计方案的一个挑战是改变设计过程中的2D思维。以3D堆叠结构设计器件是一种架构模式的转变,利用DBI混合键合可以实现很多3D SoC优势。

MI:显示和增强现实/虚拟现实/混合现实(AR/VR/MR)市场需要高互联密度来连接显示器及其驱动,混合键合技术是否与这些市场和应用兼容?

PE:Invensas DBI混合键合也非常适合显示和AR/VR/MR市场。这些市场的常见应用是在逻辑驱动阵列层上堆叠光学发射器阵列层,这类似于在图像传感器应用的逻辑读出阵列层上堆叠光学探测器阵列层。DBI混合键合可以支持低至1um的互联间距,这些应用可能需要使用当前或即将推出的新设备。此外,这些光学发射器市场通常需要非硅发射器材料,例如GaN,这类材料具有与硅显著不同的热膨胀系数。这可以通过DBI混合键合工艺的低热预算来实现,这与其他具有较高热预算的键合技术不同,这些技术无法满足这些市场和应用的需求。

MI:W2W组装以及混合键合是纯代工业务,抢夺了外包半导体封测厂商(OSAT)先进封装业务的营收。您是否看到OSAT厂商尝试在这个领域重新寻求市场定位?

PE:Invensas DBI混合键合的低拥有成本和高附加值,使其成为有意提高利润并扩大供应能力的OSAT厂商的理想候选技术。尤其是D2W DBI混合键合技术即将商业化,为OSAT利用其高度相关的芯片处理经验和专业知识提供了机遇。

关于Xperi

Xperi公司以及旗下全资子公司DTS、FotoNation、Invensas 及 Tessera致力于打造各种创新技术方案,为全球消费者呈现独一无二的体验。数百家全球领先的合作伙伴获得了Xperi解决方案的授权,数十亿件授权产品遍布全球,产品范围涵盖音频、广播、计算成像、计算机视觉、移动计算和通讯、存储、数据储存、3D半导体互联和封装等领域。

-

PCB分层堆叠在控制EMI辐射中的作用和设计技巧2013-08-28 0

-

赛普拉斯900万像素CMOS图像传感器面向高端相机2018-10-24 0

-

IBM将提供CMOS图像传感器代工服务2018-11-20 0

-

赛普拉斯面向高端数码相机的900万像素APS CMOS图像传感器2018-11-20 0

-

赛普拉斯手持终端用CMOS图像传感器方案2018-11-20 0

-

3D传感器如何为车内安全保驾护航?2020-07-29 0

-

超声波传感器应用的创新及发展2020-08-06 0

-

MEMS气压传感器在物联网中的应用有哪些2020-08-07 0

-

3D传感器在环境感知、捕捉方面的作用2020-08-10 0

-

传感器植入技术或将实现体内GPS定位2020-08-17 0

-

控制和通信IC对机器人发展起到重要作用2020-08-18 0

-

3D传感器有哪些类型2020-12-09 0

-

AR0237IR图像传感器推动3D成像技术的发展2020-12-16 0

-

3D图像的主流技术有哪几种?2021-05-28 0

-

3D线激光位移传感器专业应用于工业“机器视觉”2022-04-21 0

全部0条评论

快来发表一下你的评论吧 !