怎样优化PLL环路来达到理想的相位噪声和抖动

描述

可以使用许多工具来优化PLL环路。 ADIsimCLK是用于ADI时钟部件的好工具。优化相位噪声和抖动不一定是一回事。

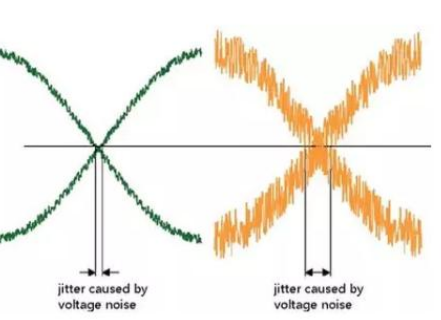

如果在给定的偏移频率下有一个相位噪声规范,那么应该将VCO和参考相位噪声信息提供给工具,例如ADIsimCLK,并使用它来优化闭环带宽实现预期目标。该过程实质上是调整闭环带宽以折衷参考和VCO相位噪声。

如果有一个具有抖动规格,则应调整闭环带宽以实现最低抖动,这可能不一定对应于所有偏移频率的最低相位噪声。

例如,虽然可以通过扩展闭环带宽来实现低近距相位噪声,但由此产生的抖动可能大于可能的最小抖动,因为环路跟踪参考的次数超过了是最佳抖动所必需的。可以通过降低闭环带宽来实现更低的抖动,允许PLL在较低的偏移频率下跟踪VCO,即使得到的相位噪声图可能在闭环带宽偏移频率处显示更多的峰值。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

怎样将相位噪声和抖动降至最低及其估算方法2009-10-13 0

-

选择环路带宽涉及抖动、相位噪声、锁定时间或杂散问题2018-08-29 0

-

相位噪声的RMS抖动2018-10-10 0

-

怎么将相位噪声转换为抖动?2019-08-13 0

-

双环路时钟发生器可清除抖动并提供多个高频输出2019-10-31 0

-

低相位噪声&抖动2020-06-10 0

-

如何区分抖动和相位噪声?2021-03-11 0

-

测量较低时钟频率的相位噪声和相位抖动2021-06-24 0

-

发现抖动、相位噪声、锁定时间或杂散问题怎么解决2022-11-16 0

-

CDCE72010抖动清理器和同步器PLL器件上获取的相位噪声数据的资料概述2018-05-15 953

-

发现相位噪声、锁定时间或杂散问题请检查锁相环的环路滤波器带宽2022-01-11 2209

-

发现抖动、相位噪声、锁定时间或杂散问题?请检查锁相环的环路滤波器带宽2022-11-02 361

-

相位噪声到抖动的转换(下)2023-10-30 1351

-

相位噪声与时间抖动有何关系?如何测试时间抖动?2024-01-31 221

全部0条评论

快来发表一下你的评论吧 !