CPLD与FPGA的区别对比概述

可编程逻辑

描述

PLD(Programmable Logic Device):可编程逻辑器件,数字集成电路半成品,芯片上按照一定的排列方式集成了大量的门和触发器等基本逻辑元件,使用者按照设计要求运用开发工具将这些片内的元件连接起来,此过程称为编程;

FPGA:基于查找表技术,要外挂配置用的EEPROM的PLD产品;由逻辑功能块排列为阵列,并由可编程的内部连线连接这些功能块。

CPLD(复杂可编程逻辑器件 Complex Programmable Logic Device):基于乘积项技术,不需要外挂配置用的PLD产品。由可编程的与门,或门阵列以及宏单元构成。与门,或门阵列可以重新编程,实现多种逻辑功能。宏单元则可以实现组合,时序逻辑功能模块。

2.CPLD与FPGA的结构

CPLD一个基本单元(宏单元)就可以分解十几个甚至20,30多个组合逻辑输入,而FPGA的一个基本单元(LUT)只能处理4输入的组合逻辑,由此看来,CPLD适合用于设计译码等复杂的组合逻辑电路。

FPGA中包含的基本单元和触发器数量很多,成千上万,而CPLD一般只能做到512个逻辑单元。因此,在设计中使用到大量触发器,如设计一个复杂的时序逻辑电路,那么就应该用FPGA。

3.CPLD的工作原理

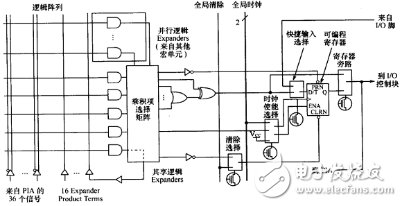

CPLD是基于乘积项的,此种CPLD的结构主要包括宏单元,可编程的连线(PIA)和I/O控制模块,基本逻辑功能就是由宏单元来实现的。

PIA则起到复杂信号传递,连接所有宏单元的作用,I/O控制块负责输入输出的电气特性控制。INPUT/GCLK1,INPUT/GCLRn,INPUT/OE1,INPUT/OE2是全局时钟,清零和输出使能信号,这些信号有专用连线与CPLD中每个宏单元相连。

CPLD器件结构图

CPLD的宏单元左侧是乘积项阵列,即“与或”阵列,每个交叉点都是一个可编程熔丝,如果导通就实现“与”逻辑,后面的乘积项选择矩阵是一个“或”阵列,两者一起实现组合逻辑。最右侧是一个可编程的D触发器,它的时钟,清零输入都可以编程选择。

CPLD宏单元图

4.FPGA的工作原理

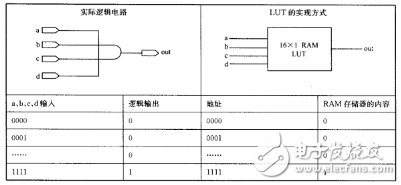

FPGA是基于查找表的原理与结构,查找表简称LUT(Look-Up-Table),本质上就是一个RAM(掉电不保存数据),目前使用最多的是4输入LUT,用户通过原理图或硬件描述语言描述了一个逻辑电路以后,FPGA开发软件会自动计算逻辑电路的所有可能的结果,并把结果事先写入RAM,这样,每输入一个信号进行逻辑运算就等于输入一个地址进行查表,找出地址对应的内容,然后输出即可。

4输入与门实现逻辑电路和LUT的实现方式

-

FPGA与CPLD的区别2011-09-27 0

-

CPLD和FPGA的区别是什么?2013-07-25 0

-

FPGA与CPLD的概念及其区别PDF2018-08-15 0

-

CPLD与FPGA对比分析哪个好?2021-06-21 0

-

FPGA与CPLD的区别是什么2021-09-22 0

-

DSP/MCU/ARM/CPLD/FPGA对比分析哪个好?2021-10-22 0

-

CPLD与FPGA的对比分析哪个好?2021-11-05 0

-

cpld fpga 区别2008-01-15 5430

-

EDA(CPLD/FPGA)技术概述2008-09-24 2456

-

oled与tft的区别对比2012-02-03 29260

-

FPGA/CPLD的设计思想2016-02-17 635

-

CPLD和FPGA的区别2016-02-19 519

-

关于CPLD和FPGA的区别2017-09-18 858

-

CPLD和FPGA两者的区别2018-05-24 49566

全部0条评论

快来发表一下你的评论吧 !