一个看起来简单但又让人极为痛苦的器件一一比较器

描述

比较器,是一个看起来简单但又让人极为痛苦的器件。如果你是刚学模拟电子技术的学生,那么在初次使用它时,不仅会被其诡异的表现难住,还将百思不得其解:如此简单的比较器,怎么就这般不听话呢?

《新概念模拟电路》系列丛书之《信号处理电路》一本书中这样说:

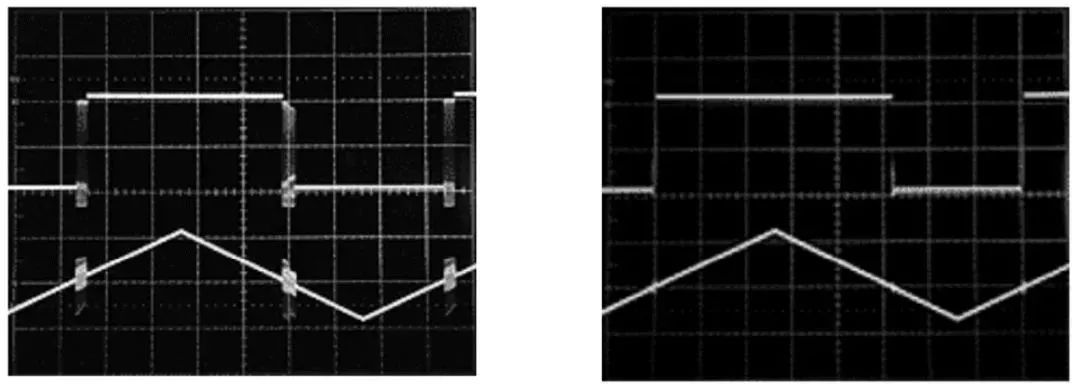

其实,比较器最常见的诡异现象就是翻转抖动。以一个基准电压为0V,输入信号为从-1V到1V的三角波为例,当输入信号穿越基准电压点时,理论上:输出信号应该立即翻转,干脆利索,且输入信号应该不受任何影响。但实际情况如图1左图所示:输出信号在翻转位置出现了多次抖动,然后才归于平静,然后,输入信号居然也出现了抖动毛刺。

图1 比较器的翻转抖动及克服抖动带来的效果

造成这种现象的原因很多,电源稳定性和地线稳定性不强是主要原因。其本质原理是,比较器的输出端突然发生状态变化时,会导致内部工作电流发生脉冲式突变,这个变化电流作用在电源电压上,会导致电源电压出现脉动;作用在地线上,会导致地线电位出现脉动。这种脉动带来的直接后果就是,比较器的输入状态发生变化:原本输入信号已经高于基准电压,却因为地线脉动的存在,出现瞬间的输入信号低于基准电压,比较器出现误翻转。这种误翻转持续作用,就会出现翻转抖动。

翻转抖动的存在,一定是输入信号在处于基准电压附近时发生。当输入电压持续增大,以至于地线抖动不足以改变比较器的输入状态时,那么输出就归于平静了。

克服翻转抖动的本质方法是加强电源和地线的稳定性——想尽一切办法让电源和地线接近理论要求:不管电源、地线上流过多大电流,其电压都是恒定不变的。比如加粗电源线(地线)、缩短电源线(地线)长度,增加合适的电源旁路、去耦电容,使用高质量的地平面,或者将数字地和模拟地分开且实现单点对接。

克服翻转抖动的另外一种方法,就是给比较器增加迟滞:用正反馈将原本开环的比较器,改变成迟滞比较器。图1右图,即为增加了迟滞后的波形,可见其翻转抖动几乎不存在了。

五大规则,破除“诡异现象”

相对来说,高速比较器更易出现各种各样的诡异现象。因此,我们在设计之初就必须牢记以下五大规则,以最大程度地避免诡异现象。

01给比较器电路增加合适的旁路电容

在器件电源管脚的最近处,对地接一个或者两个电容,以避免突变电流在漫长的电源线上——含有电阻和电感——产生的突变压降。

02让比较器电路使用地平面

由于地平面具有极大的面积,直接带来的好处有两点:第一,它具有极低的导通电阻,可以在通过大电流时保持地平面上任意两点之间的电位差足够小,以利于“地”与理论接近。第二,它还具有极低的电感,对高频电流,也不会产生足够大的压降。

03用高速布线技术实施PCB设计

高速布线技术有别于低速,关键在于考虑了杂散参数。在低频领域,电路板中的两个隔离线,具有足够大的电阻,但在高速领域,它们之间的杂散电容就会起作用。同时,长长的导线存在的电感,也会跳出来破坏正常的工作。因此,走线、位置、间距、方向、粗细、长短、过孔等,都将对高速电路产生不可忽视的影响。此事说来话长,要设计高速比较器电路,必须认真研读相关资料。

04使用合适的探头、示波器

如果要观察比较器输入输出状态,则一定要注意:探头和示波器不是理想的,它们会影响电路的正常工作。

05注意降低信号源内阻

高速比较器接收的是高速信号,因此它非常惧怕低通滤波器。信号源电阻,也就是前级信号的输出电阻,会与比较器输入端电容组成低通滤波器。提高此低通滤波器上限截止频率,是唯一的解决方案。而要如此,则有两条路:第一,降低前级信号源的输出电阻,第二,降低比较器输入端的等效输入电容。

一般来说,比较器入端等效电容主要由比较器芯片性能决定,也受线路与周边“地”之间的杂散电容影响。当选择了输入端电容最小的比较器,又通过优秀的电路板设计,将杂散电容降至最小,此时应重点考虑降低前级信号源内阻。

-

VI上写的程序运行起来的时候前面板看起来是透明或半透明...2012-08-11 0

-

为什么PCB看起来是黑色的?2017-07-22 0

-

UART输出看起来反转了2018-09-20 0

-

SOLT原始数据看起来不对2018-10-10 0

-

第一次画板看起来比较密集2019-03-06 0

-

为什么Altium里会有这种看起来透明的线?2019-07-12 0

-

比较器振荡的原因2019-07-23 0

-

为什么Allegro这个阻抗顶层看起来比内层要厚但参数显示是一样的?2019-09-06 0

-

救救孩子吧,这个电路看起来好奇怪啊2020-03-17 0

-

请问如何实现一个I2C从设备看起来像一个内存?2022-12-12 0

-

想让你的iOS 10看起来与众不同?可以试试越狱后这样做2017-03-06 1247

-

隔天测量的结果看起来不同,怎么回事?2019-01-19 3470

-

看起来像字母H的H桥开源2022-08-19 231

-

快乐解说MCU:为什么说有些芯片看起来像MCU,但是我们不认为是2023-09-18 234

全部0条评论

快来发表一下你的评论吧 !