锁存器Lacth & 触发器Flip-flop就是实现储存功能的两种逻辑单元电路

电子说

描述

大多数数字系统中,除了需要具有逻辑运算和算术运算功能的组合逻辑电路外,还需要具有储存功能的电路,组合逻辑电路和储存电路相结合可构成时序逻辑电路,锁存器Lacth & 触发器Flip-flop就是实现储存功能的两种逻辑单元电路。

锁存器是对电平敏感的电路,它们在一定电平作用下改变状态。基本SR锁存器由输入信号电平直接控制其状态,传输门控或逻辑门控锁存器在使能电平作用下由输入信号决定其状态。在使能信号作用期间,门控锁存器输出跟随输入信号变化而变化。

触发器则是对时钟脉冲边沿敏感的电路,根据不同的电路结构,它们在时钟脉冲的上升沿或下降沿作用下改变状态。目前流行的触发器电路主要有主从、维持阻塞和利用传输延迟等几种结构,它们的工作原理个不相同。

触发器按逻辑功能分类有D触发器、JK触发器、T触发器和SR触发器。它们的功能可用特性表、特性方程和状态图来描述。触发器的电路结构与逻辑功能没有必然联系。例如JK触发器既有主从结构也有维持阻塞或利用传输延迟结构。每一种逻辑功能的触发器都可以通过增加门电路和适当的外部连线转换为其它功能的触发器。

之所以能够有记忆功能能够存储信息,最主要的就是它把输出有反馈到了输入,形成了反馈这样它就能保持稳定。这使得Lacth & Flip-flop与组合逻辑电路的分析有了很大的不同,当然Latch & Flip-flop本来就只有这么几种,记住就行。不需要自己去创新。

从最基本的用两个或非门构成的SR锁存器到在前面加上两个与门和一个使能端E的逻辑门控SR锁存器,这样就可以实现多个锁存器同步进行数据锁存。但是SR锁存器有个很不好的地方就是当SR同时为1的时候,它会出现不确定状态,解决这个问题其实也很简单在逻辑门SR锁存器的S和R之间串上一个非门这样S和R永远都不会一样,当然同时为0的状态时有使能端E决定的,这个就是D锁存器,当E为1时,输出Q = D;当E为0时,输出Q保持之前的状态不变。再讲了传输门门控D锁存器,大致工作原理是当E为1的时候,放输入信号进来,当E为0时,锁存前一时刻(E=1时)的数据,后来就提出了在时序图中的几个基本概念:建立时间(Tsu)、保持时间(Th)、脉冲宽度(Tw)和传输延迟时间()。

触发器的电路结构就不仔细分析了,关键是看看几种触发器的逻辑功能,触发器在每次时钟脉冲触发沿到来之前的状态称为现态,而在此之后的状态称为次态。所谓触发器的逻辑功能,是指次态与现态、输入信号之间的逻辑关系。

D触发器功能比较简单,输出Q的值直接等于输入D就行。JK触发器由特性表,特性方程或状态图都可以看出,当J=1,K=0时,触发器的下一个状态被置1;当J=0,K=1时,将被置0;当J=K=0时,触发器状态保持不变;当J=K=1时,触发器翻转。在所有类型的触发器中JK触发器具有最强的逻辑功能,它能执行置1、置0、保持和翻转四种操作,并可以简单的附加电路转换为其他功能的触发器,因此在数字电路中被广泛应用。在某些场合,需要对计数功能进行控制,当控制信号T=1时,每来一个CP脉冲,它的状态翻转一次;而当T=0时,则不对CP信号做出响应而保持状态不变。这就是T触发器。其实T触发器很简单就是把JK触发器的JK两端接在了一起。仅有置位、复位功能的触发器称为SR触发器,并且还有约束条件SR=0。

各种触发器之间是可以很轻松的相互转换的,要会灵活应用。

锁存器能根据输入端把结果自行保持;触发器是指由时钟边沿触发的存储器单元;由敏感信号(电平,边沿)控制的锁存器就是触发器;

写电路时,产生锁存器的原因:

if语句中,没有写else,默认保持原值,产生锁存器,可能不是想要的结果;

case语句中,没有写完整default项,也容易产生锁存器;

例子:

always@(a or b)

begin

if(a) q=b;

end

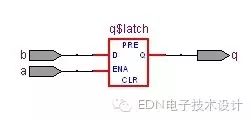

产生了锁存器,如下

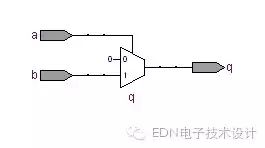

没有锁存器的情况

always@(a or b)

begin

if(a) q=b;

else q=0;

end

避免使用D锁存器,尽量使用D触发器

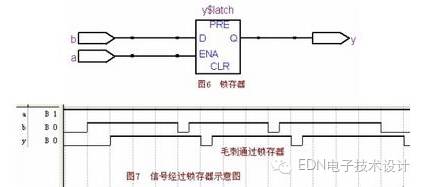

D锁存器

module test_latch(y, a, b);

output y; input a; input b; reg y;

always @(a or b) begin

if(a==1’b1)

y=b;

end endmodule

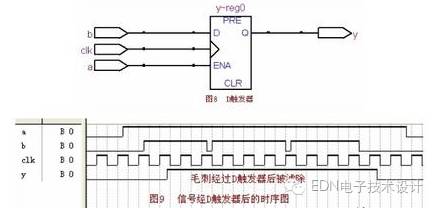

D触发器

module test_d(y,clk,a,b);

output y; input clk; input a; input b; reg y; always @(posedge clk) begin if(a==1'b1)

y=b;

end endmodule

从图8可知,例10对应的电路是D触发器。信号a被综合成D触发器的使能端,只有在时钟上沿到来且a为高时,b信号的值才能传递给a;只要在时钟上升沿期间信号b是稳定,即使在其他时候b还有毛刺,经过D触发器后数据是稳定的,毛刺被滤除。

-

锁存器、触发器、寄存器和缓冲器的区别2011-10-09 0

-

凔海笔记之FPGA(六):触发器和锁存器2016-05-21 0

-

寄存器、锁存器和触发器的区别2018-07-03 0

-

触发器、锁存器、寄存器三者的区别2018-09-11 0

-

【转】数字电路三剑客:锁存器、触发器和寄存器2018-10-27 0

-

浅析触发器2019-06-20 0

-

什么是触发器 触发器的工作原理及作用2019-12-25 0

-

FPGA从入门到精通——时序电路之触发器2021-07-04 0

-

嵌入式硬件(三)数字逻辑电路 精选资料推荐2021-07-26 0

-

数字电子技术基础5——锁存器与触发器 精选资料推荐2021-07-30 0

-

锁存器与触发器的工作原理是什么2021-11-03 0

-

锁存器和触发器2022-03-10 0

-

怎么用NICE接口读取FPGA上FLIP-FLOP中的数据?2023-08-16 0

-

锁存器Latch和触发器Flip-flop有何区别2018-04-18 130196

全部0条评论

快来发表一下你的评论吧 !