扒一扒DDR4的新功能和PCB设计上的一些注意事项

电子说

描述

DDR4新增了许多功能,这对于我们之前信手拈来的内存PCB设计又带来了一些新的挑战,虽然说之前的一些规范可以用,但还是有很多不一样的地方,如果依然按照之前的设计方法来做,说明你还不了解DDR4,一准入坑。今天咱们就来扒一扒它的新功能和PCB设计上的一些注意事项。

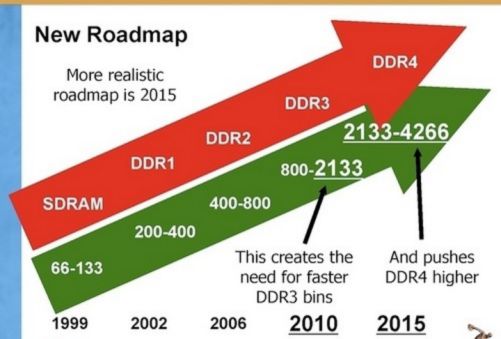

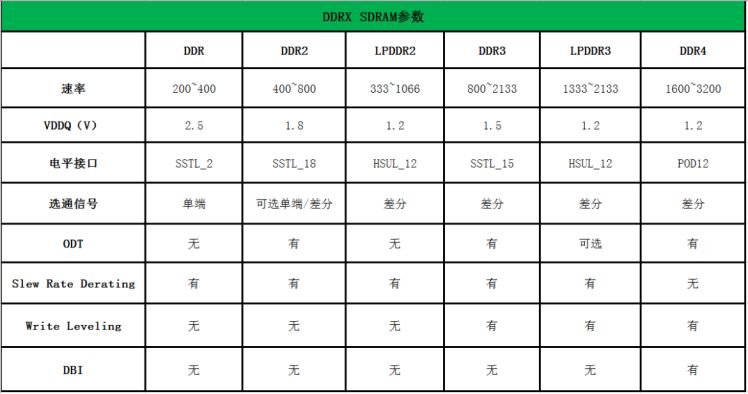

DDRX发展趋势及参数对比

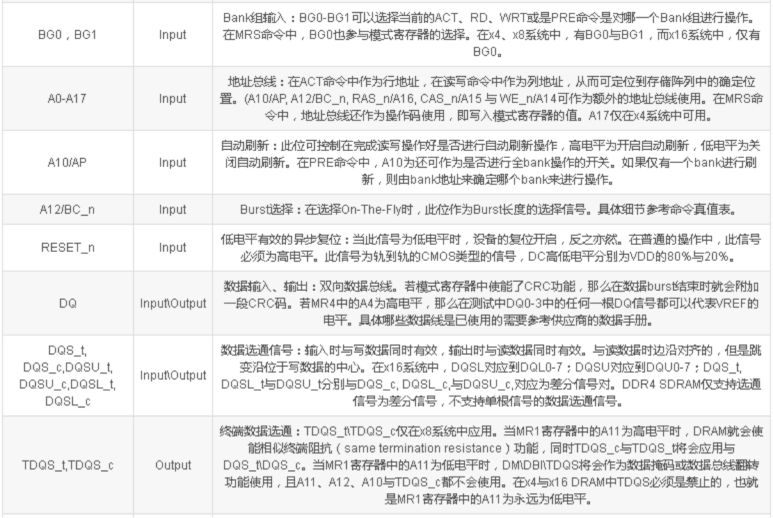

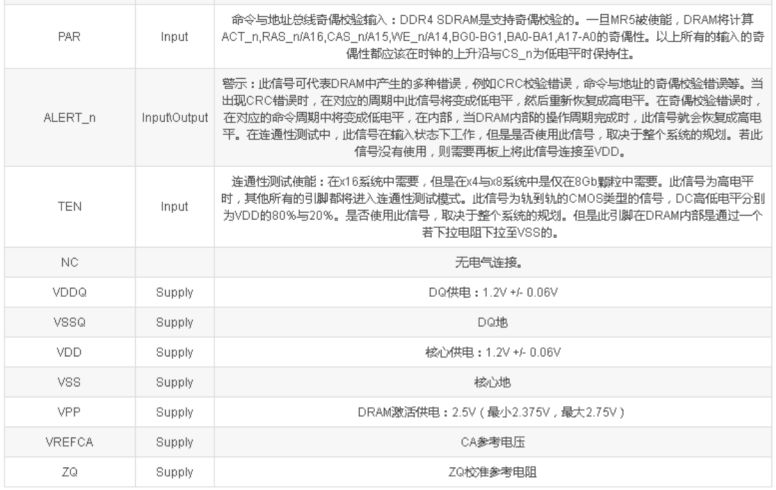

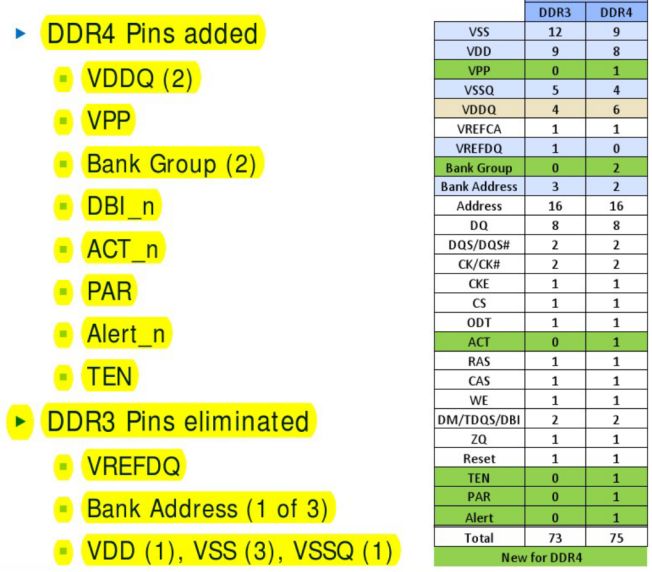

DDR4信号引脚功能

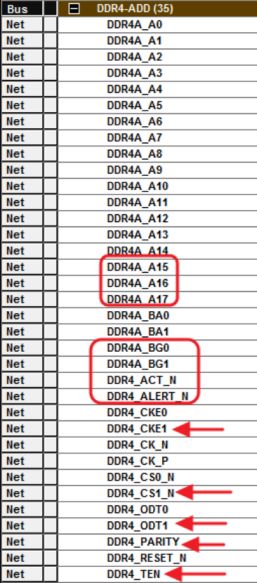

DDR4新增pin

DDR4新增功能

(1)新的JEDEC POD12接口标准(工作电压1.2V) ;

(2)DBI:可以降低功耗并且提升数据信号完整性;

(3)Bank群组结构:是个8n预取群组结构,它可以使用两个或者四个Bank组,这允许DDR4内存在每个Bank群组单独被激活、读取、写入或刷新操作,这样可以带来更高的内存速度和带宽;

(4)取消了Derating,时序仿真计算不再繁琐;

(5)DQ动态确定Vref ( V_ center ) ,增加了眼图要求;

(5)新的终止调度:在DDR4中DQ bus可以转移终止到VDDQ ,这样即使VDD电压降低的情况下也能保证稳定;

(6)新的数据总线CRC技术,可以进行传输过程中的错误侦测,特别对非ECC内存进行写入操作时有帮助;

(7)针对命令和地址总线的新的CA奇偶校验;突发长度和突发停止长度分别为8和4 ;

(8)正常和动态的ODT :改进ODT协议,并且采用新的Park Mode模式可以允许正常终结和动态吸入终结,而不需要去驱动ODT Pin

(9)Differential Signaling(差分信号技术)

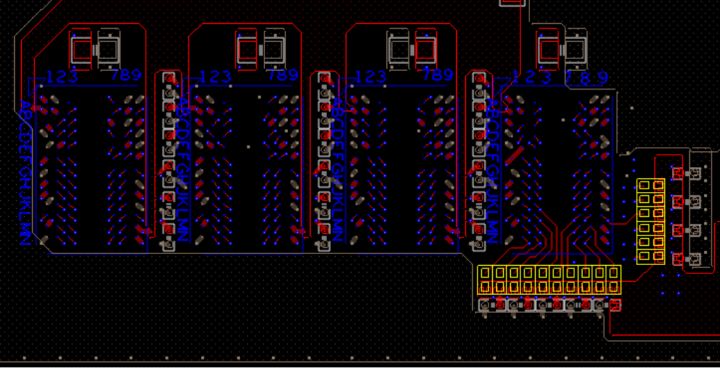

信号分组

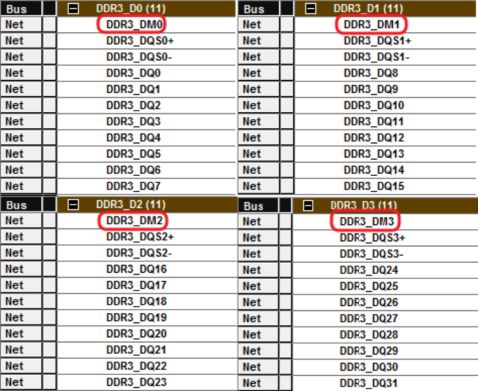

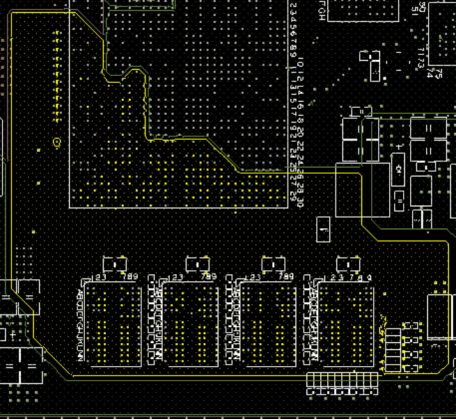

DDR3数据信号的分组

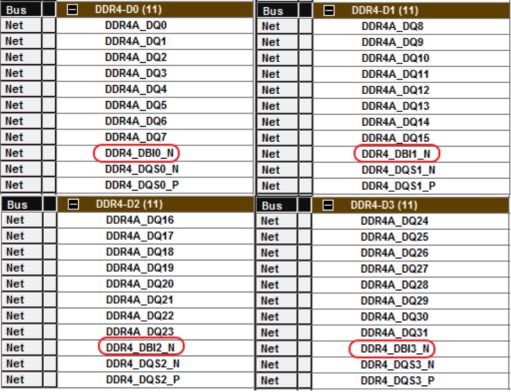

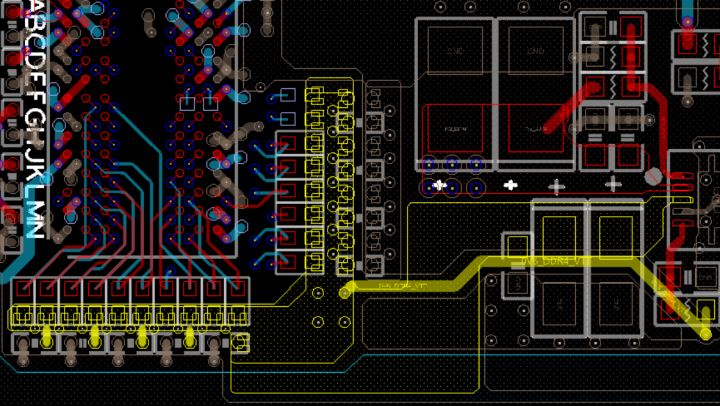

DDR4数据信号的分组

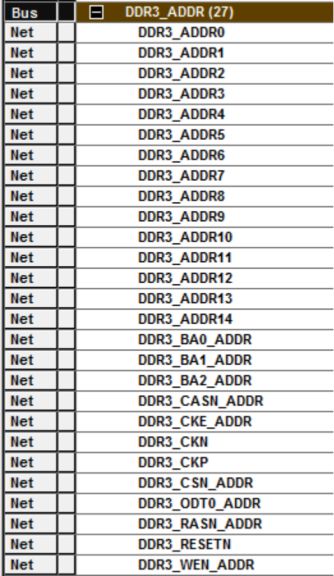

DDR3地址信号的分组

DDR4地址信号的分组

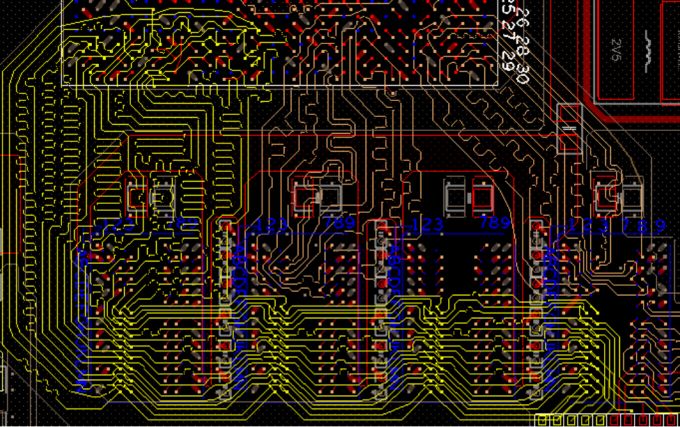

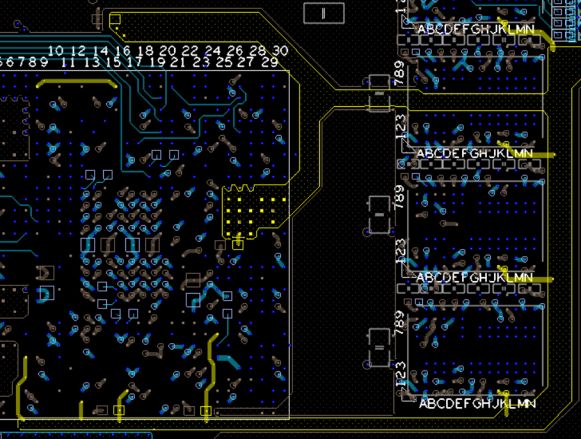

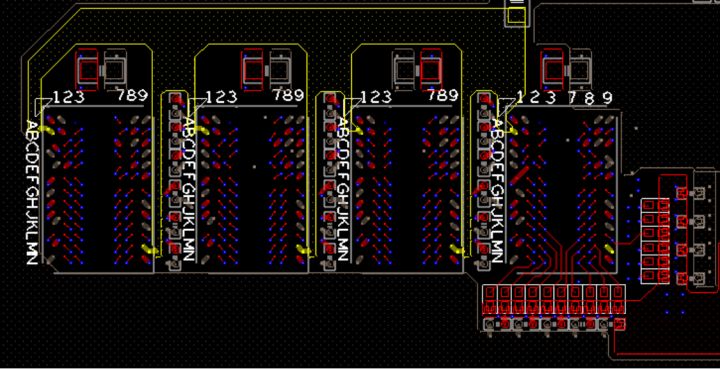

布局要求

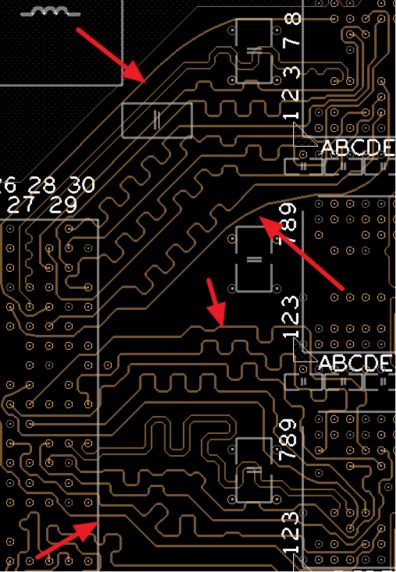

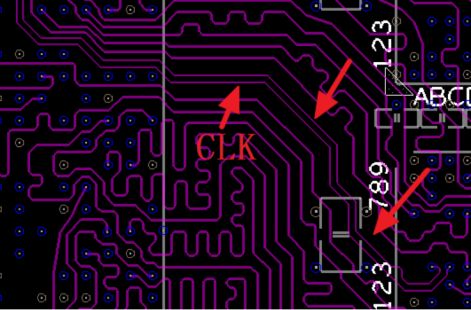

(1)地址线布局布线需使用Fly-by的拓扑结构,不可使用T型,拓扑过孔到管脚的长度尽量短,长度在150mil左右

(2)VTT上拉电阻放置在相应网络的末端,即靠近最后一个DDR4颗粒的位置放置;注意VTT上拉电阻到DDR4颗粒的走线越短越好,走线长度小于500mil;每个VTT上拉电阻对应放置一个VTT的滤波电容(最多两个电阻共用一个电容)

(3)CPU端和DDR4颗粒端,每个引脚对应一个滤波电容,滤波电容尽可能靠近引脚放置。线短而粗,回路尽量短;CPU和颗粒周边均匀摆放一些储能电容,DDR4颗粒每片至少有一个储能电容。

阻抗控制

(1)单端线:50ohm

(2)差分线:100ohm

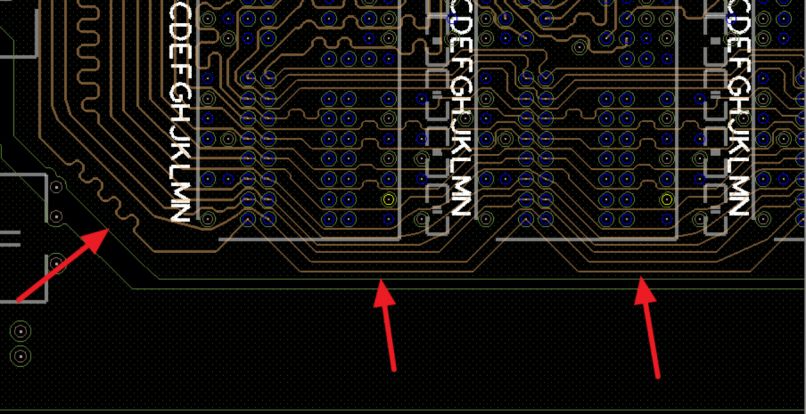

带状线和平面

(1)除了从焊盘到过孔之间的短线外,所有的走线都必须走带状线,即内层走线

(2)所有的内层走线都要求夹在两个参考平面之间,即相邻层不要有信号层,这样可以避免串扰和跨分割走线,走线到平面的边缘必须保持4mil以上的间距;

(3)数据线参考平面优先两边都是GND,接受一边地,一边自身电源,但是到GND平面的距离要比到电源平面的距离要近;对于地址线,控制信号,CLK来说,参考面首选GND和VDD,也可以选GND和GND。

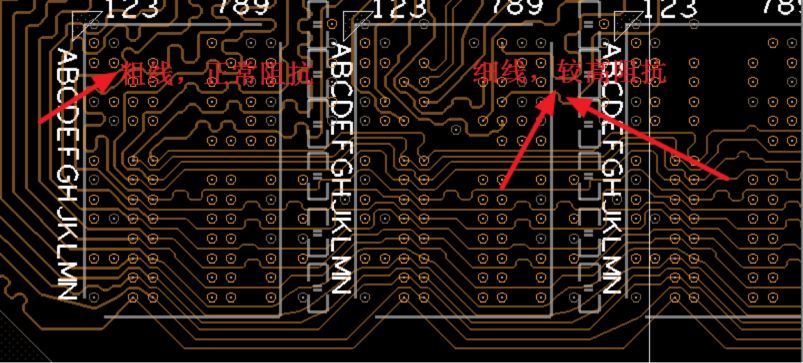

容性负载补偿

flyby拓扑要求stub走线很短,当stub走线相对于信号边沿变化率很短时,stub支线和负载呈容性。负载引入的电容,实际被分摊到了走线上,所以造成走线的单位电容增加,从而降低了走线的有效阻抗。所以在设计中,我们应该将负载部分的走线设计为较高阻抗,最直接有效的方式就是减小支线线宽。经过负载电容的平均后,负载部分的走线才会和主线阻抗保持一致,从而达到阻抗连续,降低反射的效果。

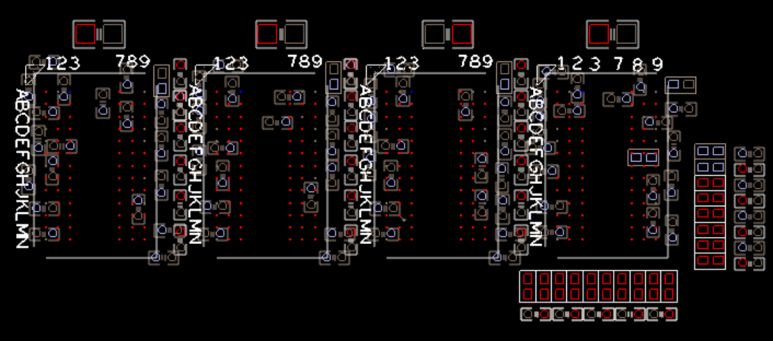

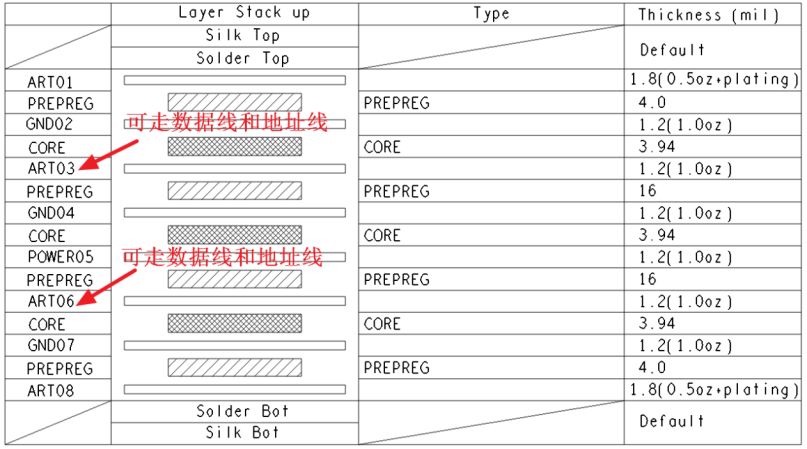

PCB叠层设计

(1)所有的DQ线必须同组同层。

(2)地址线是否同层不做要求。

(3)为了减少过孔产生的Stub,强烈建议在同一层中优先布DQ, DQS,CLK等信号。如果所有的BGA都在top层,data线尽量的靠近bottom层走,而地址,控制线则可以靠近top层走;当BGA在top层时,越靠近bottom层,过孔产生的stub越短,信号质量越好。

走线线宽和线间距

(1)线宽和线间距必须满足阻抗控制,即单端线50ohm,差分线100ohm。ZQ属于模拟信号,布线尽可能短,并且阻抗越低越好,所以尽可能的把线走宽一点,建议3倍50ohm阻抗控制的线宽;

(2)DQ和DBI数据线,组内要求满足3W间距,与其他组外信号之间保持至少4W;

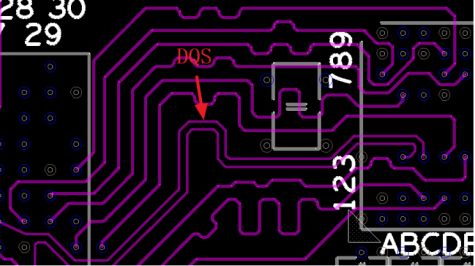

(3)DQS和CLK距离其他信号间距做到5W以上;

(4)在过孔比较密集的BGA区域,同组内的数据线,地址线的间距可以缩小到2W,但是要求这样的走线尽可能的短,并且尽可能的走直线;

(5)如果空间允许,所有的信号线走线之间的间距尽可能的保证均匀美观;

(6)内存信号与其他非内存信号之间应该保证4倍的介质层高的距离。

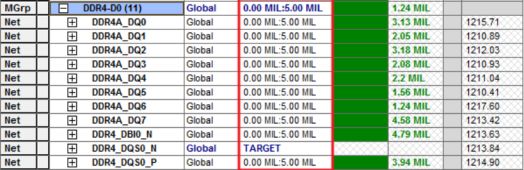

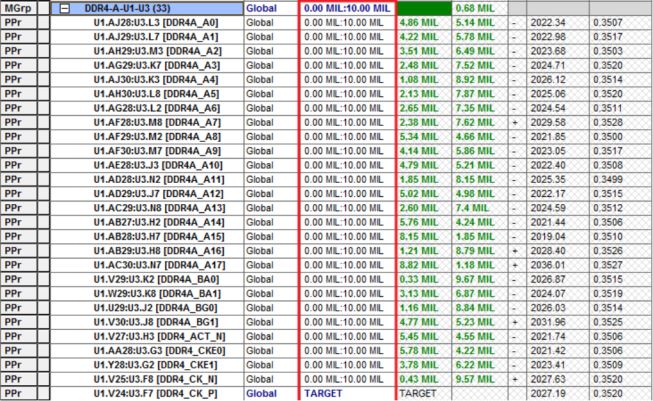

等长要求

(1)数据走线尽量短,不要超过2000mil,分组做等长,组内等长参考DQS误差范围控制在+/-5mil;

(2)地址线、控制线、时钟线作为一组等长,组内等长参考CLK误差范围控制在+/-10mil;

(3)DQS、时钟差分线对内误差范围控制在+/-2mil;

(4)RESET和ALERT不需要做等长控制

(5)信号实际长度应当包括零件管脚的长度,尽量取得零件管脚长度,并导入软件中;

(6)因有些IC内核设计比较特别,按新品设计指导书或说明按参考板做,特别是Intel,AMD的芯片,请特别留意芯片手册要求;

电源处理

(1)VDD(1.2V)电源是DDR3的核心电源,其引脚分布比较散,且电流相对会比较大,需要在电源平面分配一个区域给VDD(1.2V);VDD的容差要求是5%,详细在JEDEC里有叙述。通过电源层的平面电容和专用的一定数量的去耦电容,可以做到电源完整性。

(2)VTT(0.6V)电源,它不仅有严格的容差性,而且还有很大的瞬间电流;可以通过增加去耦电容来实现它的目标阻抗;由于VTT是集中在上拉电阻处,不是很分散,且对电流有一定的要求,在处理VTT电源时,一般是在元件面同层通过铺铜直接连接,铜皮要有一定宽度(120mil)。

(3)VREF(0.6V)VREF要求更加严格的容差性,但是它承载的电流比较小。它不需要非常宽的走线,且通过一两个去耦电容就可以达到目标阻抗的要求。因其相对比较独立,电流也不大,布线处理时建议用与器件同层的铜皮或走线直接连接,无须再电源平面层为其分配电源。注意铺铜或走线时,要先经过电容再接到芯片的电源引脚,不要从分压电阻那里直接接到芯片的电源引脚。

(4)VPP(2.5V)内存的激活供电,容差相对宽松,最小2.375V,最大2.75V。电流也不是很大,一般走根粗线或者画块小铜皮即可。

DDR4设计的约束条件挺多的,有没有觉得很难,无从下手?没关系,看文字一脸懵逼,咱还有视频教程,你离会画DDR4的距离只差一个二维码。

-

PCB参考设计规范 PCB设计注意事项2009-11-30 0

-

PCB设计有哪些注意事项!2012-12-14 0

-

48V电源的PCB设计注意事项2017-07-06 0

-

原创|高速PCB设计中,处理关键信号的注意事项2017-11-01 0

-

PCB板在手环布局和布线的注意事项2020-10-29 0

-

混合信号PCB设计有什么注意事项?2021-04-25 0

-

PCB设计中有哪些注意事项?2021-04-25 0

-

混合信号PCB设计注意事项是什么2021-04-26 0

-

使用WiFi模块的一些细节及注意事项2021-07-19 0

-

滤波电路的PCB设计注意事项2021-11-11 0

-

pcb设计注意事项2009-01-18 953

-

浅谈PCB板设计注意事项2012-05-09 3374

-

VGA OUT 的PCB设计注意事项2023-11-23 365

-

音频接口电路的PCB设计注意事项2023-11-23 509

全部0条评论

快来发表一下你的评论吧 !