英特尔的Agilex FPGA发布 必将对当前的FPGA市场带来一波最强的冲击

可编程逻辑

描述

从 Falcon Mesa 到 Agile

英特尔的10纳米FPGA终于来了。在四月刚刚结束的英特尔“以数据为中心创新日”中,曾经代号为Falcon Mesa的英特尔最新一代10纳米FPGA正式亮相,并正式命名为Agilex™。

在本文中,小编将对Agilex的六大核心技术做全面的深入解读。

灵活+敏捷=Agilex™ FPGA

Agilex是Agile(敏捷)和Flexible(灵活)的合二为一,而这两个特点正是现代FPGA技术最为核心的两大要点。

具体来说,“灵活性”就是指可编程性,它基于FPGA的核心技术——可编程逻辑阵列,可以灵活的针对不同应用场景进行编程,并改变FPGA的逻辑结构和功能。

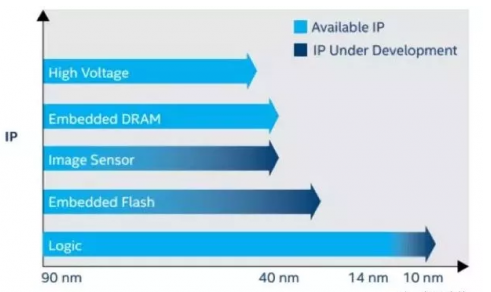

“敏捷性”指的是异构,它既可以是不同逻辑单元之间的异构,也可以是不同工艺的异构,或者两者兼而有之。如下图所示,不同类型的IP所对应的成熟工艺与迭代时间都不尽相同。只有采用异构架构,才能充分发挥不同IP和不同工艺节点的优势,取长补短,在性能和成本上取得良好的平衡。因此异构FPGA也是目前和未来业界发展和研究的主要方向。

在这个大背景下,Agilex™ FPGA应运而生。它既包含了传统FPGA灵活的可编程性,又结合了现代FPGA基于异构架构的敏捷性,因此能够同时适用于众多应用领域,并针对性的进行配置和快速迭代,如下图所示。

与进化多年的Stratix®、Arria®、Cyclone®、Max® 等FPGA产品系列相比,Agilex™ 是原FPGA巨头Altera在2015年底被英特尔收购、并成为其可编程方案事业部(PSG)后正式推出的一个全新的FPGA系列。正因如此,Agilex™ 无疑被英特尔寄予了更多的期待。

在这些期待背后,离不开来自英特尔的核心技术的加持。而这也将是区分Agilex™ 与它的前代产品、以及其他竞争对手的最主要的优势。具体来说,Agilex™ 遗传自英特尔的核心竞争优势有以下六点。

1、英特尔10纳米工艺

英特尔在半导体领域称雄几十年,靠的就是两个独门绝技:第一是众所周知的x86架构,第二则是曾经遥遥领先竞争对手的半导体制造工艺。这也促成了英特尔著名的“Tick-Tock”战略,即架构和工艺的更新逐年交错进行,同时还能保持处理器性能的稳步增长。

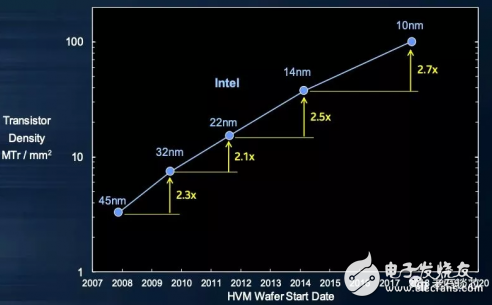

不过,这家芯片巨头在10纳米工艺上遇到了阻碍。事实上,英特尔也曾预测10纳米的研发会比之前耗时更久,如下图所示,但可能没有人想到会是这么久。

结果是,就在过去的一两年中,曾经被远远甩在身后的竞争者纷纷在十纳米这个工艺节点完成了超车,台积电和三星都逐渐将自家的十纳米工艺投入量产。

终于,2019年初痛定思痛的英特尔一口气发布了四款基于10纳米工艺的芯片产品,涵盖了个人计算平台、数据中心、5G网络等多个应用领域,并将最快于年底正式出货量产。而这次发布的Agilex™ FPGA,也正是基于英特尔10纳米工艺的旗舰级FPGA产品。

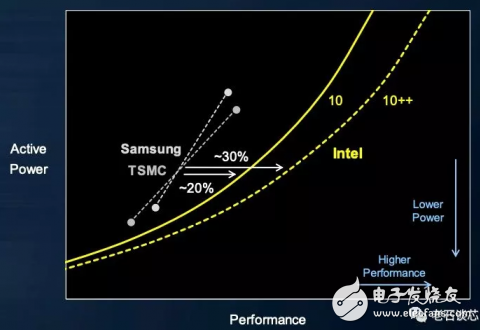

对于芯片制程而言,在相同的工艺节点下,英特尔的工艺往往具有更优异的性能,这也是业界公认的事实。一旦英特尔的十纳米工艺达到稳定并量产,预计将会比竞争对手带来20%-30%的性能和功耗优势,如下图所示。

2、系统级3D芯片

系统级3D芯片的异构集成和封装,也是英特尔的独门秘籍之一。这其中主要有两个主要技术,一个是EMIB(嵌入式多管芯互联桥接),用于提供多个异构晶片的高速互连;另一个则是2019年最新公布的Foveros 3D封装技术。

在Agilex™ FPGA中,使用了第二代EMIB技术,用以连接可编程逻辑阵列以及周围的各类子芯片集(Chiplets)。由于EMIB不需要引入额外的硅中介层,因此不需要大量的硅通孔,这样显著降低了系统的制造复杂度。同时不需要在中介层中使用长导线,因此降低了不同晶片间的传输延时,减少了信号的传输干扰。另外,在替换不同的子芯片集时更加容易,而无需重做整个芯片系统。

3、CXL:CPU与FPGA互连的终极方案

当前,FPGA的一个主要应用场景是在数据中心里作为CPU的硬件加速器,用来加速各类应用,如深度学习的模型训练、金融计算、网络功能卸载等等。

在数据中心的CPU领域,英特尔的Xeon® CPU一直是绝对的最强王者。作为数据中心加速器的FPGA,首先需要考虑的就是与Xeon® CPU的兼容性问题。很明显,作为具有“纯正血统”的Agilex™ FPGA,从出生伊始就相比竞争对手占据了天时和地利。

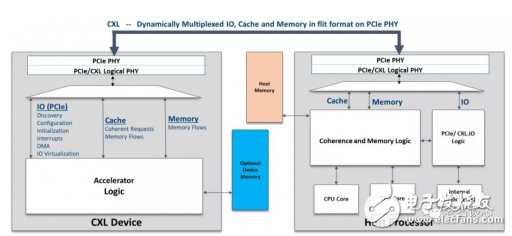

缓存一致性问题一直是硬件加速器领域亟需解决的核心问题之一。而解决这个问题的主要方法,就是明确和普及CPU与硬件加速器之间的内存互联协议,就好比大家熟知的用于CPU和加速器通信的PCIe协议等等。

在今年3月,英特尔宣布联合微软、阿里、思科、戴尔EMC、Facebook、谷歌、惠普企业HPE和华为等公司,共同组件一个全新的互联标准,名为Compute Express Link – CXL,如下图所示。

有趣的是,CXL的发起者中有四个互联网巨头、两个服务器设备制造商、两个网络设备制造商。这种多元性立体的呈现了CXL的目标应用领域:互联网数据中心、通信基础设施、云计算与云服务等等。而这些领域也正是FPGA大显身手的重要平台。

对于Agilex™ FPGA,它将原生支持CXL协议,并将成为业界首款面向Xeon® 可扩展处理器的内存一致性硬件加速器。值得注意的是,CXL协议基于PCIe设计和扩展,如下图所示,这样可以完全复用PCIe PHY和通道,与其他类似的协议相比有着明显的易用性。

因此,Agilex™ 对CXL的原生支持,势必会在“天时”和“地利”的基础上,为它在数据中心的广泛使用带来巨大的“人和”优势。

4、可变精度DSP

FPGA在人工智能应用中的最大优点之一就是可以采用可变精度的字长表示和数学运算,从而带来巨大的性能提升。在现有的英特尔FPGA中,已经可以支持固化的定点数以及FP32的DSP运算。

在Agilex™ FPGA中,又扩展支持了FP8、FP16和BFLOAT16的DSP运算,同时也增加了9x9乘法器的数量,以及乘法器的配置方式等等,一些常用的DSP配置结构如下图所示。这些针对AI应用的革新,也会极大提升未来FPGA在AI领域的使用范围。

5、增强版HyperFlex架构

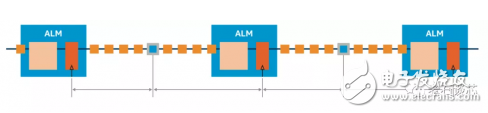

HyperFlex的主要思想就是在FPGA的布线网络上,加入很多名为hyper-register的小型寄存器,这样可以把原本比较长的时序路径分割成多个较短的路径,从而达到频率提升的作用,如下图所示。

但在很多情况下,不是所有的hyper-register都会被使用。为了减小额外延时,对FPGA设计工具中的retiming和自动流水线算法提出了更多的要求。

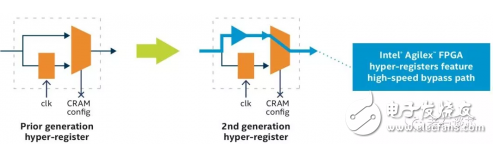

在英特尔的Agilex™ FPGA中,这个问题得到了针对性的补强,方法其实非常简单粗暴,就是尽量缩小hyper-register的旁路路径的延时(高达40%),如下图。这样当某些hyper-register不使用时,其对应的系统延时可以达到导线级的标准。

6、OneAPI:英特尔的雄心

在2018年末的英特尔架构日上,英特尔的芯片首席架构师Raja Koduri对外公布了公司正在着力研发的一件“大事”:一个名为OneAPI的软件编程框架。

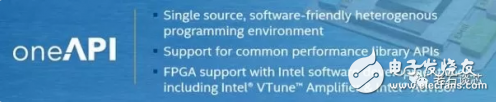

顾名思义,OneAPI将会为英特尔的CPU、GPU、FPGA、以及各种AI和其他应用的硬件加速器提供一个统一的编程接口,使得开发者可以随意在底层硬件之间进行切换和优化。OneAPI的口号是“晶体管一个也不能少”,这也很好的总结了OneAPI的终极目标。

除了编程接口外,OneAPI想必还会包含一个完整的开发环境、库、驱动等必要的要素,它代表了英特尔最大的野心,就是将旗下所有的芯片和硬件产品通过这个软件系统连接起来,并实现无缝切换。同时,可以预见英特尔还将围绕这个软件系统逐步构建生态环境。因此这个系统一旦实现,将成为其他任何竞争对手无法匹敌的优势。

对于新发布的Agilex™ FPGA,它也将成为首款支持OneAPI的英特尔FPGA产品,见下图。

结语

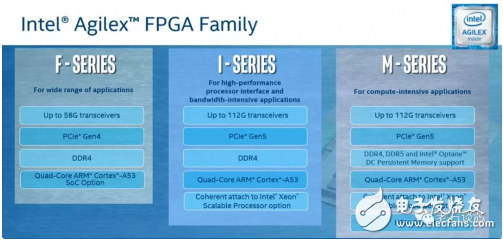

英特尔在发布会上宣布,Agilex™ FPGA将有F、I、M三个产品系列,见下图,并最早将于今年第三季度交付到客户手中进行前期评估。

小编相信,这款全副武装了英特尔各种黑科技的最高段位FPGA,必将对当前的FPGA市场带来一波最强的冲击。

-

5G芯片市场,你看好英特尔还是高通?2017-03-01 0

-

OpenCL平台和英特尔Stratix 10 FPGA的结合使用2019-07-17 0

-

展望未来英特尔FPGA设计,介绍新型224G PAM4收发器2020-09-02 0

-

英特尔重点发布oneAPI v1.0,异构编程器到底是什么2020-10-26 0

-

集万千宠爱于一身!英特尔全新 Agilex FPGA发布2019-04-16 3816

-

英特尔发布Agilex FPGA新品2019-06-12 489

-

探秘Agilex FPGA,看懂英特尔的技术创新力2019-07-11 258

-

英特尔Agilex FPGA家族全系列概述表2021-03-12 3345

-

解密英特尔® Agilex™ FPGA家族的八大特性2021-04-07 1977

-

基于英特尔®AGILEX™ FPGA和SOC FPGA的BittWare加速“双星”发布2021-06-30 2118

-

全新英特尔Agilex D系列FPGA和SoC适用于中端FPGA应用2022-11-03 842

-

使用英特尔® Agilex™ FPGA 解决以数据为中心的挑战2023-01-04 507

-

英特尔Agilex FPGA的优势和特性2023-09-08 657

-

英特尔 FPGA的新品及全矩阵应用2023-11-17 401

-

英特尔Agilex 3 FPGA产品家族介绍2023-11-24 481

全部0条评论

快来发表一下你的评论吧 !