如何使用xSignals来定义高速信号的路径

EDA/IC设计

描述

在高速设计中,基于时序的考虑通常要对信号做线长匹配。对于只有2个管脚的信号路径,计算和匹配线长这一过程非常直接、清晰。但对于大部分高速设计来讲,情况会更为复杂,这些情况包含但不仅限于:

1.信号路径中需要使用端接电阻(termination resistor),这时需要调制的线长是包括端接电阻在内的不同网络。

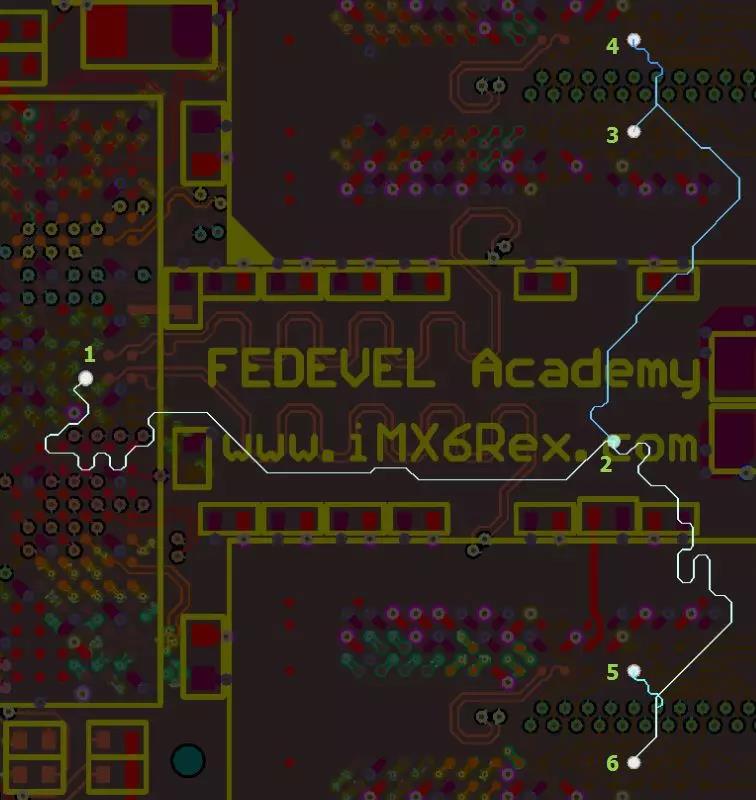

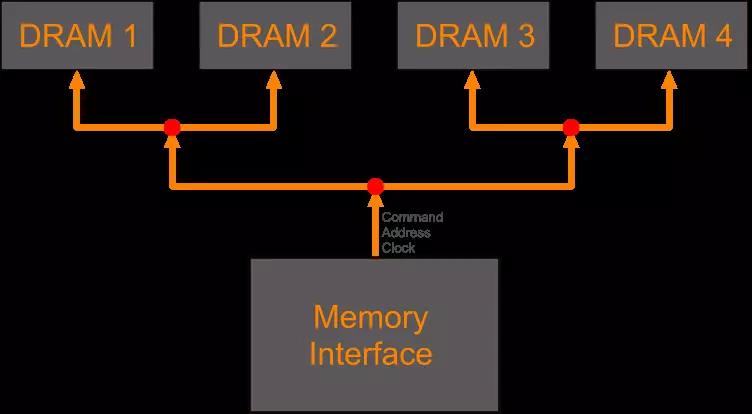

2.Data总线常用的的T点拓扑结构。如下图,实际需要调等长的是同一网络的不同分支:2-3 = 2-4 = 2-5 = 2-6。

3.DDR3/DDR4中地址总线、控制总线用到的菊花链(Fly-By)拓扑结构,需要对同一网络的不同branch进行线长匹配:

在引入xSignal之前,AD的线长规则(Net Length)及匹配线长规则(Matched Net Length)只能针对同一网络,无法对同一网络中某一段路径进行调制,也无法对端接电阻进行处理。虽然一直存在“From-To”对象,但一直存在Bug,“From-To”对象针对规则无效。..。.工程师无奈只能使用Excel计算出每段的长度,然后慢慢调整,效率很低。

AD15之后,xSignal的出现不仅可以解决Branch线长调制的问题,也可以解决含端接电阻的信号路径调制问题。简单来说,xSignal可以定义两个节点之间的信号路径,无论这两个节点是同一网络还是不同网络。

创建一个新的xSignal

创建xSignal主要有以下几种方式:

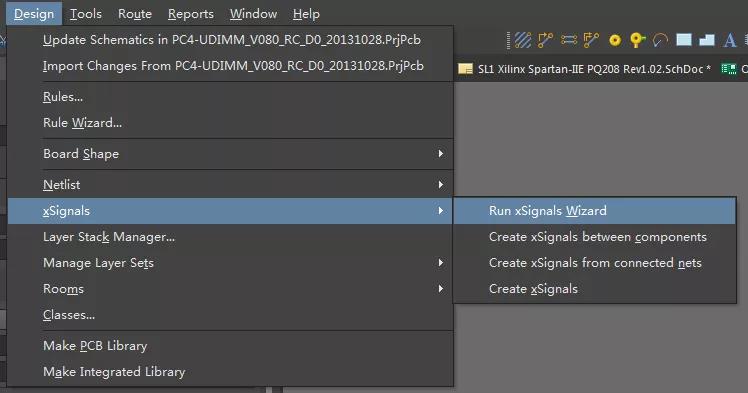

使用向导(Run xSignal Wizard)

选中源器件,并点击“Create xSignals between components”来定义两个器件间的xSignal

选中源器件,并点击“Create xSignals from connected nets”,通过源器件及与源器件连接的网络来定义xSignal

直接点击“Create xSignals”使用对话框手动创建Xsignal。

向导的使用有点复杂,今后有空再讲,这里主要讲一下其它两种方式。

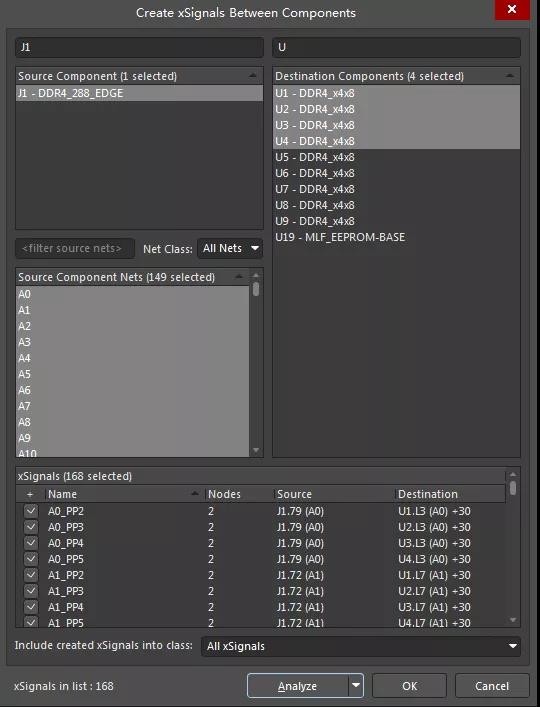

使用“Create xSignals between components”对话框

点击菜单Design » xSignals » Create xSignals,对话框中左侧为源器件,右侧为目标器件;目标器件可以多选。

过以下步骤创建xSignal:

选择源器件(source component)

选择目标器件(destination component)

选择感兴趣的网络

点击“Analyze”,AD会自动分析两器件之间感兴趣网络的所有路径。请仔细检查Source和Destination中的结果是否正确(尤其是存在端接电阻的情况)

在Include created xSignals into class栏中输入创建的xSignal Class的名称,默认会归类到All xSignals类中。

点击OK完成创建。完成后可以在PCB面板中看到所有已创建的xSignal。

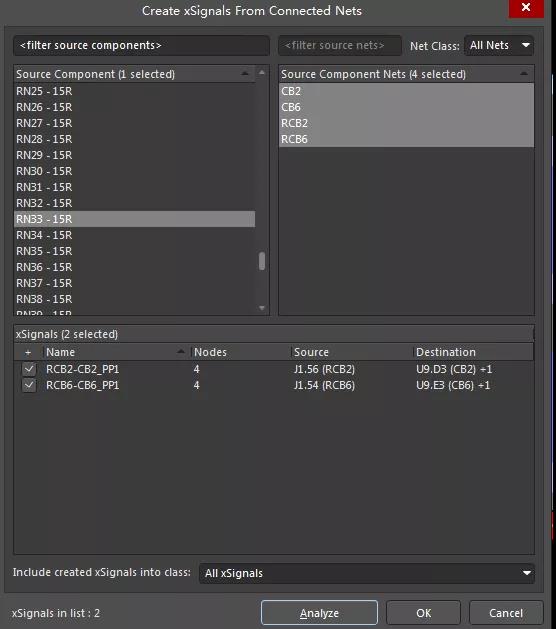

使用“CreatexSignals from connected nets”对话框

如果您的xSignal包含端接电阻,使用这个方式创建xSignal更为直接。选中端接电阻后点击“CreatexSignals from connected nets”:

上图为选中4个pin角的排阻RN33,右侧Source Component Nets中为排阻连接的所有网络。点击“Analyze”后,系统为自动分析出可能的xSignal。注意,请仔细检查Source和Destinatiion中的网络是否正确,如果不正确,可以进行手动调整。确认后完成xSignal的创建。

网络拓扑(Net Topology)的作用

xSignal定义的是两个节点(或焊盘)之间的信号路径。AD是根据两个节点间的连接线(connection line)来分析信号路径的,而连接线的定义方式是通过Routing Topology规则来决定的,默认Routing Topology的规则为shortest,即最短。

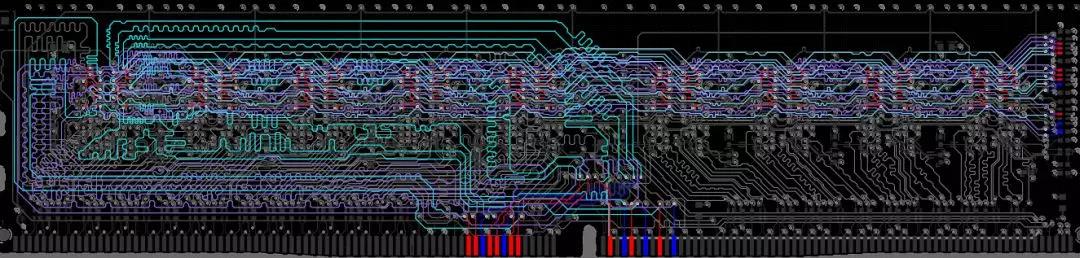

下图为Fly-by拓扑结构下CPU连接到4个Memory的动画,可以清楚地看到4个xSignal的定义情况:

T点拓扑结构(Balance T)中支点的定义

T点拓扑结构不仅需要对主干做等长,还需要对支干做等长。

上图中的红色点即为支点(Branch point),需要保证每个支点到DRAM1,2,3,4都是等长的。

问题来了,AD中的xSignal必须使用实体的器件Pin脚创建,不支持独立的焊盘或过孔(Free Pad/Via)。在Mentor和Cadence中,可以将某个Pad或Via定义为“虚拟T点”,从而进行分支的线长调制,但在AD中,目前还无法支持这一方式。一个变通的方法是为独立的Pad/Via制作一个单独的器件(原理图符号+封装),然后将这一器件放在T点处。虽然有些麻烦,但毕竟解决了AD之前无法对分支网络进行线长规则定义且无法进行线长调制的尴尬。

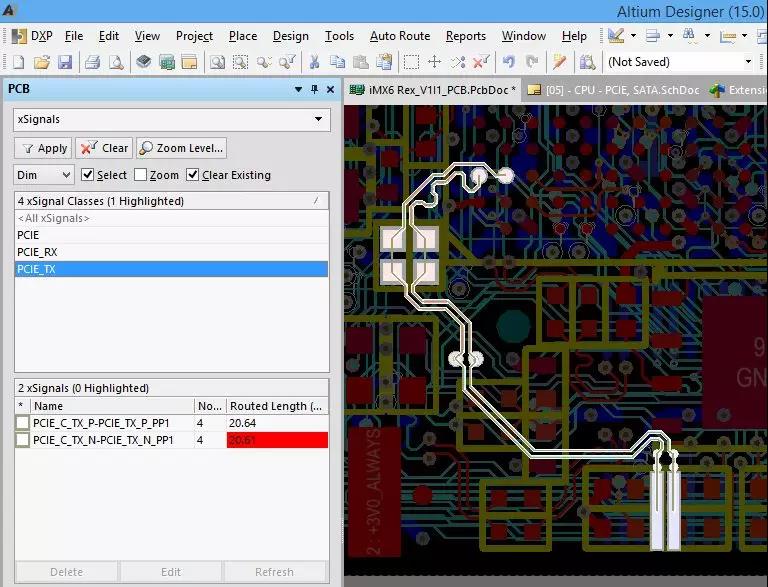

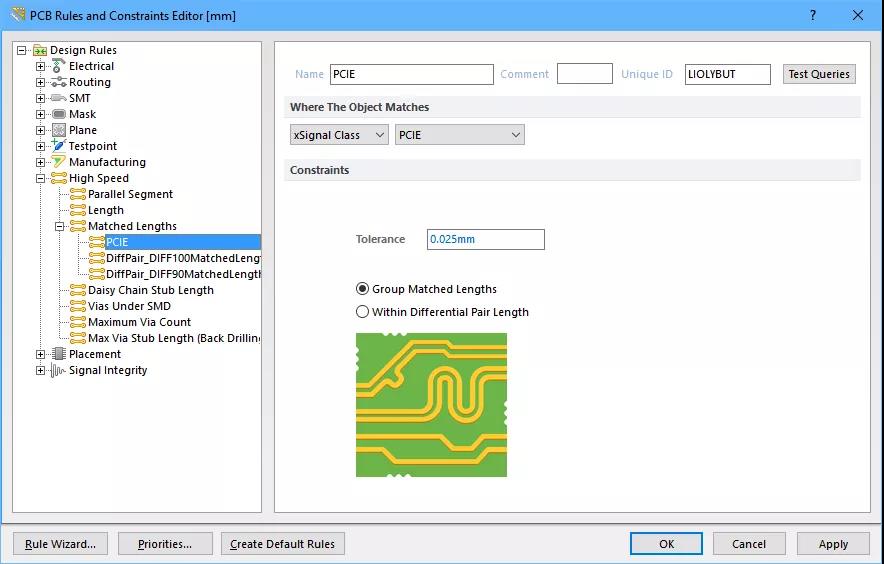

Length & Matched Net Length规则

xSignal创建完成后,接下去的使用方法和网络(Net)完全一样了。记住,xSignal Class对应的是Net Class; xSignal对应的是Net。区别在与xSignal定义的pin到pin之间的路径,而Net是所有属性相同的网络。

下图是PCB面板中查看xSignal的示意图以及定义Matched Net Length规则的一个截图:

具体规则的创建在以后的章节中详细介绍。

总结一下,xSignal是一个非常重要的功能,基本解决了Altium Designer之前无法在高速设计中准确调制信号线长的问题。结合如何准确测量信号长度一文中提到的对线长计算精度的提高,大大减少了工程师在高速设计中Layout的时间,且提高了设计的准确性。

-

如何区分高速信号和低速信号2022-12-12 6301

-

高速信号和低速信号有什么区别,怎么定义高速和低速呢2014-12-18 0

-

高速信号分析的几个基本问题2017-12-16 0

-

高速PCB设计——回流路径分析2021-02-05 0

-

如何加强信号路径的性能2009-09-23 431

-

差分信号回流路径的全波电磁场解析2011-11-09 999

-

设计高速混合信号系统信号路径的详细资料概述2018-05-15 877

-

PCB设计EMI问题:高速信号走线九大规则2019-04-03 6933

-

PCB设计中高速信号与低速信号如何区分2019-08-20 9359

-

信号路径中的模拟及混合信号部分的器件选择和设计事项2020-07-17 755

-

看待高速信号的不同定义2020-10-12 2327

-

高速电路是什么,什么信号才属于高速信号?2022-06-24 6231

-

PCB设计高速信号布线技巧2023-02-21 1212

-

高速信号的判断标准2023-03-08 1826

-

什么是信号回流路径?2023-11-24 832

全部0条评论

快来发表一下你的评论吧 !