优秀的高速PCB设计之去耦电容

描述

电源和地平面

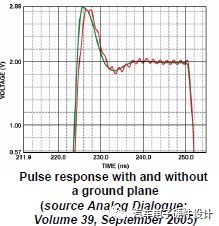

应该尽可能的使用电源和地平面,

Why?

在设备和电源之间提供一个低阻抗的

路径

提供屏蔽

提供散热

降低分布电感

一个完整的无破损的平面是最优选择

破碎的地平面会在走线的上下层之间引入寄生电感

Remember!

低频时,电流总是流过最小电阻路径

高频时,电流总是渡过最小电感路径

去耦电容(或“旁路电容”)

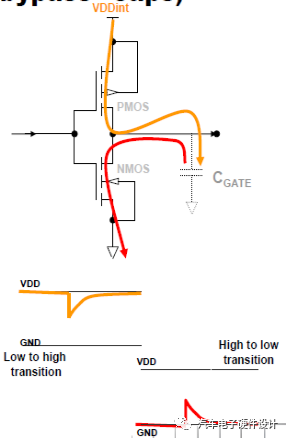

当设备里的门电路开关时,设备里的阻抗会有一个瞬时的变化

结果就是电流会有一个瞬时的变化

去耦电容会这些瞬时的变化提供一个低阻抗的电流源

降低电源地之间的电压波动

帮助电源地信号工作在设备的工作SPEC之内

高速设计中有5个频段需要调节

DC至10Khz

通过调节模块来调节

10Khz至100Khz

通过去耦电容来调节

100Khz to 10Mhz

通过100nf(0.1uf)来调节

10 Mhz to 100Mhz

通过10 nf来调节

100Mhz至更高

通过1nf和PCB电源和地平面来调节

需要多少去耦电容才够用呢?

取决于系统

需要考虑工作频率,I/O的开关数量,每个Pin脚的容性负载,走线的特征阻抗, 结点的温度,芯片内部的运算

对于处理器,要考虑各种运算方式,缓存,内存,DMA,等等

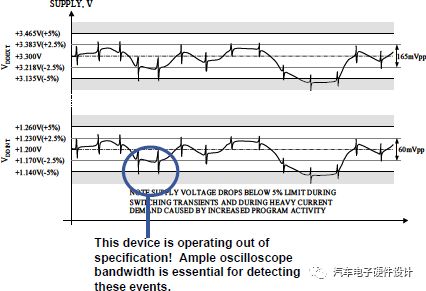

经验法则:从DC至高频的每个频段内,供电引脚的电压波动都就小于5%

DC供电电压的最大波动加上噪声的最大值应该小于供电电压的5%

需要一个足够带宽的示波器

有很多的方法去评估总共需要的容值,以及如何分布电容

这是一个复杂的问题,特别是在处理现在那些包含有成千上万门电电路的处理器的时候.

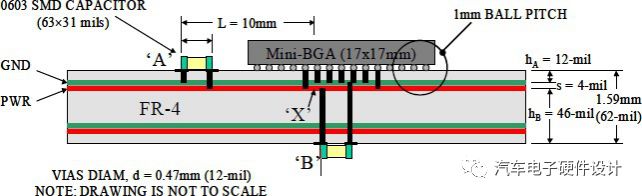

为了获得最好的性能, 应该尽可能的降低供 电引脚与去耦电容之 间的电感与电阻

PCB布线和过孔会增加阻抗

当使用电源/地平面对时,电容如同在PCB顶层 一样有效

100Mhz以上的有效电容…

随着时钟频率和边缘变化率的提高,如何有效的使用旁路电容变得越来越困难

电容的ESL(等效串联电感)随着频率的增加而增加

电容的ESR(等效串联电阻)的增加会降低电容的效力

电容的寄生参数(pads,vias)所带来的电抗会随着频率增加而增加

100nf的电容在100Mhz之上是无用的

-

去耦电容在PCB板设计中的应用2009-12-09 0

-

PCB设计中的去耦电容和旁路电容2011-02-24 0

-

电容在高速PCB设计的应用2012-08-14 0

-

高速PCB设计电容的应用2014-10-24 0

-

【下载】《PCB设计技巧》 | 一线优秀电子工程师PCB设计进阶必备2017-07-26 0

-

资深工程师精心整理的PCB设计技术(高速、混合、微弱)2019-03-25 0

-

PCB设计之电容2019-08-13 0

-

PCB设计时去耦电容该怎么放呢?2023-04-11 0

-

电容在高速PCB设计中该如何摆放呢?2023-04-20 0

-

EMC之PCB设计技巧2023-12-19 0

-

电容在高速PCB设计中的应用2009-08-16 517

-

高速PCB设计电容的应用 5页 0.3M2016-12-16 408

-

高速PCB设计电容的应用.zip2022-12-30 204

全部0条评论

快来发表一下你的评论吧 !