瑞萨电子推出基于SOTB工艺的嵌入式闪存低功耗技术 实现能量收集并无需电池供电

存储技术

594人已加入

描述

瑞萨电子株式会社宣布,推出基于65nm SOTB((薄氧化埋层上覆硅)工艺的新型嵌入式闪存低功耗技术,可提供1.5MB容量,是业界首款基于65nm SOTB技术的嵌入式2T-MONOS(双晶体管-金属氧化氮氧化硅)闪存(注1)。通过引入全新电路技术来降低闪存中外围电路的功耗,实现了在64 MHz的工作频率下低至0.22 pJ/bit的读取能耗——这是业界嵌入式闪存在MCU上的最低水平。用于外围电路的新低功率技术包括:(1)在检测存储器中的数据时降低能耗;(2)在将读取的数据发送到外部时减少传输能耗。该先进技术帮助读取存储器数据时的能耗大幅降低。

瑞萨在6月12日在日本京都召开的2019年度“VLSI和电路技术专题研讨会(2019年6月9-14日)”上展示相关测试结果。

基于SOTB的新技术已在瑞萨R7F0E嵌入式控制器中所采用,该控制器专门用于能量采集应用。瑞萨独有的SOTB工艺技术可显著降低工作和待机状态下的功耗。通常,这两种状态下的功耗互为消长:即一种功耗较低意味着另一种功耗较高。当从闪存读取数据时,新技术大幅降低功耗。与非SOTB 2T-MONOS闪存(约需50μA/MHz读取电流)相比,新技术实现的读取电流仅6μA/MHz左右,等效于0.22 pJ/bit的读取能耗,达到MCU嵌入式闪存最低能耗级别。这项新技术还有助于在R7F0E上实现20μA/MHz的低有效读取电流,达到业界最佳。

全新嵌入式闪存技术的关键特性:

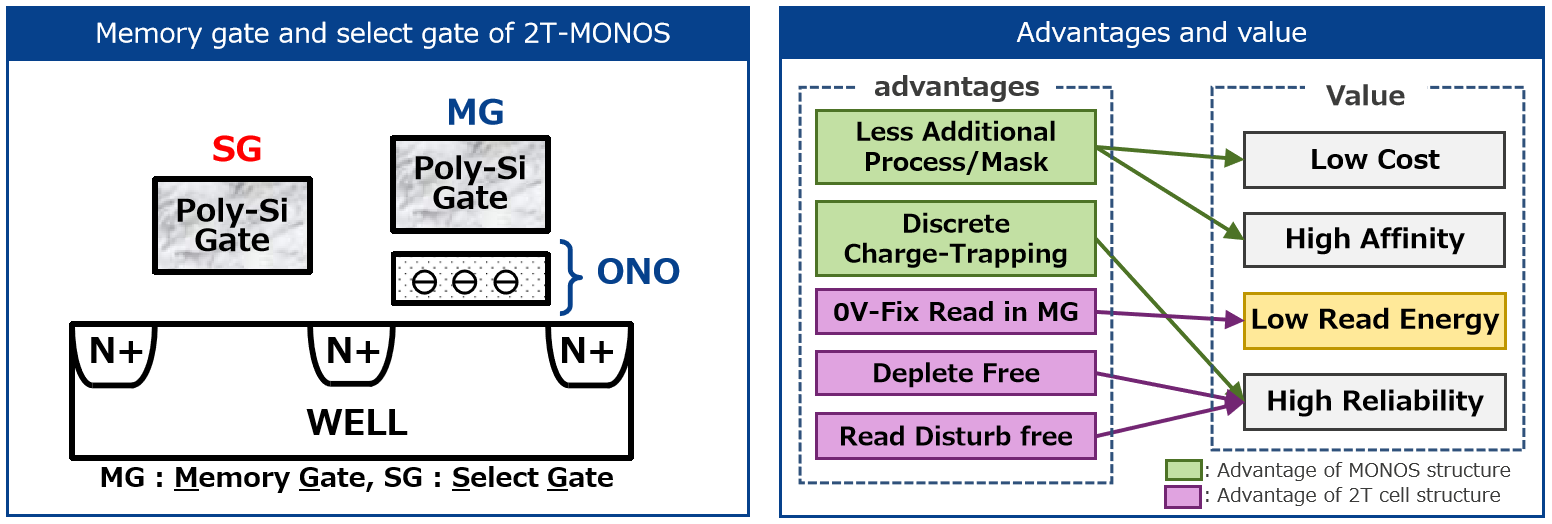

适用于SOTB工艺的低功耗2T-MONOS闪存

采用SOTB工艺的2T-MONOS嵌入式闪存具备包含电隔离元件的双晶体管结构。与单晶体管结构不同,在读取操作期间无需负电压,使读取数据时的功耗降低。此外,同其它存储器处理相比,MONOS在生产过程中使用更少的掩模,并可使用离散电荷捕获方案存储数据,从而能够在不增加生产成本的情况下带来低功耗和高重写可靠性。

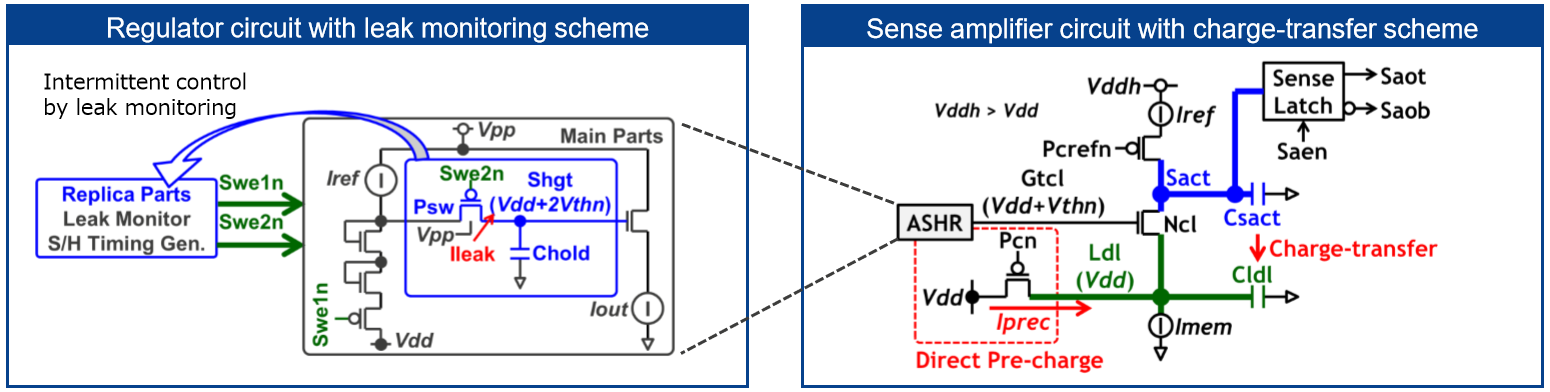

用于超低耗能的感测放大器电路及稳压器电路技术

存储器读取过程中的大部分能量消耗发生在识别数据的感测操作,以及将识别的数据输出至外部这两个环节。为了解决此问题,单端感测放大器在感测操作期间显著降低了位线预充电能量,其采用全新电荷转移技术,可提高预充电速度和能源效率。此外,新推出的稳压器电路技术利用漏电监测,对感测放大器的基准电压进行最佳间歇控制,使其以恒定的方式消耗能量。这些先进技术不仅大幅降低能耗,同时加速感测操作。

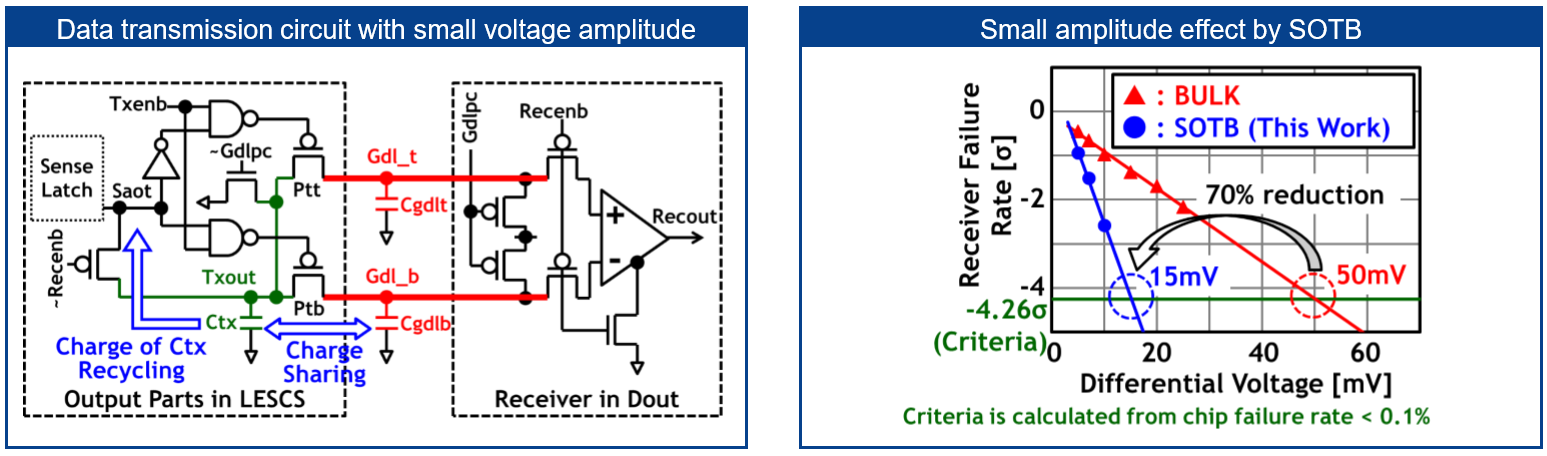

大幅削减数据传输能耗的电路技术

SOTB工艺的特性之一是实现了晶体管阈值(Vth)波动的最小化。新技术借助这一优势,利用极小的电压幅值实现数据传输。当读取数据发送至外部时,该技术使得传输能量的消耗显著降低。

瑞萨通过帮助使端点设备更加智能化,以加速推动“智能社会”的发展。瑞萨认为,通过无电池方案,能源收集系统彻底摆脱更换电池的困扰,是实现这一目标的必要步骤。同时,瑞萨将持续致力于帮助实现环保型智能社会的技术开发。

注释

(注1)MONOS:金属氧化氮氧化硅。此技术使瑞萨在EEPROM、安全MCU和其它产品领域取得了超过20年的优异业绩。MONOS技术应用于瑞萨MCU产品中的嵌入式闪存。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

瑞萨电子推出采用自研RISC-V CPU内核的通用32位MCU2024-03-30 0

-

ESC - 瑞萨和Redpine公司合作超低功耗,高吞吐量的802.11n Wi-Fi...2013-06-27 0

-

嵌入式系统中的低功耗设计2014-01-21 0

-

用能量收集和低功耗蓝牙设计无电池信标2016-02-23 0

-

医疗系统从环境收集能量2016-02-23 0

-

常见能量收集技术2016-02-23 0

-

脉冲能量收集的供电电路2016-03-01 0

-

低功耗MCU为能量收集应用2016-06-29 0

-

介绍能量收集、能量储存和电源管理解决方案的优点、构建以及发展趋势2017-07-04 0

-

瑞萨电子低功耗MCU 78K0/Kx2-L产品特征2019-06-27 0

-

超低功耗的嵌入式应用的实现:降低系统中电池功耗2020-08-20 0

-

基于瑞萨独有的SOTB™制程工艺的MCU荣获2019年度MCU产品奖2020-10-22 0

-

在嵌入式Linux平台下的功耗管理技术2021-11-05 0

-

超低功耗 MCU 的能量收集如何消除电池2022-12-28 643

全部0条评论

快来发表一下你的评论吧 !