基于MCU的设计快速发展给SoPC带来变革

描述

FPGA的实现技术

按传统看法,FPGA使用内存技术来存储FPGA需要的逻辑配置。目前在用的有四种技术实现方式,每种都有其优缺点:基于SRAM的FPGA,带内部闪存的SRAM,基于闪存的,和反熔丝(又称OTP,因为它们仅可编程一次)。

•基于SRAM的FPGA将逻辑单元配置文件存储在静态存储器中,而静态存储器则由锁在器阵列组成。由于SRAM是易失性,这种类型的FPGA必须在每次系统启动时重新编程。存在两种基本的编程模式:

o主模式,此时FPGA从外部存储源读取的配置数据,比如从外部闪存芯片。

o从模式,此时FPGA由一个外部主设备来配置,比如由一个处理器。通常情况下,主要通过一个专用的配置界面或通过使用边界扫描(JTAG)接口来完成。

o带有内部闪存的基于SRAM的FPGA省去了外部非易失性存储的需求,所谓内部闪存包含了内部闪存块。

o纯正的基于Flash的FPGA采用Flash作为一个主要存储源来进行配置存储,因此不需要外部非易失性存储器。该技术比基于SRAM的FPGA耗电少,更耐辐射的影响。

o基于反熔丝(OTP)的FPGA与前面提到的技术差异很大,因为它们仅可编程一次。 (反熔丝器件最初不传导电流,但可以烧写成导通状态)。

当前基于SRAM的FPGA密度最高,但功耗也大,需要一个外部非易失性存储器来存储配置数据流。带有内置闪存模块的基于SRAM的FPGA不需要外部配置存储器。相较于基于SRAM的技术来说,基于闪存和反熔丝的FPGA的功耗要小得多。

内嵌处理器内核

可编程器件最初是为了替代胶连逻辑,但随着门密度的增长,FPGA和CPLD厂商开始加入独特功能的电路,来增强其未分配的门和逻辑的功能。这就导致了可编程芯片(SOPC)的出现,其中包含处理器这样复杂器件的整个系统都被集成在单个可编程逻辑器件中。

今天,大多数FPGA和CPLD厂商提供一系列产品,供应MCU和其它IP核功能。使用内核使得系统设计人员接触到熟悉的开发工具集、操作系统和适用应用需求的可调性能。

有两种内核——硬核和软核。软核按逻辑功能描述——并非物理实现——并且一般由HDL代码组成。硬核,如其名称所示,带物理实现。当与FPGA和CPLD一同使用时,硬核通常称为嵌入式内核,因为它们嵌入在裸芯中并被可编程逻辑环绕。

软核有两种实现方案。第一种——通常更常见——是采用供应商已经支持的设计(但仍取决于设计团队来决定增加I / O和其它外围设备)。另外一个,设计团队HDL具有代码购买权,并把它纳入FPGA的HDL代码中。

为加快研发时间并让系统设计者更容易使用,可编程逻辑供应商提供了各种流行的MCU内核。 例如Altera公司,提供来自ARM、飞思卡尔半导体和英特尔的可用内核——同时附带自己的Nios和Nios II处理器内核,这些自有内核不需要支付版权费。

赛普拉斯半导体公司的PSoC5集成了可配置的模拟和数字外设功能、存储器和微控制器。PSoC5使用67 MHz的ARMCortexTM-M3内核。PSoC4集成了ARM的Cortex-M0核心,而PSoC3集成了英特尔的8位MCU8051核心。

SoPC的优点

使用内含MCU功能的SoPC有几个强大理由。第一个是要意识到使用专用MCU的隐形成本。如果该部件不具备有关特性的适当组合,例如,外部逻辑和软件,那么必须重新开发以弥补功能缺口。尽管MCU供应商提供具有专门特性的器件,以满足特定的应用需求,但这些芯片没有考虑到动态的市场条件下可能需要在非常短的时间内加入一个新的接口或外围设备的可能情况。

设计目前最先进工艺技术的新款微控制器成本很高,也需要很长的时间。MCU供应商已经通过加入更多的特性来回应市场需求——但其中的一些特性在某些应用中并无任何用途。这也增加了产品成本,而这在成本敏感的市场中是致命的。

SoPC的出现“帅气”地解决了这些问题。这种芯片可在设计过程中根据需要进行编程和重新编程,加快快速原型开发和缩短产品进入市场时间。 如果需求发生变化,SoPC还可以现场升级——即便该设备已经在某个产品中部署过。

因为具备全面验证、固件开发和现场测试等优点,开发风险可以最小化。设计工程师可以在系统中运行SoPC,从而检测该设备在真实世界运行情况,从而确定潜在的设计缺陷。

在单个SOPC开发系统级软件可以大大缩短整个软件的开发周期。采用FPGA供应商的工具可以更容易地发现bug,并确定兼容性问题。如果所需功能不能在软件中实现,识别出额外的硬件支持需求也宜早不宜迟。对于之前未被发现的缺陷或加入新功能来说,SoPC可以快速修改,而不需要大量的一次性工程费用或冗长的制造周期。他们还提供展示样品,可供销售人员使用来增加确保客户预购的概率。除了快速原型的优势外,许多情况下SoPC也可用于批量生产。

案例:汽车电子中处理器的灵活性

汽车对集成MCU的需求基本无止境。每一个主要系统——仅列出其中的几个:发动机控制、制动、底盘和娱乐信息——都至少需要一个MCU。传统上,需求由定制的MCU来满足,但随着应用(以及各种MCU变体)数量的增加,这一策略也受到质疑。汽车制造商正在寻求更灵活、更易定制的解决方案,在某些情况下,FPGA是合适的选择。

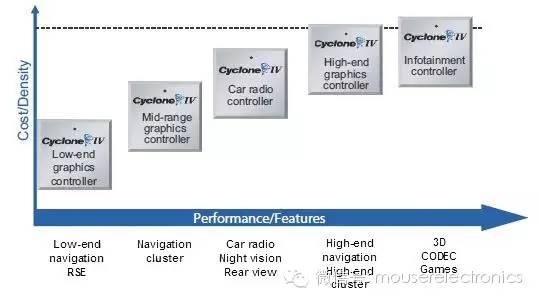

在汽车电子中已经开始使用FPGA来实现图形控制器,部分原因是因为随着计算和I / O需求的增长,FPGA能够迅速重新配置,以在没有大幅增加一次性工程费用的前提下满足新挑战。图4显示了Altera的CycloneIV,它可以被重新配置以处理日益苛刻的应用。

图4:Altera的Cyclone IV是一系列汽车图形应用中具有成本效益的解决方案。

在每个实现中,Altera的Nios II MCU内核可以根据设计人员的规格自动产生。通过使用QuartusII设计软件中的Altera SOPC生成器,给设计选择合适参数后,可以实现逻辑所需的精准功能和相应功耗。

NIOS II采用RISC架构,带有独立的32位地址和数据总线。两种总线都有自己的缓存。然而设计师做出最终决定,比如是否为代码和数据使用独立的缓存——或者使用共享内存方式。尽管Nios II具有其他先进的处理器功能,但设置决定了它们的最终特性。举例来说,硬件乘法器、桶形移位器以及硬件除法可以作为可选项。同样的,指令和数据高速缓存也是可选项,可以改变大小或完全省掉。

结论

使用SoPC的解决方案带来的灵活性为设计人员提供更多的机会,比如为某个特定应用开发精准的微控制器。该芯片可在设计过程中根据需要进行编程和重新编程,从而实现快速原型和缩短进入市场时间。现场测试可以在设计周期结束后立即完成,甚至是同步完成。 如果需求发生变化,SoPC也可以现场升级——即便该器件已经在某个产品中部署过。

-

U信通手机对讲能让集群通信行业带来变革吗2009-09-17 0

-

FPGA/SOPC开发快速入门教程中文版2012-05-23 0

-

FPGA SOPC开发快速教程2012-08-07 0

-

USB TypeC接口技术即将带来的行业变革2017-02-14 0

-

汽车电子技术之汽车仪表盘MCU变革概述2019-07-09 0

-

RFID技术给军事物流领域带来什么?2019-08-05 0

-

汽车技术变革的重大影响有哪些?2020-05-01 0

-

HarmonyOS学习之七:鸿蒙系统给IoT带来新的契机2020-11-27 0

-

5g技术给新能源发电带来变革_精选资料分享2021-07-12 0

-

sopc和fpga差别2021-07-22 0

-

FPGA/SOPC开发快速入门教程2008-08-06 784

-

FPGA_SOPC快速开发教程2010-11-01 431

-

公链未来可以为哪些行业带来变革2019-04-16 839

-

5G的发展带来了时代的变革2020-10-15 2571

-

Matter如何为家庭自动化带来变革2022-12-22 531

全部0条评论

快来发表一下你的评论吧 !