PCB设计各种信号完整性问题

描述

在本系列中,我们将回顾和探讨影响当今高速印刷电路板 (PCB) 设计的各种信号完整性 (SI) 问题,以及如何通过仿真来避免这些问题。

如果您是贸然进入了高速设计领域的新手工程师之一,并且被“信号完整性仿真”这个术语所震撼,请不要烦恼。在这次博客之旅中,我们先来回顾一下基础知识,然后再介绍一些更高深的话题。

我们已不再生活在信号“0”和“1”的数字领域里了,因此我们现在需要考虑在从发射器到接收器的传输过程中模拟对信号都有些什么样的影响。

随着时钟速度的增加和上升/下降时间的加快,PCB 走线不再是理想的导线,而且对其承载的信号不透明。根据一般的经验法则,任何长于“3 倍(以厘米为单位)于上升时间(以 ns 为单位)或 1.18 倍(以英寸为单位)于上升时间(以 ns 为单位)”的走线都应该被视为传输线,再加上用于今天的高速信号的、以纳秒 (ns)/皮秒 (ps) 范围计算的上升/下降时间,您就会发现即使是短走线,最后也会象传输线一样工作。

封装走线、引线、PCB 走线、连接器和电缆都开始影响那些高速信号了。如果这些接口的阻抗设计和匹配得不当,可能会导致信号完整性问题,从而会影响到系统的性能和可靠性。

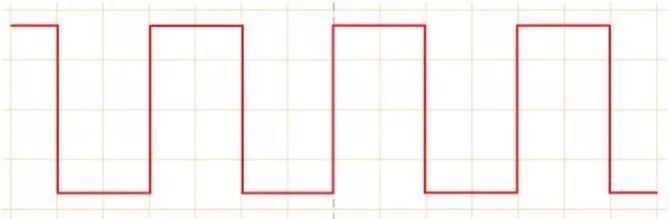

理想的数字信号

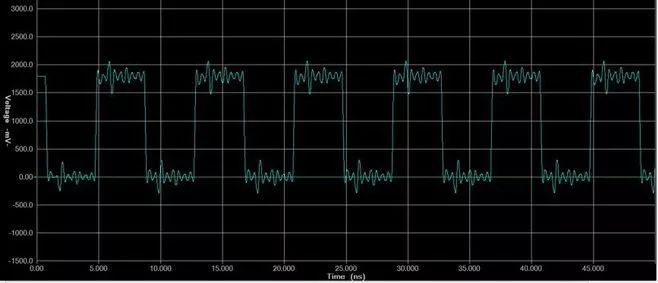

现实的数字信号

在上面的例子中,信号的模拟特性显而易见。如果没有恰当地考虑其影响,信号最终可能会出现过冲、下冲和毛刺,从而降低信号质量并影响器件的操作。

过冲会降低器件的可靠性,在极端情况下还会对器件造成不可逆转的损坏。下冲可能会引起相同的反向偏置,以及反向偏置基板,这会导致器件以从未打算操作的方式进行操作。

随着 PCB 技术以及可以具有微通孔、埋入式通孔和盲孔的高速 PCB 设计方面的进步,探测感兴趣的信号并对其进行调试已不再总是可行。结合更短的设计周期和更快的产品上市时间要求,硬件仿真(也被称为信号完整性仿真)不再是可选的选项了。为了在第一时间开发出设计恰当的产品并节省在实验室里调试有问题的 PCB 设计所需的大量成本和时间,它已成为不可或缺的要求。

在本系列课程中,我们会介绍与设计人员必须处理的高速 PCB 设计的各个方面相关的主题,并一起来了解硬件仿真如何有助于消除设计阶段的猜测。撰写本博客的目的是帮助设计人员在设计周期的早期捕获并解决问题。这比起在实验室里调试原型、经历多个布局周期,并花费宝贵的时间、金钱和精力要更经济、更有效。

Mentor Graphics Hyperlynx v9.4.2 是一个 SI 仿真工具,将在本系列中用作一个帮助描述各种概念的机制。Hyperlynx 只是市场上的一种 SI 工具,还有许多其他供应商提供的其他工具。无论使用哪种工具,本系列中涵盖的概念都保持不变。赛灵思对任何第三方 SI 工具均提供完美的支持,Hyperlynx 只是碰巧是本系列中用来详细说明所涵盖概念的工具。

SI 仿真模型

我们先来看看可用于 SI 仿真的各种模型、它们之间的差异,以及在运行 SI 仿真时人们首选的模型。

SPICE 模型:

SPICE 代表以集成电路为重点的仿真程序。顾名思义,模型设计得非常详细(详细到到晶体管级别和工艺参数)。这些模型非常准确且非常复杂。然而,由于电路是在晶体管级进行描述的(这是专有信息),并非所有器件供应商都将这些模型用于 SI 仿真。还有一个限制,即并非所有 SPICE 仿真器都完全兼容。

赛灵思提供加密的 HSPICE 模型(UltraScale +系列除外),而这种模型需要使用 Synopsys的HSPICE仿真工具进行运行。

IBIS 模型:

IBIS 代表 I/O 缓存信息规范,是用于使用纯 ASCII 文本格式数据描述数字器件缓存区的模拟行为的标准。这些是行为级模型,表示用于输入和输出的典型、最小和最大外壳角的 I/V 特性和 dV/dt。由于这些模型是没有显示适当数据的行为模型,所以他们是供应商发布的、用于模拟输入/输出 (IO) 的最流行的类型。它们还具有受所有 SI 工具支持的优势及其易用性。

快速浏览 IBIS 模型中的重要部分:

报头:包含模型的一般信息(诸如文件名、版本、源、注释等这类信息)

组件:将器件中所有不同的模型组织到引脚

模型:描述各种缓存区的驱动和接收器的特征

定义封装模型:描述器件的封装模型,并提供器件引脚的 RLC 矩阵

IBIS 规范 v6.1(最新版本)包含 IBIS 文件的各种语法和标题描述的详细描述,是了解 IBIS 模型的推荐文档。如需下载,请访问 http://ibis.org/。

下图对这两种模型进行了比较:

| IBIS Models | SPICE Models |

|

- Blackbox with no transistor level information. - Fast simulation speed. - Compatible with all simulation tools. - Lower accuracy compared to SPICE simulations. - Easily available from vendors. |

- Circuit level with propriety transistor level information. - Slow simulation speed. - Most simulation tools are not fully compatible. - Highly accurate. - Not easily available and may need NDA. |

赛灵思 IBIS 模型适用于所有器件,可以从这里。这些模型本质上是通用的,不会将特定的封装引脚映射到任何 I/O 标准模型。与 ASIC 不同的是,FPGA 是用户可编程的,除了少数专用引脚外,管脚是用户特定的。

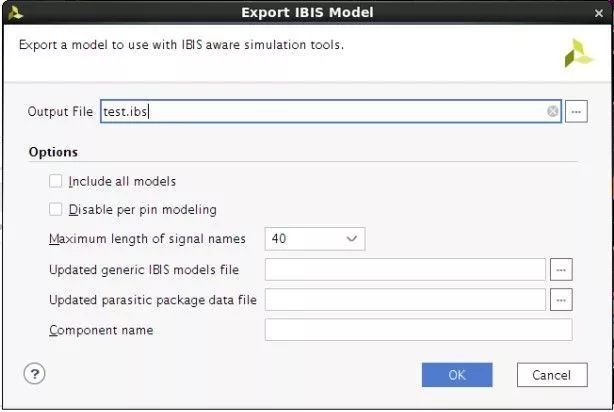

我们建议从 Vivado Design Suite 中获取 IBIS 模型(该套件允许您生成 IBIS 模型)。Vivado 使用设计中的网表和实现细节,并将该信息与可用的每引脚寄生封装信息相结合,为设计创建定制的 IBIS 模型。

请记住,仿真结果仅与所提供模型的质量一样好。从 Vivado 生成模型会为您提供一个映射到您的设计的 I/O 端口的 IBIS模型,以及完全不会出现错误的最佳机会。

以下是以下列用例为例从 Vivado 生成 IBIS 模型的步骤:

1.有 RTL 设计:

如果您有 RTL 设计,请按照以下步骤操作:

打开精心设计、综合或实现的设计。

要么 a) 单击“File -> Export -> Export IBIS Models”。

要么 b) 在 Tcl 控制台中使用以下语法运行“write_ibis”命令。

Write_ibis

Write IBIS models for current floorplan.

Syntax

write_ibis [-force] [-allmodels] [-nopin] [-truncate ] [ -component_name ] [-ibs ] [-pkg ] [-quiet] [-verbose]

2. 没有 RTL 设计:

如果您没有 RTL 设计并且计划使用管脚排列,请按照以下步骤操作。如果您不熟悉 I/O 管脚分配方面的详情,请参阅(UG899)。

- 打开 Vivado I/O Planning 工程。

- 选择器件。

- 通过 CSV 或 XDC 文件导入此管脚文件。如- 果没有可用的管脚,请选择“No I/O Ports at this time”选项。(注意:此选项将提供包含封装数据的通用 IBIS 模型。)

- 完成创建项目,系统随即会打开封装视图。

- 查看“I/O 端口”标签以确保已正确导入管脚。如果需要,运行 DRC。

- 要么 a) 单击“File -> Export -> Export IBIS Models”。(见方法1)

- 要么 b) 在 Tcl 控制台中使用以下语法运行“write_ibis”命令:(见方法1)

3. 基于 Zynq MPSoC 或 Zynq-7000 的设计:

如果只有 Zynq 器件的 PS 部分需要 IBIS 模型,您可以按照以下步骤操作:

- 在 Vivado 中启动新的 RTL 工程并选择目标 Zynq 器件和包。

- 准备好新项目后,在 IP 集成器中创建块设计。

- 单击“+”按钮在 IP 选择器窗口中添加 IP,并根据所选器件系列选择“Zynq UltraScale + MPSoC”或“Zynq7 Processing System”。

- 相应的基于 Zynq 的块将添加到图表窗口中。

- 双击 Zynq 块打开“Re-customize IP”窗口。在“Re-customize IP”窗口中,选择要在“Page Navigator”中设置的选项,并设置必要的参数,例如 I/O 配置、时钟配置、DDR 配置等。

- 单击“OK”,系统随即会更新 IP。右键单击 Zynq IP 块,然后单击“Make External”。Vivado 将自动添加到外部信号。

- 要避免收到有关未分配地址的警告,单击“Address Editor”窗口并单击“Auto Assign Address”。

- 在“Hierarchy”窗口中,单击“Sources”标签。右键单击设计,然后单击“Create HDL Wrapper”。

- 选择“Let Vivado manage wrapper”,然后单击“OK”。

- 当封装完成后,在 Flow Navigator 中选择“Open Elaborated Design”。系统随即会打开一个对话框,该对话框中列出了有关 Elaborated 设计的详细信息。单击“OK”,然后打开细化设计。

- 要么 a) 单击“File -> Export -> Export IBIS Models”。(见方法1)

- 要么 b) 在 Tcl 控制台中使用以下语法运行“write_ibis”命令:(见方法1)

S-参数模型:

请输入文字

过去,S 参数(散射参数的简称)在频域中使用得最为广泛。然而,随着今天的高速数字信号达到> 1 GHz 的速度,S 参数在 SI 仿真中被用作无源互连的行为模型,例如电阻器、电容器、PCB 走线、背、连接器、电缆等。

大多数连接器和电缆供应商提供其产品的 S 参数,可用于在 SI 仿真中对其进行建模(尤其是在对多板接口进行仿真时)。大多数 SI 工具支持将 S 参数模型与 IBIS 模型相结合,以对接口进行端到端的仿真。

运行 SI 仿真所需的模型列表合并在下图中。

| Transmitter (Tx) and Receiver (Rx) | IBIS Models |

| Lumped Elements (R, L, C) | Primitives within simulator or S-parameter from vendor if available. |

| PCB Traces | Transmission line primitive in simulator or S-parameter model if derived from a PCB layout file. |

| Connectors, Cables | S-Parameter models or IBIS models from the respective vendor. |

-

基于信号完整性分析的PCB设计解析2017-12-04 1185

-

高速PCB设计,信号完整性问题你一定要清楚!2024-04-07 161

-

高速PCB设计的信号完整性问题2012-10-17 0

-

基于信号完整性分析的高速PCB设计2015-01-07 0

-

高速PCB设计信号完整性问题形成原因是什么?2021-03-17 0

-

PowerPCB信号完整性整体设计分析2010-10-11 1989

-

PCB信号完整性有哪几步_如何确保PCB设计信号完整性2018-05-23 11020

-

高速PCB设计的信号完整性问题分析2019-06-18 667

-

识别和修复pcb信号完整性问题2019-10-12 2625

-

如何克服高速PCB设计中信号完整性问题?2020-09-17 2592

-

信号完整性问题与PCB设计2021-03-23 676

-

在PCB设计时有哪些点会导致信号完整性问题2022-09-29 1104

-

如何确保PCB设计信号完整性的方法2022-12-22 850

-

PCB设计中的信号完整性问题2023-11-08 437

-

分析高速数字PCB设计信号完整性解决方法2024-01-11 168

全部0条评论

快来发表一下你的评论吧 !