CPU和FPGA的机器视觉算法分割

描述

本篇讨论的是有关CPU(在Zynq SoC中是指ARM处理器核)和FPGA的可编程逻辑架构之间的机器视觉算法分割。

美国国家仪器公司(National Instruments)的Carlton Heard在新一期RTC杂志刚刚发表了一篇内容翔实的标题为《FPGA –将视觉技术提升至新高》的机器视觉处理方案文章,Heard写道:

“视觉应用程序必须依靠其他解决方案,而不是简单地依靠更快的处理器来提高速度。一种选择是分割图像处理算法,并行处理更多任务,在视觉应用程序当中使用的算法非常适合于这样处理。如SSE 、超线程和多核技术可以用于在不增加原始时钟速率的情况下并行处理、执行多个任务。不过,选择这种方法也需要处理多个问题。除非所使用的软件包将复杂性进行抽象化,否则难以使用多线程编程软件。必须在线程之间传送数据,这样会出现存储器拷贝和同步抖动。此外,它通常是一个手动过程,以利用现有的单线程图像处理算法,并兼容多内核。即使这样,开销问题往往禁止过多的并行处理,因为大多数系统设计人员无法为所创建的测试单元购买16内核服务器级计算机。”

“使用FPGA的好处在于,它基本上是由软件定义的硬件。因此,系统设计人员可以在软件芯片中编程,并且当该软件下载到FPGA,代码变成可根据需要重新编程的实际硬件。由于FPGA实际是并行设备,使用FPGA进行图像处理特别有利。可将算法分割运行数千种不同的通路,并能保持完全独立。虽然FPGA本身是非常适合许多视觉应用程序的,但系统中还存在很多因素不适合在FPGA上运行。评估是否要使用FPGA进行图像处理需要考虑多项因素。

“ FPGA处在处理图像时具有令人难以置信的低延时(微秒数量级)...当使用具有高速相机总线的FPGA,如不缓冲的图像数据的Camera Link,只要第一个像素自相机中发出,FPGA就可以处理图像,而不要等到整个图象读出已经完成后再处理。”

“ FPGA可以帮助避免抖动。因为 FPGA不会因为其他线程、操作系统或中断产生额外的开销, FPGA具有很好的确定性。对于许多图像处理算法来说,FPGA能够将所确定的执行时间精确到纳秒。”

Heard的文章延续了系统级功耗限制的讨论,这样的讨论有利于FPGA在视觉系统中的应用。

“一个FPGA可消耗1-10瓦的功率,而同样性能的CPU会轻易消耗50-200瓦。功耗较大,就必须消散大量的热量。在无风扇嵌入式应用程序中,这可能会造成更为复杂的大型机械设计。所以,在极端条件下如太空,空中和水下应用中,低功耗FPGA特别有用。”

Heard的文章列出了机器视觉的四个主要应用类别:

1、可视化

2、高速控制

3、图像预处理

4、协处理

•“可视化”,从相机拍摄图像并进行调整,以增强图像显示效果以适应人眼观看。在这种情况下,FPGA从相机读取图像,执行某些类型的并行处理,如突出显示边缘和关注功能或掩蔽功能。然后在FPGA直接输出图像至监视器或将其发送到主机CPU进行显示.....例如,使用医疗设备拍摄图像,提取细胞图像显示在监视器上供医生检查。FPGA可用于测量每个细胞的大小和颜色,并突出显示医生关注的特定细胞。

• 高速控制应用程序,采用已处理图像控制输出,以执行控制执行器等任务。“在这些应用中,捕获图像和执行操作之间的时间必须连续而且短暂,因此应优先使用具有低延迟和低抖动功能的FPGA。FPGA与视觉和I / O紧密集成可启用高级应用程序,如视觉伺服,视频数据被用于定位直接反馈并控制伺服电机。”

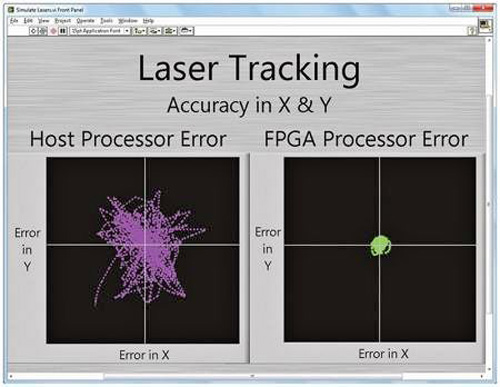

Heard的文章清楚地说明在激光跟踪中通过使用具有确定性的,低抖动的,基于FPGA视觉系统来显著减少错误(而不是使用基于CPU系统):

“FPGA非常适用于做空气成分分选,比如需要执行成像、检验和对正在下降的空气进行分选等。这类应用程序低抖动至关重要,因为必须要知道决策和I / O的时间间隔。”

“图像预处理、协同处理几乎相同,区别在于设备初始捕获图像......预处理图像时,图像数据遍历FPGA ,被修改或增强,然后FPGA将图像发送到主机以进行进一步处理和分析。协处理指图像数据自CPU还不是自相机发送到FPGA 。一旦捕获数据需要处理大量图像时这种情况是最常见的”

Heard的文章清楚地说明了美国国家仪器公司使用LabVIEW FPGA扩展了LabVIEW 图形开发平台,可加速复杂视觉处理系统开发:

“通常情况下,使用FPGA会增加设计的复杂度。硬件编程与传统软件编程的显著差异是一条复杂而不平凡的学习曲线。然而,高层次综合工具如LabVIEW FPGA的可用于将这些复杂度抽象化,设计师能够充分利用FPGA技术,不需要对VHDL编程有深入的了解。”

如果设计团队更熟悉其他类型的开发工具也可以采取其他方法。例如,如果开发团队非常熟悉采用高级编程语言的C和C + +、Xilinx Vivado HLS (高层次综合)编码视觉系统可在 Xilinx 7 系列 All Programmable 器件 和 Zynq All Programmable SoC利用这些语言编译将这些算法编写成硬件描述。

许多视觉系统开发团队所熟悉的其他种类的视觉专用开发工具,如MVTec的综合开发软件HALCON 和Silicon Software Visual Applets图形设计工具。这些工具也可以针对Xilinx All Programmable器件,使用低功耗可编程硬件提高视觉性能,而无需学习新的设计风格。

-

基于FPGA的机器视觉设计2013-09-04 0

-

FPGA综合算法2015-01-15 0

-

机器视觉算法与应用(双语版)2016-06-29 0

-

【下载】《机器人学、机器视觉与控制――MATLAB算法基础》2018-01-17 0

-

以FPGA为核心的机器视觉系统设计方案2019-05-05 0

-

机器人视觉系统组成及定位算法分析2019-06-08 0

-

照明对机器视觉应用有什么影响?2019-08-02 0

-

机器视觉系统应用于标签外观视觉检查!2019-11-18 0

-

深圳机器视觉led光源有什么优势2021-01-11 0

-

CPU和FPGA的机器视觉算法分割2021-05-31 0

-

基于机器视觉的色差检测算法_范鹏飞2017-03-19 787

-

视觉显著性目标分割提取2017-12-06 660

-

机器视觉应用,CPU还是FPGA?资料下载2021-03-29 532

-

什么叫机器视觉?机器视觉和嵌入式有什么关系?2023-08-07 715

全部0条评论

快来发表一下你的评论吧 !