DDR4伪漏极开路驱动器及对接收器的功耗和Vref电平而言的意义

电子说

1.4w人已加入

描述

本文最初于 DesignCon 大会上发表并获得了最佳论文奖提名,其中研究了DDR4 的伪漏极开路驱动器,以及其使用对接收器的功耗和 Vref 电平而言的意义。

DDR4 是 JEDEC DRAM 部件系列的下一阶段,旨在满足市场对更高速度和更低功耗的需求。这些因素构成了 DDR4 的新特性以及设计 DDR4 系统时需要予以考虑的新要求。

相比以前的 DDR 技术,新的 DDR4 标准除了数据速率更快以外,还包含其他变化,而这些变化将会对电路板设计工程师产生影响。DDR4 中的新因素,例如不对称端接方案、数据总线反转和利用眼图模板验证信号等,都需要通过仿真验证设计的新方法。

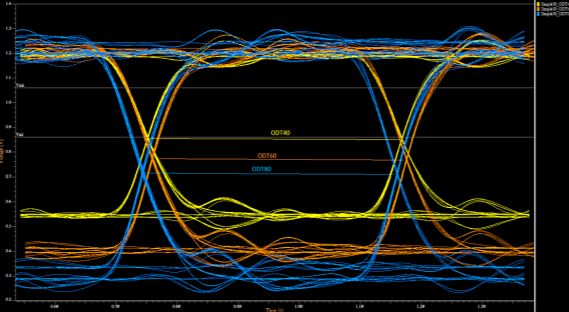

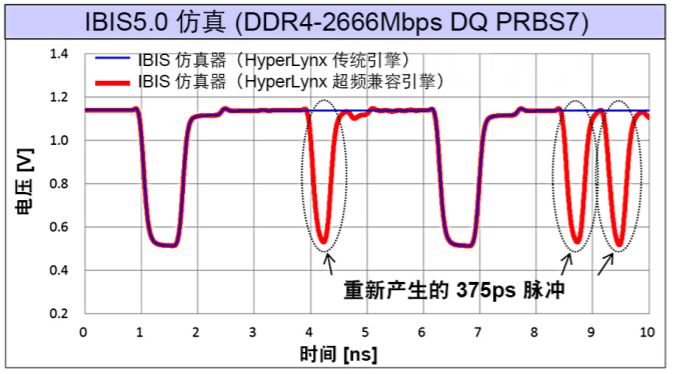

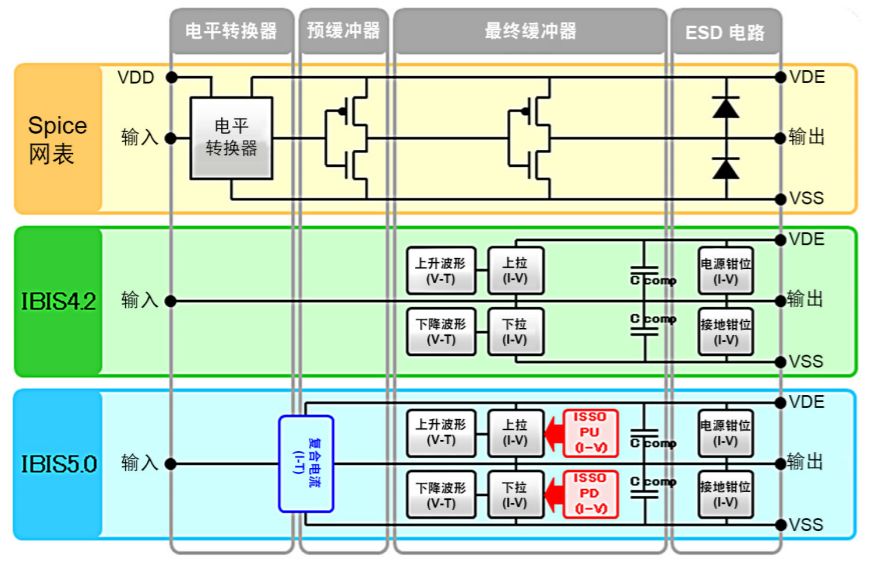

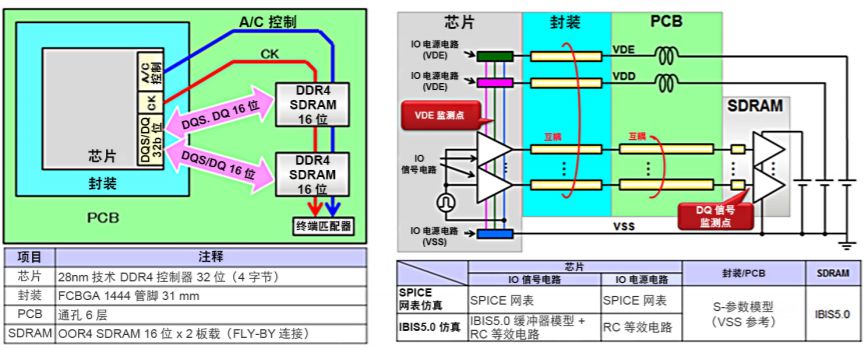

本文研究了 DDR4 伪漏极开路 (POD) 驱动器对数据总线信号传输的影响,并介绍了动态计算 DRAM 内部 VrefDQ 电平以进行数据眼图分析的方法论,生成和验证数据眼图的方法论,以及将写入均衡和校准整合到仿真中的方法。此外,通过将电源完整性效应纳入信号完整性分析来评估同步开关噪声 (SSN),对于电路板设计和时序收敛也很重要,本文将借助示例加以阐述。本文还将描述一个采用 IBIS 5.0 功耗分析模型的系统设计示例,其中包括比较了 IBIS 结果与晶体管级模型以研究仿真精度。风,毫无预兆地席卷整片旷野,撩动人的思绪万千。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

将 LVDS 驱动器与 Sub-LVDS 接收器对接应用说明2024-09-13 959

-

低功耗差动线路驱动器和接收器对数据表2024-06-21 531

-

漏极开路输出的十六进制反相器缓冲器/驱动器SN74LVC06A数据表2024-05-31 461

-

漏极开路输出的三重逆变器缓冲器/驱动器数据表2024-05-21 501

-

具有漏极开路输出的 SN74AUP2G07低功耗双路缓冲器/驱动器数据表2024-04-30 435

-

8位双向多电压电平转换器;漏极开路;推拉-LSF01082023-02-20 523

-

4位双向多电压电平转换器;漏极开路;推拉-LSF02042023-02-17 676

-

2位双向多电压电平转换器;漏极开路;推拉-NCA93062023-02-15 561

-

1位双向多电压电平转换器;漏极开路;推拉-LSF01012023-02-10 586

-

2位双向多电压电平转换器;漏极开路;推拉-LSF01022023-02-09 591

-

介绍DDR3和DDR4的write leveling以及DBI功能2022-12-16 3959

-

如何使DDR4降低系统功耗?要借助POD电平2018-07-27 18836

-

怎样降低DDR4系统功耗2017-10-13 2065

-

驱动器/接收器,驱动器/接收器原理是什么?2010-03-08 2230

全部0条评论

快来发表一下你的评论吧 !