使用EDA设计射频模拟电路的一些知识点详细说明

描述

集成电路自1958年问世以来至现在,其工艺节点已经从10微米发展到3纳米。集成电路又可分为数字集成电路、模拟集成电路和数/模混合集成电路。因为设计流程,生产工艺的不同,数字集成电路和模拟集成电路呈现了两种截然不同的发展情况。

这几十年来,数字集成电路的集成化程度越来越高。以英特尔为例,自从1975年,其创始人戈登摩尔发表了摩尔定律以后的几十年里,英特尔的研究人员一直以来都根据摩尔定律设定目标和指标。在摩尔定律的指导下,计算机集成电路芯片变得越来越小,运算速度却越来越快。

摩尔定律

英特尔在1971年开发了第一个商用处理器Intel 4004,片内集成了2300个晶体管,采用五层设计、10微米制程,能够处理4bit的数据,每秒运算6万次。经历了几十年的发展,如今的处理器已经到达10nm制程工艺,最高可配置48颗核心,以英特尔在2019年最新发布的i9-9980HK为例,能够处理64bit的数据,CPU主频可高达5GHz。

Intel 4004

数字集成电路的迅速发展推动了EDA工具的自动化发展历史。EDA(Electronic Design Automation)工具从20世纪60年代出现,一直到20世纪80年代,设计方法发生了很大的变化。

CAD(Computer-aided Design)是20世纪70年代的技术,可以称作是第一代EDA工具,其主要功能是交互图形编辑,设计规则检查,解决晶体管级版图设计、PCB布局布线、门级电路模拟和测试;

20世纪80年代进入到CAE(Computer-aided Engineering)阶段,由于集成电路规模的逐步扩大和电子系统的日趋复杂,人们进一步开发设计软件,将各个CAD工具集成为系统,从而加强了电路功能设计和结构设计功能。

20世纪90年代以后微电子技术突飞猛进,一个芯片上可以集成几百万、几千万乃至上亿个晶体管,这给EDA技术提出了更高的要求,也促进了EDA技术的大发展。各公司相继开发出了大规模的EDA软件系统,这时就出现了以高级语言描述、系统级仿真和综合技术为特征的EDA技术。

随着近年来智能手机、5G、物联网等技术的发展,模拟集成电路,尤其是射频集成电路越来越被大家重视。但是,相比于数字集成电路的迅猛发展,模拟射频集成电路的技术进步较为缓慢,其设计设计难度也非常高。

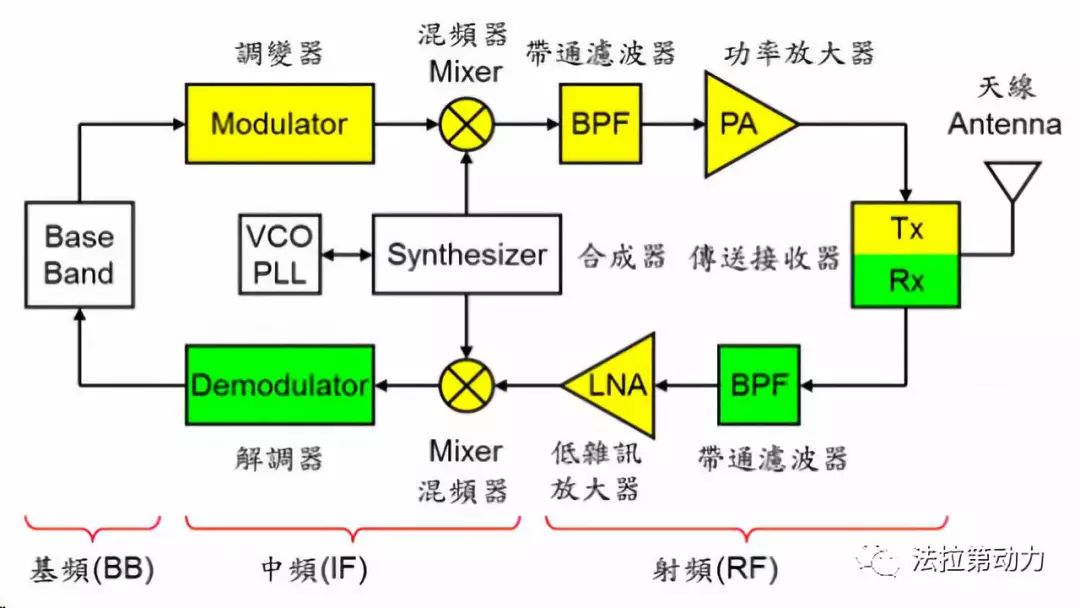

无线通信系统框架

这主要是因为高频电路中存在大量的寄生效应、串扰等因素。模拟集成电路从平面图纸变成实际电路的过程中,需要严格依靠设计师的丰富经验。如何布局、如何消除元件之间的各种负面的影响,兼容不理想的元件,都需要依靠设计师手工来解决。造成此现象的重要原因之一,就是缺乏很好的EDA工具作为支撑。

那么,在没有好的EDA工具支持的情况下,设计工程师是如何来解决这些问题呢?通常的做法是在设计时将设计余量留大,比如本来可以靠得很近的两条走线拉得比较远,这样就能使芯片工作,但会增加芯片的面积;或者使用降频的方式,比如本来在2GHz工作的芯片,降到1GHz看看是否工作,如果1GHz还是不工作,那再降到500MHz可能就工作了,但这样芯片的实际工作频率只有500MHz,就会损失了芯片的性能。

总的来说,随着各种通信制式的迅猛发展,无线设备工作频率不断提升,高频芯片设计的难度也不断增大。

现阶段,一般的电路级仿真已经无法准确表述芯片内部真实的场分布情况,为了得到准确的仿真结果,使用全波三维电磁场算法对芯片进行仿真是一种非常有效的手段。但是,目前市面上存在的普通仿真软件无法完成高复杂度版图的仿真任务。常用的射频仿真工具要求使用者必须具备坚实的电磁场理论基础,否则无法进行准确的建模和设置正确的边界条件,上述技术要求让大部分电路设计师望而却步。另外,在高频时或者处理多层电路版图时,常用的射频仿真工具的计算复杂度很高,这导致运算速度非常慢。

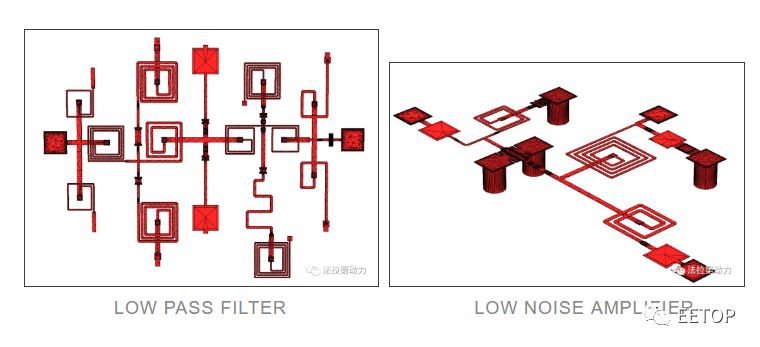

为了解决这些问题,许多人致力于开发新型的仿真工具,如三维全波电磁仿真工具UltraEM。该软件用于仿真射频芯片中的无源器件,它不仅使用了全波电磁场分析来保证计算精度,而且解决了全波分析致命的计算复杂度高的缺陷。

图 低通滤波器和低噪声放大器

此外,UltraEM结合另外一款系统级自动优化工具Circuit Compiler,可以极大地提高射频芯片设计领域的自动化程度,增加流片成功率。

UltraEM:三维全波电磁仿真软件,用于仿真射频芯片中的无源器件,如下图显示的低通滤波器和低噪声放大器。

Circuit Compiler: 用于系统级的电路自动优化平台,可以支持三种类型的器件模型输入,分别是S参数模型、AI模型、集总元件模型(如下图)。由这些器件连接成的电路系统,可以进行目标优化,并给出最终优化完的电路。

-

介绍一些基础的电力知识点2023-08-15 2608

-

高速电路设计常见的知识点2023-02-13 2374

-

详解射频微波基础知识点2023-01-29 3511

-

一些小众的C语言知识点2022-09-26 1157

-

Verilog设计过程中的一些经验与知识点2022-03-15 3232

-

机智云入门知识点2021-12-07 825

-

记录一些飞控开发过程的知识点2021-08-09 1160

-

APT触摸布局的一些建议详细说明2020-10-27 1410

-

Python的知识点总结详细说明2020-09-29 1677

-

LLC的基本原理和设计方法设计步骤及一些问题详细说明2020-03-18 1654

-

射频的基础知识培训教程详细说明2020-03-14 2226

-

DSP入门学习必看的一些知识点详细概述2019-11-01 1818

-

通信协议的一些相关知识点资料合集免费下载2019-06-04 1453

-

关于红外通信的一些问题知识点2016-05-05 1068

全部0条评论

快来发表一下你的评论吧 !