FPGA开发中如何对整个设计添加时序约束

描述

什么是静态时序分析?

通俗来说:在输入信号到输出信号中,因为经过的传输路径、寄存器、门电路等器件的时间,这个时间就是时序。开发工具不知道我们路径上的要求,我们通过时序约束来告诉开发工具,根据要求,重新规划,从而实现我们的时序要求,达到时序的收敛。

我们对整个设计添加时序约束,让整个设计。

时序的欠约束:约束的少了;

时序的过约束:约束了过了;

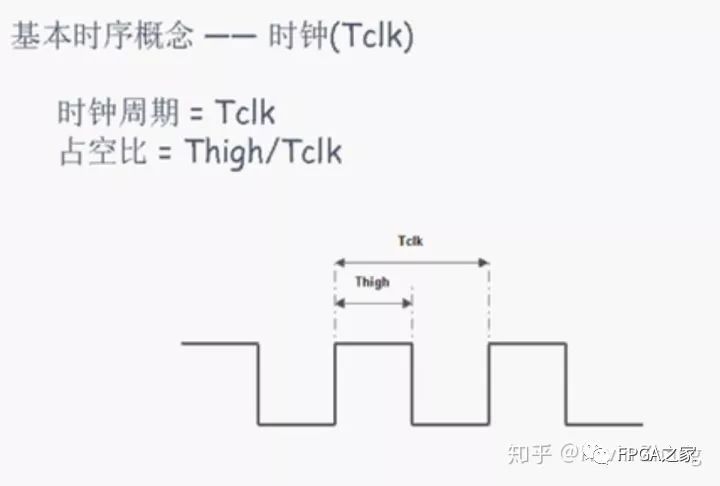

时序基本概念:时钟

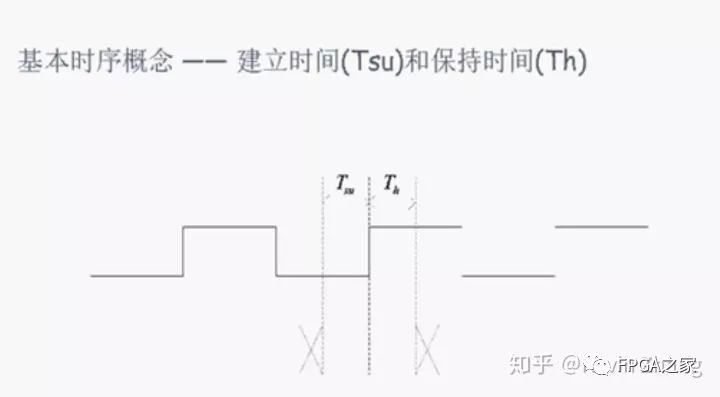

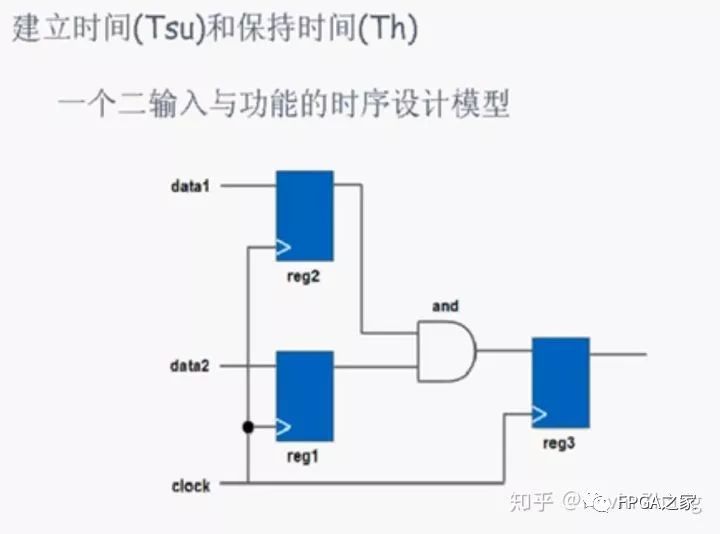

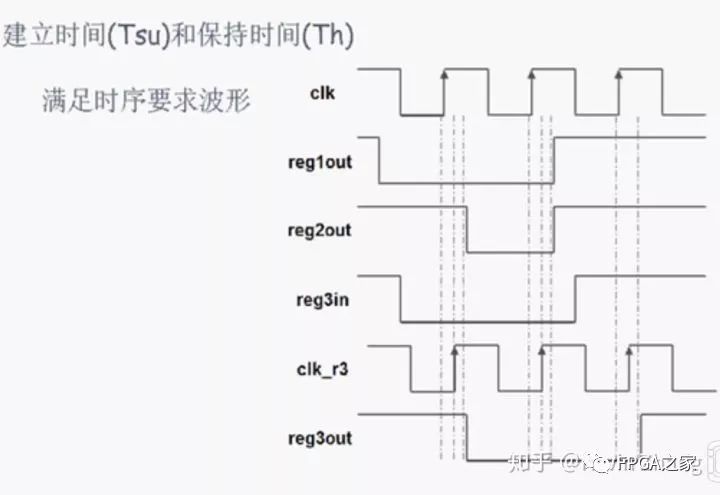

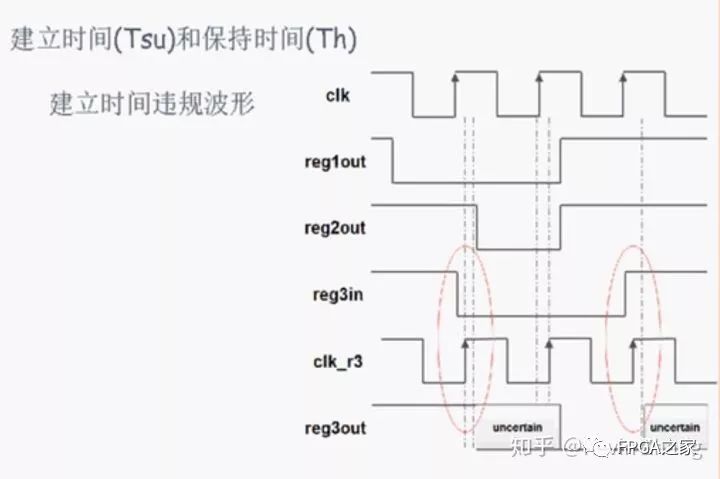

建立时间setup和保持时间hold

建立时间:在时钟上升沿前,数据不能改变的最小时间;

保持时间:在数据上升沿后,数据不能改变的最小时间;

例子

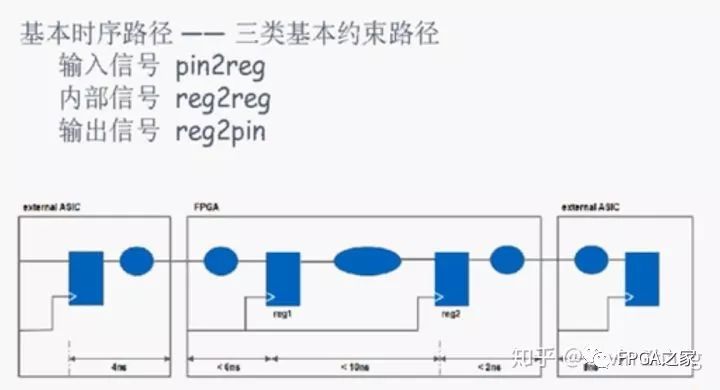

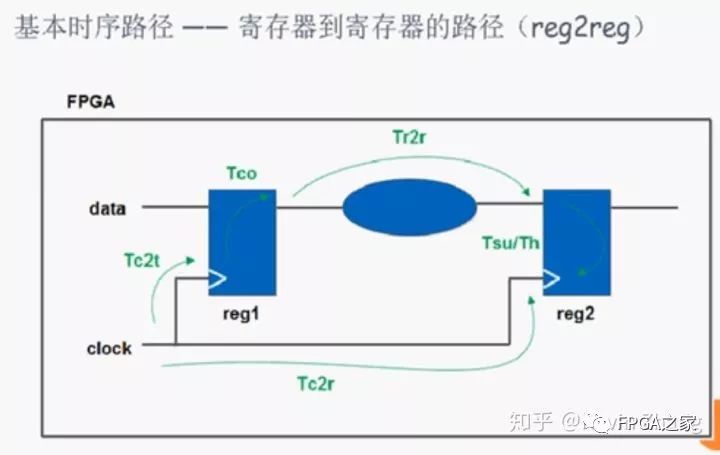

三种时序路径

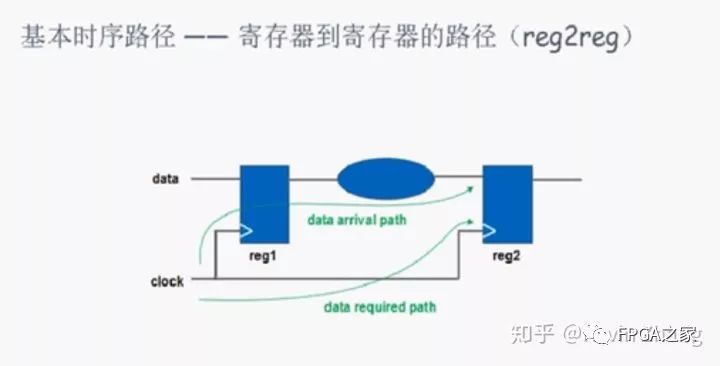

分析一个寄存器的延时

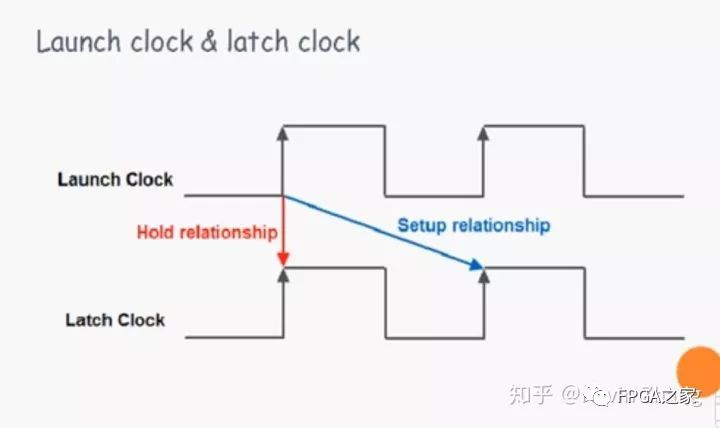

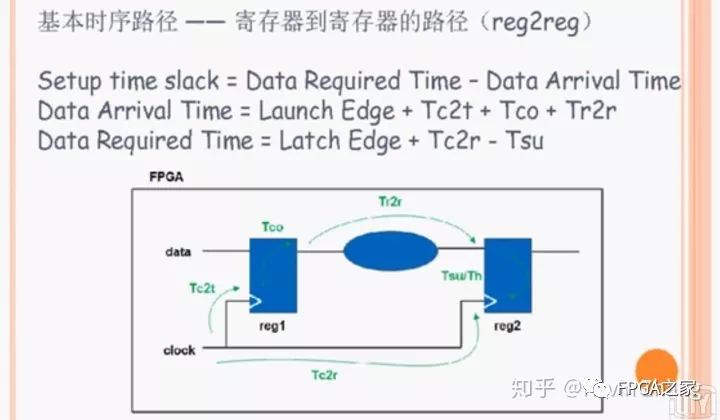

setup slack余量,这个时间是差了一个时钟周期;

数据达到时间,首先是发射时钟+时钟到REG1的延时+reg1的延时+传输路径的延时

数据时间需求:锁存时钟+时钟到reg2的延时-setup时间

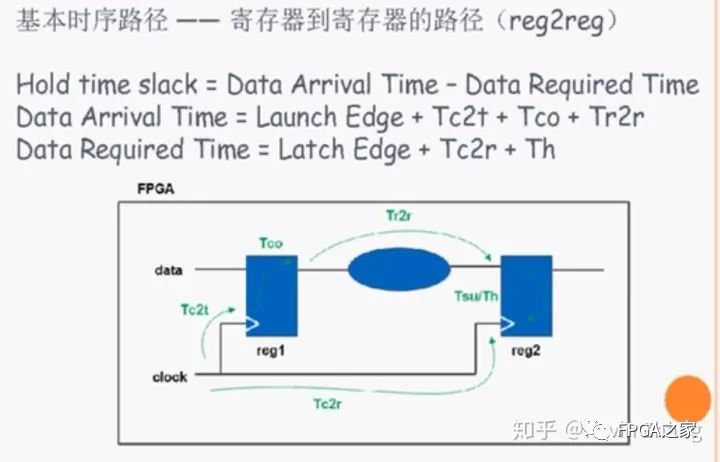

hold时间余量,这里分析的应该是同一个周期里面的时间,这个时间是对齐的;

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

深度解析FPGA中的时序约束2024-08-06 2819

-

FPGA I/O口时序约束讲解2023-08-14 3233

-

FPGA时序约束的原理是什么?2023-06-26 1391

-

如何在Vivado中添加时序约束2023-06-23 4432

-

FPGA时序约束之衍生时钟约束和时钟分组约束2023-06-12 4490

-

FPGA时序约束的基础知识2023-06-06 2066

-

FPGA的IO口时序约束分析2022-09-27 2529

-

FPGA设计之时序约束2022-03-18 2346

-

FPGA时序分析如何添加其他约束2019-03-18 2469

-

添加时序约束的技巧分析2017-11-25 3229

-

FPGA中的时序约束设计2017-11-17 3090

-

FPGA开发之时序约束(周期约束)2017-02-09 941

-

FPGA时序约束方法2015-12-14 1005

全部0条评论

快来发表一下你的评论吧 !