关于先进节点和特殊应用下的On-chip ESD 研讨会的分析和介绍

描述

5月23日,在张江举办了一场2个小时的研讨会,主题是On-chip ESD,演讲者由在on-chip ESD 领域耕耘了近20年的Sofics以及两个合作伙伴Moortec 和 HHGRACE 共同分享最新项目成果和合作的点点滴滴。 On-chip ESD 虽然是小众方向,但是不能缺少,因为ESD的HBM,MM,CDM不容易仿真,一定要等芯片出来后做了测试才知道结果,所以一旦失败,整个芯片的研发周期会拖延,造成比较大的损失。当然,对于高速电路这块的应用,ESD在寄生电容,电阻,这块的性能通过仿真可以获得,对于物联网等超低功耗的应用,ESD的漏电性能还是提前可以获得的,所以对于以上的应用,如果最基础的性能都没有达标,就需要寻找好的解决方案,特别在先进节点16nm,12nm, 7nm, 流片昂贵的时代,ESD 一次成功显得尤为重要。

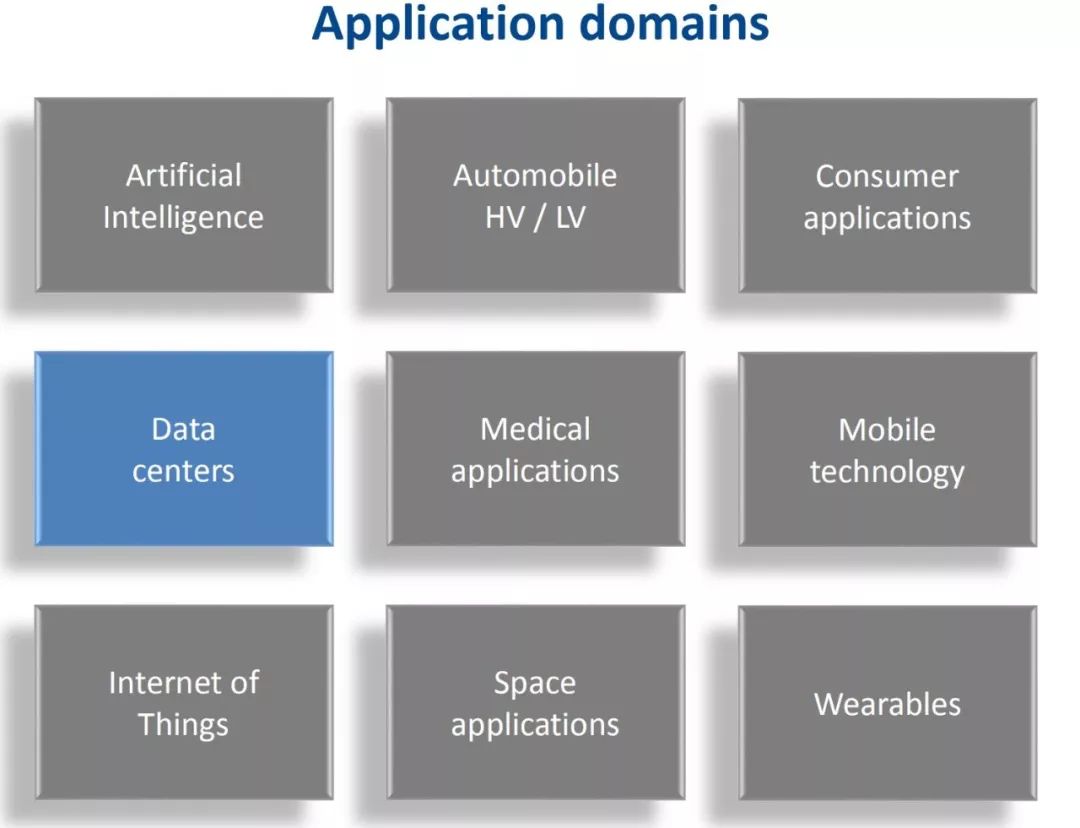

Sofics 的演讲非常接近应用,主要介绍了在人工智能、汽车电子,消费应用、大数据、医疗应用、移动应用、物联网、太空应用、可穿戴等方面的案例。

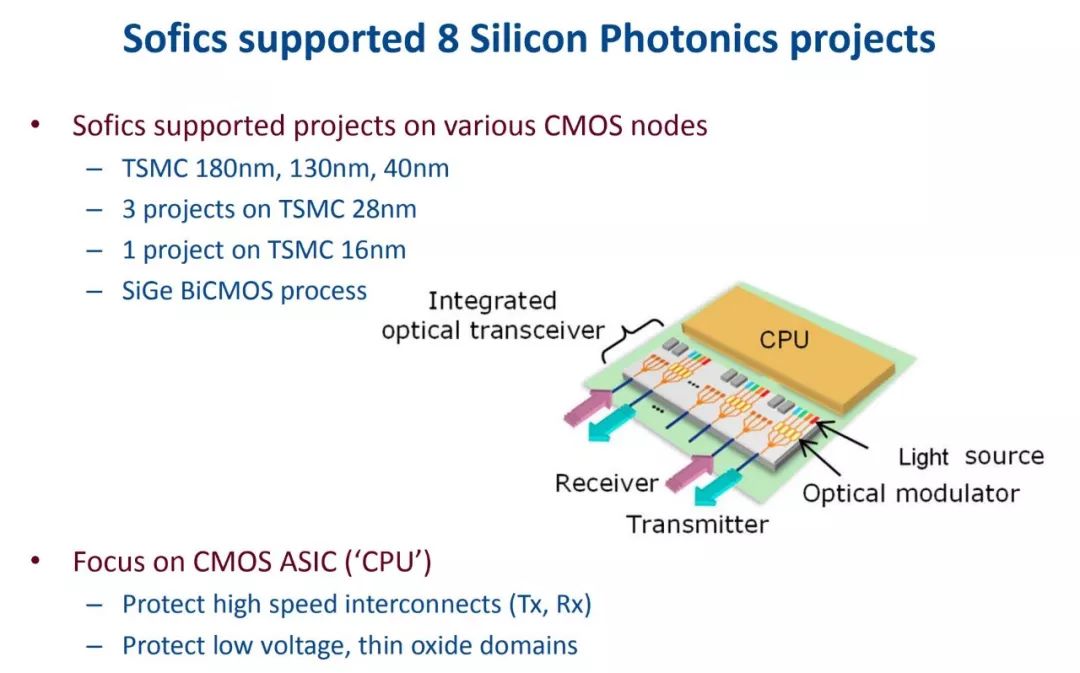

在高速传输这块的应用,基本都是先进节点(28,16,7nm),大数据,硅光电等很多IO接口都有非常高的SPEC要求, 比如寄生电容,Sofics 已经实现20fF 以下,在PAD中没有引入ESD电阻等。

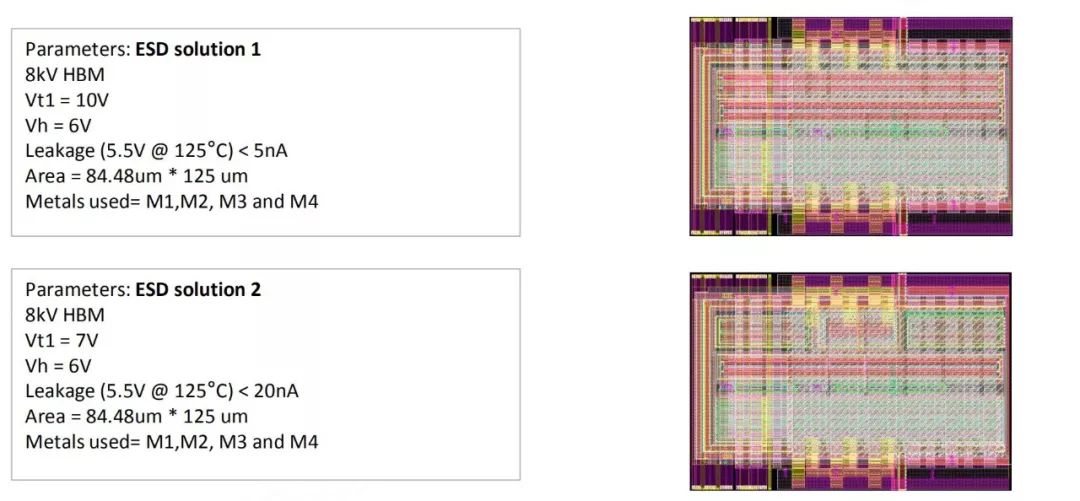

在和HHGRACE合作的在0.11um e-flash 平台中,实现了超低功耗的ESD解决方案,为后续IOT的应用,提供了非常好的解决方案。其中HBM性能>8keV, 总体漏电小于20 nA,5nA (5.5V, 125 degree) 也显示了双方合作的完美。

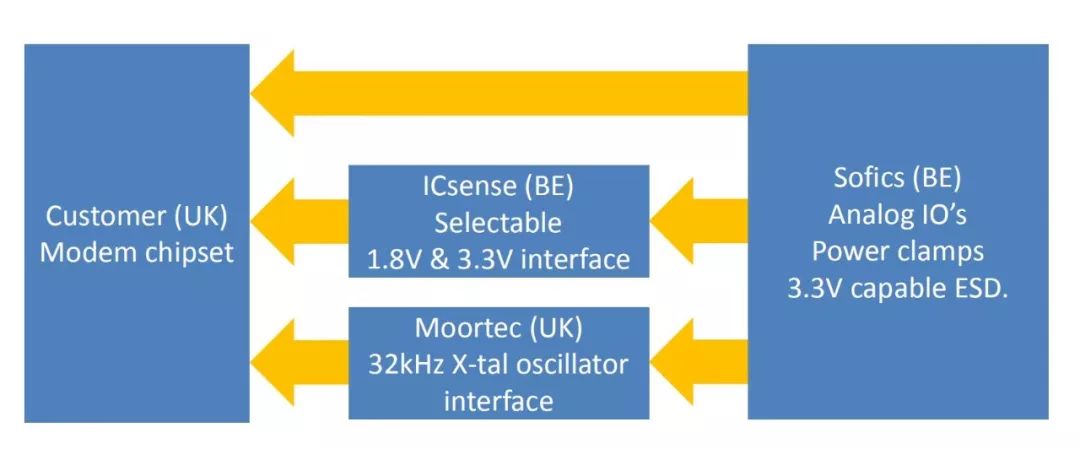

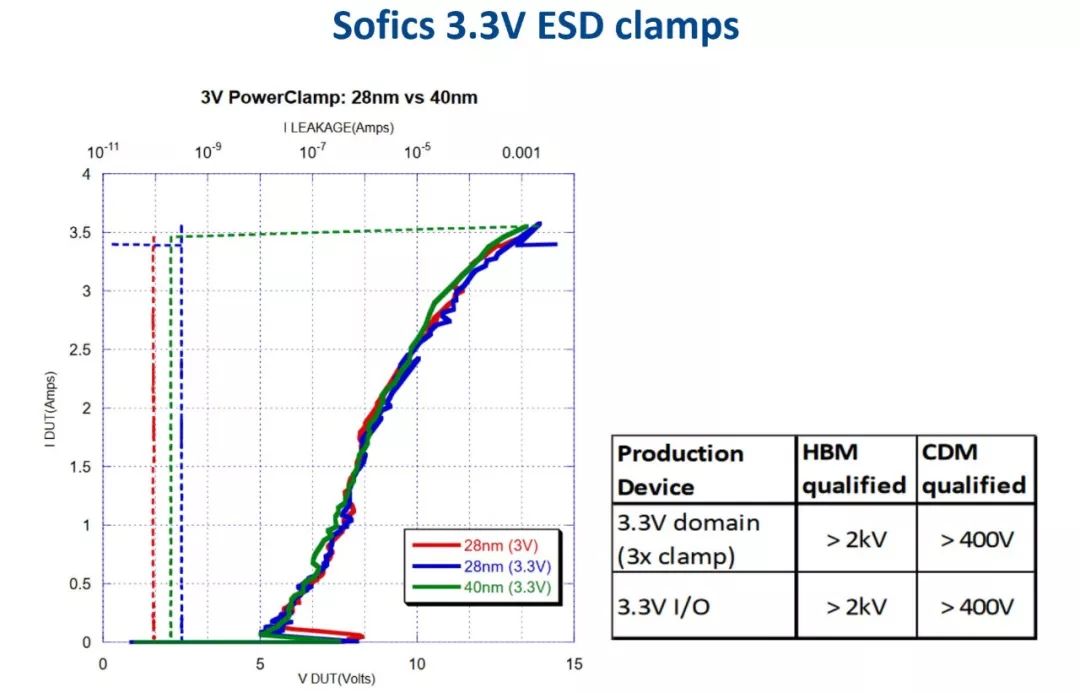

在和英国IP 供应商Moortec,和Icsense三方的合作中,Sofics 成功得在28nm, 1.8V 工作电压的工艺下,实现 3.3V ESD clamp, 让超压IO输出变成了可能,特别对那些设计公司,想在设计电路中,实现工作电压只有0.85V到1.8V的MOSFET器件做超压输出的,给了一个非常好的方向和选择。

虽然研讨会只有2个小时,会后,大家讨论得非常热烈,也非常希望国内有一个好的ESD信息共享的平台,因为只有国内外多交流,才能知道差距,互相学习,实现最终超越。 XMOD作为研讨会的组织者,也希望把欧洲更多小而美的公司技术资源转移落地到国内,相信,通过一个个小的技术点差距的弥补,能像星星之火一样,最终帮助到国内半导体产业链的发展。关于研讨会的演讲资料,如果感兴趣的,可以留言或者私信,在经过作者允许后,后续上传公司网站,分享给大家。

微信热点文章:

1. MOS-AK Peking 器件模型国际会议日程&邀请函

2. 射频测试&建模培训-(MOS-AK PEKING)

3. 写在中兴通讯被制裁之际

4. 122GHz雷达套装系统和芯片

5. TESTCHIP的设计

6. On-chip ESD 资源共享

-

【华秋研讨会】这场研讨会硬件工程师不要错过2023-10-27 1518

-

关于硅光电应用下的on-chip ESD的性能分析和介绍2019-09-09 3141

-

关于AI背景下的on-chip ESD (静电保护)需求分析和应用2019-09-08 3332

-

技术研讨会手册2019-06-24 1532

-

斯德哥尔摩的英特尔物联网商业研讨会2018-11-01 3788

-

TI MCU设计研讨会:产品的市场情况介绍2018-08-23 2888

-

【TI 研讨会】TI DLP® 创新显示应用研讨会火热报名中!!!2018-06-23 1912

-

2015 Cadence新技术研讨会2015-05-19 4552

-

一博全国技术研讨会——武汉研讨会召开在即2014-04-01 4316

-

先进无线通讯设计验证研讨会2010-07-25 512

-

先进多媒体标准研讨会2010-06-29 511

-

汽车零部件系列技术研讨会暨采购配对会2009-08-28 3788

-

On-Chip ESD Protection for Int2009-07-18 594

全部0条评论

快来发表一下你的评论吧 !