关于静电保护(ESD) 中的CDM需求的发和应用

描述

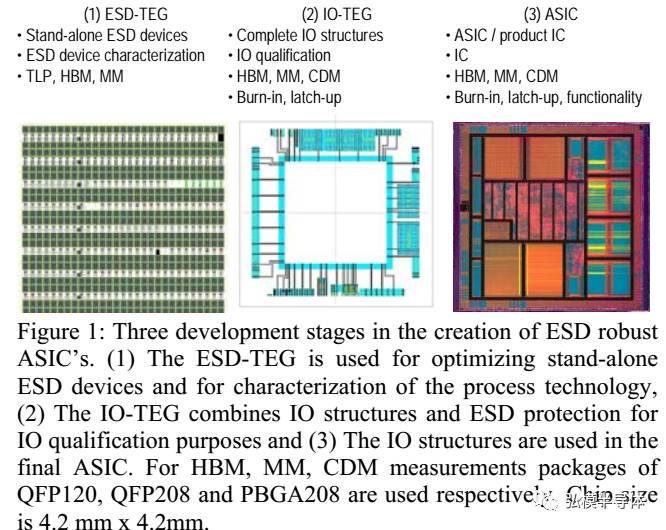

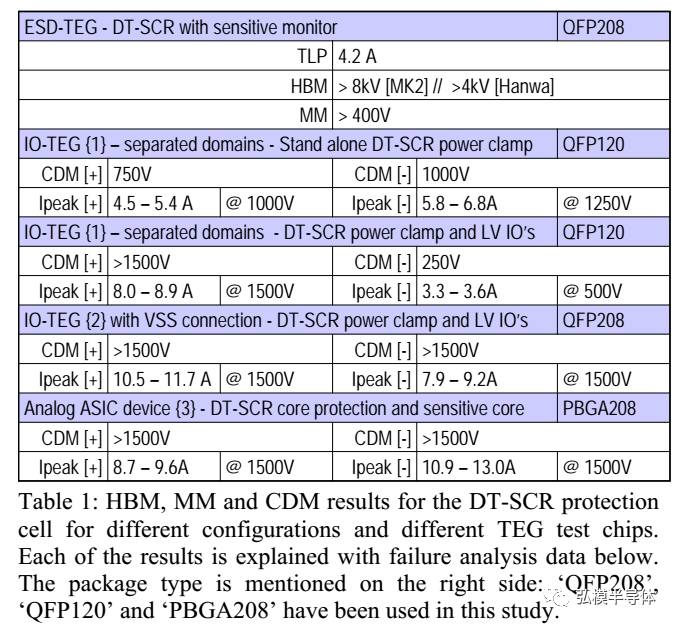

和on-chip ESD 中的HBM,MM不同,CDM的指标与IC layout ,封装,BONDING TYPE强相关。 因此很多IC公司会在一个测试芯片上,制作一个和实际产品相近的IC IO RING来选择最优的CDM方案。随着技术节点的减小和面对各种新型消费,工业产品,对ESD的要求变得更多样和更强大。 特别重要的是,first-time-right IC release对设计公司来说,越来越迫切,在这里,我们引用SOFICS的一些文章来介绍在CDM这块和设计公司共同合作的成果。 比如下面的这篇文章讲述了在引用了公司的ESD结构,在富士通的工艺线上的IO TESTCHIP上做不同的实验后,共同验证了对于CDM的性能影响是多方面的。

在这些不同的测试让我们得到以下结论,在同样的on-chip ESD 结构下:

DT-SCR ESD 结构在LV IO DOMAIN 里面还是外面有比较大影响

2. 通过低电阻的VSS和SUBSTRATE相连,可以大幅提高器件CDM 性能

3. 使用低电阻的衬底也会大大改善CDM性能

4. 单单通过IO TESTCHIP CDM测试,会误判内部核心器件的静电保护能力

更多此类的文章可以参考:

公司在on-chip ESD 领域给客户提供私人定制的需求,比如高速,高压,超低功耗等等,工艺覆盖所有半导体厂主流工艺并且IP转移非常方便。在给客户解决ESD和IO 方面问题的同时,帮助客户省芯片面积,省MASK,提高性能和TIME-TO-MARKET。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

ESD静电保护器的选型及应用2016-05-26 2778

-

如何正确的选择ESD静电保护器件?2017-06-27 5712

-

ESD静电保护器件的特点2018-01-26 4902

-

ESD保护二极管,一种有效的ESD静电保护器件2018-10-30 3204

-

选择ESD静电保护元件的参考因素2020-12-15 2969

-

HDMI接口静电保护解决方案2020-12-31 5237

-

一种常见的ESD静电保护器件2021-03-11 3266

-

ESD静电保护:ESD电容2018-08-10 11266

-

ESD静电保护器在Microphone接口的保护应用2021-12-09 1565

-

ESD静电保护器的作用是怎样的2022-06-06 3299

-

ESD静电保护芯片二极管2022-03-30 3405

-

ESD静电保护管的工作原理2022-09-22 8364

-

静电保护器件ESD是什么?如何选型?2023-02-27 7831

-

K课堂丨ESD静电保护管的工作原理2023-06-05 3667

-

物联网中常见的静电保护电路设计方案_ESD静电保护管2024-09-29 2156

全部0条评论

快来发表一下你的评论吧 !