关于制作一个18W全兼容快充移动电源的方法分析介绍

描述

随着智能手机的普及,这年头出门不带一个移动电源心里好没安全感。在手机急着充电的时刻,突然发现自己的移动电源跟手机不兼容,或者充电速度巨慢,估计整个人要崩溃。这时候要是有一个兼容各种手机且充电速度快的移动电源,分分钟解决你的困境。今天咱们就来讨论一下关于18W全兼容快充移动电源方案。

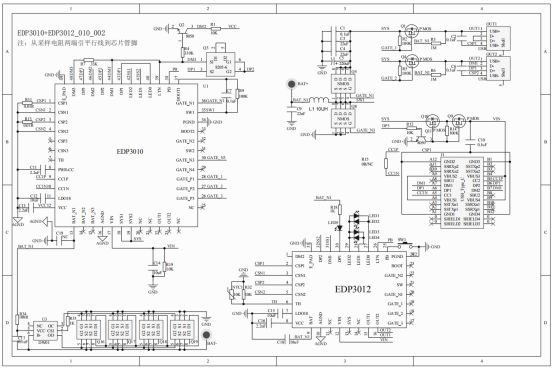

18W全兼容快充移动电源方案基于移动电源SOC芯片EDP3010+EDP3012,由芯片厂商易能微电子出品。

EDP3010+EDP3012全兼容下列快充协议:QC/PE/AFC/FCP/SCP/VOOC。

快充移动电源方案用一颗芯片完成了DC-DC升降压和快充协议,方案集成度高,外围原件少,热效率非常优秀,18W时最低效率超过90%.元件温度低于70℃。支持BC1.2、DCP、QC2.0/3.0、PE1.0、AFC、FCP、SCP、VOOC、Apple 2.4A输入输出双向快充协议。测试了市场上100多款几乎囊括了所有快充协议的手机,兼容性几乎做到100%.具有完善的电池充放电管理,独立的锂电保护电路,支持过压/欠压,过流,反向电流,短路,高低温保护等功能。安全性高,可靠性好,生产简单,是当前市场上快充协议最全,兼容性最好的快充移动电源方案。

应用范围

EDP3010:多串PD快充移动电源、车充、适配器

EDP3012:快充移动电源、快充车充、智能排插

1BOM物料清单

| EDP3010+EDP3012(AAC)物料清单 | ||||

| No. | 名称 | 规格 | 位号 | 用量 |

| 1 | 主控芯片 | EDP3010 QFN48 | U1 | 1 |

| 2 | 主控芯片 | EDP3012 QFN32 | U2 | 1 |

| 3 | 贴片电阻 | 0.01R 1%1206 | R11 R13 | 2 |

| 4 | 0R 5%0603 | R15 | 0 | |

| 5 | 100R 5%0603 | R34 | 1 | |

| 6 | 1K 5%0603 | R18 R35 | 2 | |

| 7 | 10K 5%0603 | R1 R12 R19 R32 | 4 | |

| 8 | 33K 5%0603 | R7 | 1 | |

| 9 | 100K 5%0603 | R2 R5 R9 R14 | 4 | |

| 10 | 330K 5%0603 | R4 | 1 | |

| 11 | 1M 5%0603 | R3 R6 | 2 | |

| 12 | 10K NTC | NTC1 | 1 | |

| 13 | 0.1uF/50V 10%0603 | C1 C2 C6 C7 C10 C17 | 6 | |

| 14 | 2.2uF/16V 10%0603 | C11 C13 C16 | 3 | |

| 15 | 10uF/25V 10%0805 | C12 C14 C15 C18 | 4 | |

| 16 | 10uF/25V 10%0805 | C19 | 0 | |

| 17 | 22uF/25V 10%0805 | C3 C4 C9 | 3 | |

| 18 | 电解电容 | 220uF/25V 10% | C5 | 1 |

| 19 | 电感 | 3.3uH | L1 | 1 |

| 20 | MOS管 | DTS2319 SOT-23 | Q1 Q4 Q9 Q10 | 4 |

| 21 | FS8205 SOT-23-6 | Q3 | 1 | |

| 22 | TDM3526 DFN3.3*3.3 | Q5 Q8 | 2 | |

| 23 | FS8205 TSSOP8 | Q16 Q17 Q18 Q19 | 4 | |

| 24 | 三极管 | NPN 8050 SOT-23 | Q2 Q11 | 2 |

| 25 | 电量指示灯 | LED 0603 | LED1 LED2 LED3 LED4 | 4 |

| 26 | 快充指示灯 | LED 0603 | LED5 | 1 |

| 27 | USB-A母座 | USB-A母座 | OUT1 OUT2 | 2 |

| 28 | USB-C母座 | USB-C母座 | J1 | 1 |

| 29 | 按键 | SW | SW1 | 1 |

| 30 | 电池接口 | Power BAT-2.54 | BAT-BAT+ | 2 |

| 31 | 锂保芯片 | DW01 SOT-23-6 | U3 | 1 |

2电路图

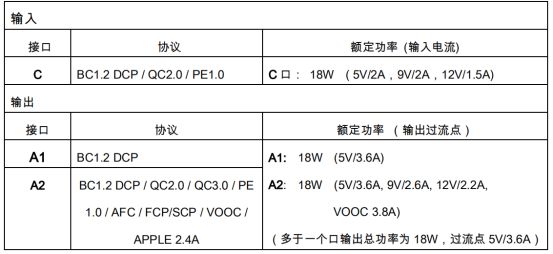

3功能描述

1) 接口协议及功率

2)操作UI

插入适配器首次上电激活锂电保护电路,系统上电,随后进入充电状态。若适配器支持快充则执行快充握手后协调输入电流.并根据电池的电压进行涓流,恒流和恒压充电,LED灯闪烁显示电池电量;恒压充电阶段充电电流小到一定程度后确认电池充满,关闭充电;若电池充满电后未拔出电源,电池电压降到回充电压点后重新进入充电;充电状态拔出电源后,系统进入待机.充电状态不响应输出口负载插入,也不响应按键。

待机状态插入手机或短按按键进入放电状态.若此时有手机插入且支持快充的话则执行快充握手后协调输出电压,LED显示电池电量.负载电流小到一定程度后确认手机充满电,延时一段时间后关闭输出,进入待机.输出时长按按键则关闭输出进入待机.输出状态时插入电源转入充电状态.当发生过压,欠压,过流,短路,等异常时,立即关机.当高低温过温后也关机,温度恢复到正常后重新工作

4PCB设计

1.IC下面需敷铜散热(IC衬底要连接到PGND),散热面积尽量大,衬底焊盘打通孔到PCB底层,并适当露铜皮增强散热。

2.LDO18脚的10uF电容要靠近芯片管脚;AGND用单点接连的方式回到PGND。

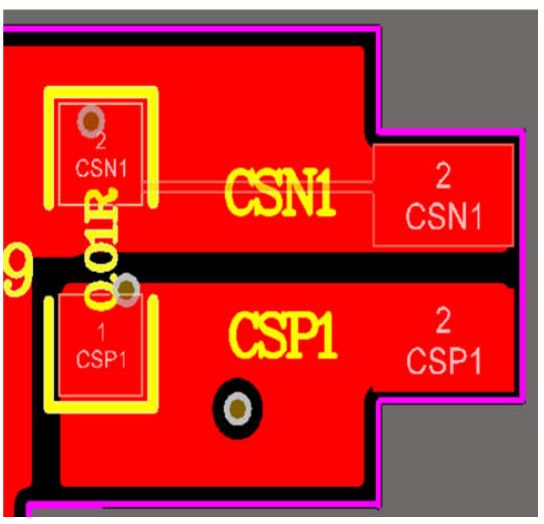

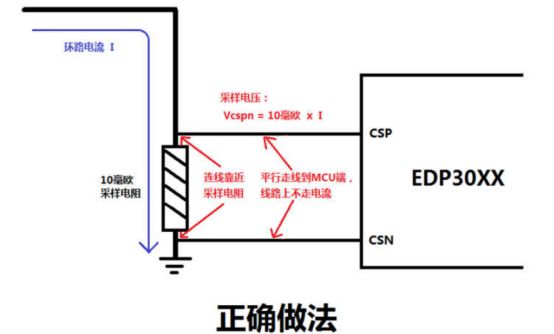

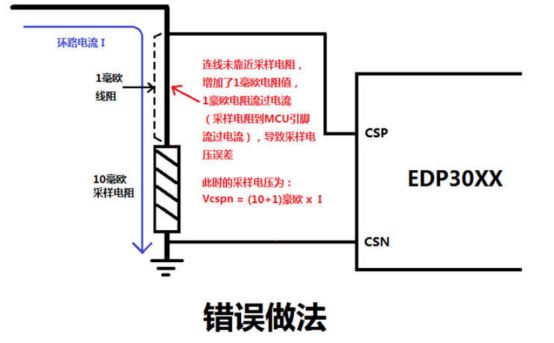

3.采样电阻CSP,CSN端Layout应遵循如下规则:

a)CSP,CSN走线要尽量避开干扰源器件比如电感,环路MOS,Vout等;

b)CSP,CSN走线尽量在同一层,减少打孔的情况;

c)CSP,CSN两条线都必须靠近采样电阻,从采样电阻两端平行走线接入芯片且尽量靠近芯片;采样电阻到芯片端之间的连线不得过电流.同样原理CSN也是不可以直接和PGND相连。

4.大电流通路(升降压环路部分电路:BAT–电感–MOS--VOUT):尽量走在同一层,而且尽量粗短,同时地的面积也尽量增大且要完整.这样可以增加散热,减小纹波并降低EMC干扰.

5.USB口外壳不可以直接接GND.因为某些USB线负极是与外壳相连的,而采样电阻是需要接在接口负极与GND中间,若两者相连则相当于采样电阻短路了.

6.为保证散热,EMC等性能最佳,推荐使用四层板

-

锤子推出新款坚果快充移动电源10000mAh 输出功率最高可达18W2019-09-11 5726

-

教你如何制作一个18W全兼容快充适配器2018-07-18 3884

-

三分钟了解如何制作一个18W全兼容快充移动电源2018-08-15 4845

-

SW6124 整合PD3.0的 全协议快充 移动电源单芯片2019-01-14 7006

-

科发鑫 18W移动电源方案 IP5328P 全协议兼容2019-08-23 1798

-

智融推出超级快充移动电源芯片SW6208:支持数显,全接口快充2019-08-27 3838

-

超级快充移动电源SOC芯片SW6208:内置数码管驱动,三进三出全接口快充2019-09-02 2075

-

PD3.0的全协议快充移动电源单芯片SW61242021-03-31 1762

-

[供应] 智融SW6106双向PD移动电源18W多协议快充芯片+无线快充方案2022-03-18 14236

-

锤子科技推出坚果18W快充移动电源,支持双向快充2019-09-10 3643

-

公牛移动电源快充版高清图赏2018-11-30 3823

-

关于全兼容快充适配器性能分析和应用2019-08-30 11571

-

果粉18W闪充套装上架 支持18W PD3.0快充协议2020-01-03 4480

-

Geekon移动电源概念版 18w QC3.0 PD 3.0双向快充 三口正反插 动态灯效2022-01-05 724

-

SW6106 18W快充开源设计案例2022-08-08 1676

全部0条评论

快来发表一下你的评论吧 !