关于全兼容快充适配器性能分析和应用

描述

目前快充市场可谓“百花齐放”,各种快充协议让人眼花缭乱。高通QC2.0/3.0、MTKPE 1.0/2.0和USB PD高压快充占据市场大壁江山;华为Super Charger、OPPO VOOC、努比亚NeoCharger、高通QC 4.0以及MTK PE3.0低压直充也发展迅速;魅族、小米、OPPO以及锤子等手机品牌也正在研究更大功率的电荷泵高压直充充电技术。

快充业界尚未形成统一的协议,各种协议互不兼容,用户使用起来诸多不便。将各种快充协议放到一个芯片内做一个全协议兼容的方案,可以一定程度上解决兼容性难题。

易能推出的EDP3032,是为全协议快充适配器设计的一颗 SOC 芯片,内部集成 QC2.0、QC3.0、PE1.0、AFC、FCP、SCP、 VOOC、BC1.2 DCP、APPLE 2.4A 快充协议;支持输出电压自适应,还集成了输出欠压、过压、短路保护等多重安全保护功能。如何利用易能的EDP3032芯片制作一个18W全协议兼容的快充适配器?

(18W全兼容快充适配器)

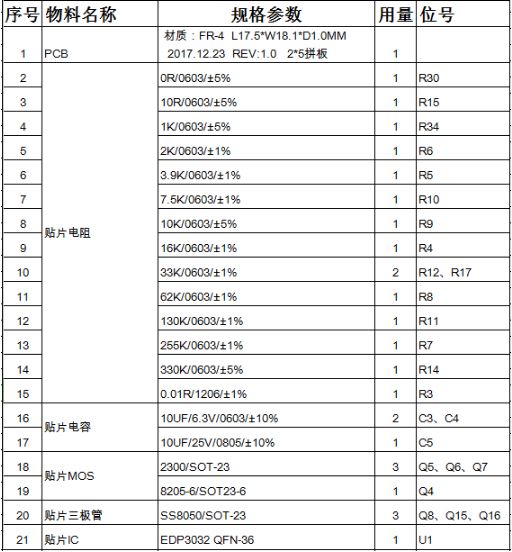

1 BOM贴片清单

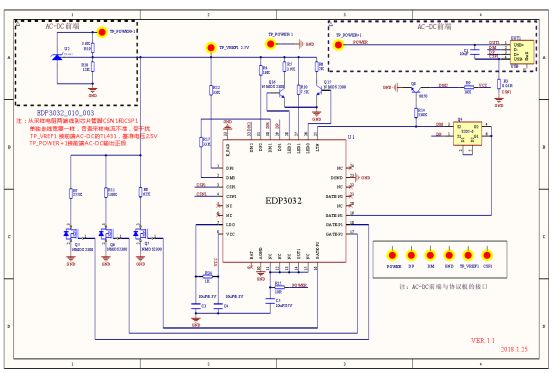

2 电路原理图

3 PCB设计

(1)IC下面需敷铜散热,IC衬底要连接到PGND,散热面积尽量大,衬底焊盘打通孔到PCB底层,并适当露铜皮增强散热。

(2)LDO18脚的10uF电容要靠近芯片管脚;AGND用单点接连的方式回到PGND。

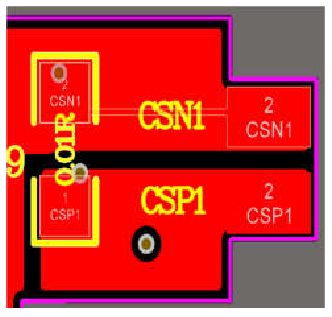

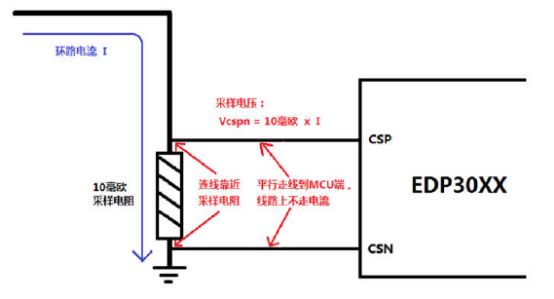

(3)采样电阻CSP,CSN端Layout应遵循如下规则:

a) CSP,CSN走线要尽量避开干扰源器件比如电感、环路MOS、Vout等;

b) CSP,CSN走线尽量在同一层,减少打孔的情况;

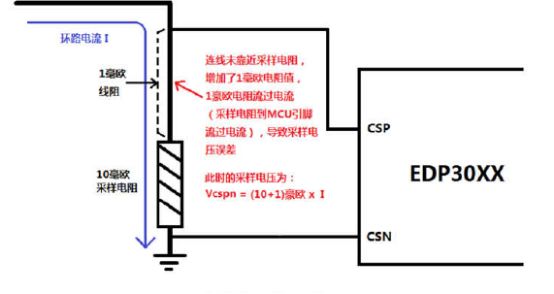

c) CSP,CSN两条线都必须靠近采样电阻,从采样电阻两端平行走线接入芯片且尽量靠近芯片,采样电阻到芯片端之间的连线不得过电流。同理,CSN也不可以直接和PGND相连。

( 焊盘 )

(正确做法)

(错误做法)

d) 大电流通路(升降压环路部分电路:BAT–电感–MOS--VOUT):尽量走在同一层,而且尽量粗短,同时地的面积也尽量增大且要完整,从而增加散热,减小纹波并降低EMC干扰。

e) USB口外壳不可以直接接GND。由于某些USB线负极与外壳相连,而采样电阻需要接在接口负极与GND中间,若两者相连会导致采样电阻短路。

f) 为保证散热,EMC等性能最佳,推荐使用四层板。

-

5V供电的STC单片机串口引脚(TX/RX)接到快充适配器的D+/D-上面后,导致快充适配器输出9V电压,这是什么原因导致的?2025-03-26 9540

-

教你如何制作一个18W全兼容快充适配器2018-07-18 3997

-

三分钟了解如何制作一个18W全兼容快充移动电源2018-08-15 4952

-

请问适配器快充口对应的握手芯片也是要有快充功能有哪款2019-01-31 2806

-

在适配器快充多协议这个版块,智融同样推出几款强力芯片。2019-09-27 1249

-

PD电源适配器是什么2020-04-28 8629

-

IP6505车充/适配器解决方案2020-07-02 38596

-

USB-C PD适配器的相关资料推荐2021-12-29 1828

-

光纤适配器是什么_光纤适配器的作用介绍2018-02-26 42854

-

设计模式-适配器模式-以电压适配器为例2021-11-07 1164

-

效率因数是如何影响电源适配器性能的?2023-11-23 1787

-

什么是蓝牙适配器?它有哪些性能特点?2024-02-02 5738

-

12W适配器电源芯片U93136的工作原理介绍2024-04-28 2343

-

芯海科技CPW3301:兼容多种PD快充协议,引领电源适配器市场2024-08-09 1594

-

适配器电源IC U231X集合高效率、安全性、小体积多重优势2025-01-09 1388

全部0条评论

快来发表一下你的评论吧 !