HBM PHY的作用 以及验证方面的一些难点介绍

描述

由于制造技术的进步,存储系统在过去几年中发展了很多。高带宽存储器(HBM)是最新类型的存储器芯片的一个例子,它可以支持低功耗,超宽通信通道和堆叠配置。 HBM子系统涉及不同类型的存储器控制器(全速,半速),HBM PHY和HBM DRAM。 HBM子系统适用于涉及高性能图形和计算,高端网络和通信设备以及需要大量内存的处理器的应用。由于其关键的最终应用程序角色,验证HBM子系统中涉及的所有设计组件至关重要。在这里,我们将讨论HBM PHY的作用,以及主要的验证方面/挑战。

简介

HBM PHY是整个HBM系统解决方案的关键要素。 HBM PHY通常通过DFI接口从存储器控制器接收HBM DRAM row-col命令,数据,奇偶校验等,并将它们与HBM DRAM接口一起传递给HBM存储器。它处理两种不同的接口,支持DFI接口的多种频率比。理想情况下,HBM PHY需要支持所有HBM存储器功能,如频率比,数据速率,存储器大小,伪通道模式,传统模式,DBI,DM等.HBM PHY可以在子系统级别和块级别进行验证,具有不同的,供应商特定的内存控制器和HBM内存。

验证策略

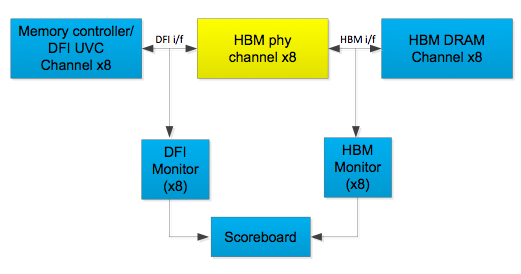

图1验证策略流程

要验证HBM PHY设计,我们需要以下组件:HBM内存控制器或DFI驱动程序UVC(通用)验证组件)用于驱动DFI接口:

DFI接口信号可能是特定于实现的,但它们应遵循所谓的DFI3.1协议。供应商特定的内存控制器可以是单端口或双端口。 DFI接口涉及控制接口,写数据接口,读数据接口,更新接口,状态接口和培训接口的阶段0和阶段1信号。当选择频率比1时,控制器将仅以与HBM DRAM存储器时钟频率相同的频率驱动0相信号(* p0)。支持频率比为2的控制器将在两个阶段上驱动:phase0(* p0)和phase1(* p1),占DRAM内存时钟频率的一半。

AMBA APB总线可用于配置和初始化用于HBM DRAM的存储器控制器,如DM,DBI,延迟等。存储器地址和数据可以使用AMBA AXI总线或任何供应商专用接口提供。一旦通过APB接口初始化和配置存储器控制器,存储器控制器将获得读写地址并通过AXI总线或其他供应商特定接口写入数据。 APB/AXI/供应商特定的UVC将用作存储器控制器的配置和数据驱动程序。

完全随机化,时序控制,无缝事务,row-col命令控制&但是,内存控制器不支持很少的模式操作。因此,功能验证可能存在覆盖漏洞。为了实现完全随机化,时序控制,基于命令控制系统Verilog -UVM的DFI UVC用于驱动DFI信号。

用于接收DRAM写入读取的HBM内存

供应商特定的HBM内存可用于连接HBM PHY HBM JEDEC接口。该HBM存储器将从HBM PHY接收HBM命令,数据,数据掩码,奇偶校验等。通常,所有内存模型都提供内置协议断言。每个HBM设备都具有特定于供应商的功能,功能和时序。 HBM内存模型将在VCS/IUS/Questa工具中加密;因此,验证环境应与所有工具兼容。应根据HBM内存的所有支持功能验证HBM PHY。

DFI Monitor,HBM Monitor

DFI监视器将捕获row-col地址;从DFI接口写入数据,读取数据,数据掩码,数据总线反转等信息。在写入操作期间,它将基于DBI和DM值存储写入数据,并且在读取操作期间,它将读取的数据与先前存储的写入数据进行比较。类似地,HBM监视器将仅捕获驻留在HBM DRAM接口中的row-col地址,写入数据,读取数据,数据掩码,数据总线反转等信息。由于DFI监视器正在执行相同操作,因此无需在HBM监视器中进行内存写入读取比较。 DFI监视器应支持频率比为1和2。两个监视器都是用UVM方法开发的,并为其他验证组件提供HBM数据包。

DFI接口和DRAM接口之间的记分板

记分板将获得HBM来自DFI监视器和HBM监视器的数据包。在写入传输的情况下,将来自DFI监视器的HBM数据包与来自HBM监视器的HBM数据包进行比较。 HBM监测的HBM数据包与DFI监测的HBM数据包进行比较。

验证挑战

主要是行为内存模型已加密,因此调试仍然是一项挑战。但是内存断言会记录任何HBM DRAM时序违规。 DFI,HBM监视器和记分板将帮助调试问题。

频率比1:2在DFI驱动程序和DFI监视器中实现。 DFI接口需要以HBM时钟频率的一半频率驱动2个不同相位(P0和P1)的信号。

存储器控制器和其他存储器设备的功能限制将无法完全验证HBM PHY。 DFI UVC可以克服内存控制器的局限性,这意味着不同的内存模型可以集成到测试平台中以覆盖全部功能。

验证环境应该是工具(VCS,IUS,Questa) - 独立作为内存模型可以在任何工具中加密 - IUS,VCS,Questa。基于System Verilog-UVM的验证环境将提供独立于工具的平台。

处理全速和半速模式的无缝写入/读取,在DFI驱动程序,DFI监视器,HBM监视器中需要系统架构。

使用APB接口初始化和配置所有内存控制器需要测试芯片级验证,这需要大约10分钟的模拟时间。因此,调试时间会增加。

常见问题

时间违规和写入读取内存模型的延迟限制将产生错误的读取数据,主要是“x”。

门级仿真将为设计中的未初始化的触发器产生“x”。工具&使用开关设计特定的初始化以初始化具有某些已知值的所有触发器将有助于克服此问题

- 相关推荐

- 热点推荐

- PCB打样

- 华强PCB

- HBM

- 华强pcb线路板打样

-

急需一些电子技术方面的资料,希望能够在此等到2009-07-18 3248

-

自己收集的一些关于手机摄像头方面的资料,分享下!2013-10-03 14050

-

搜集到的一些步进电机方面的VI资料2015-05-06 9234

-

求一些BMS方面的资料2015-05-24 4568

-

上传一些关于DSP算法方面的资料,互相学习。2015-07-09 11684

-

想学习一些机器人控制方面的工作,要学习什么内容!2015-11-20 4565

-

USB产品在调试与规范验证方面有哪些技巧?2021-05-10 805

-

分享一些嵌入式方面的基础知识2021-11-08 2267

-

介绍一些与变量相关的存储属性与作用域2022-02-14 755

-

一些无线电方面的旧资料.pdf2010-03-12 514

-

PAM4信号的一些测试和测量方面的挑战2019-08-08 9753

-

分享一些比较全面的手机原理资料2021-11-05 939

-

介绍HBM3标准的一些关键功能2022-08-17 7246

-

介绍一些大功率IGBT模块应用中的一些技术2022-09-05 3983

-

飞速发展的HBM仍面临着一些挑战2023-07-22 3352

全部0条评论

快来发表一下你的评论吧 !