电源完整性和配电网络阻抗对同步开关噪声的影响

描述

对于硬件设计人员来说,了解PDN的每个元件的谐振频率(例如,体旁路和去耦电容,平面电容和互连电感)及其对PI的影响非常重要。具有差的PI的PCB(例如,在50MHz及更高时具有高PDN阻抗)引起由PDN供电的信号的SSN和抖动。本文演示了PCB上PDN阻抗与SSN之间的关系。

分析和结果

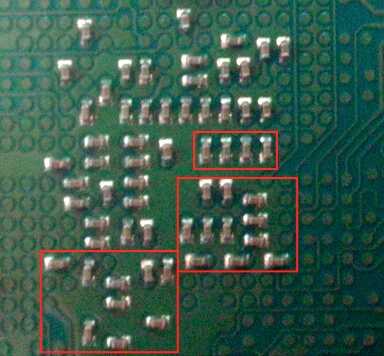

原型如图所示图1已实施。该处理器带有外部40MHz晶体振荡器,有三个主要接口:320Mbps数据或160MHz时钟速率的DDR2 SDRAM,80MHz时钟速率的并行闪存和通用I/O.所有这些组件都从降压转换器获取功率。在PCB上,每个电源引脚上的处理器BGA正下方放置0.1μF去耦电容,如图2所示。

图1DUT的方框图

图2处理器下的去耦电容放置

为了显示PDN阻抗和SSN之间的关系,在原型PCB上尝试了表I中列出的两个测试用例。在测试用例A中,卸载了一部分去耦电容(如图2中的红框所示)。另一方面,所有去耦电容都加载到测试用例B中。

表I.正在研究的去耦条件

| 测试用例 | 条件 |

| A | 一部分去耦电容器被卸载 |

| B | 所有去耦电容都加载 |

首先,比较10MHz至500MHz的PDN阻抗曲线(使用Mentor Graphics Hyperlynx进行仿真)。由于Vcc和地之间的去耦电容量较低,测试用例A的阻抗高于情况B.

图3PDN阻抗图

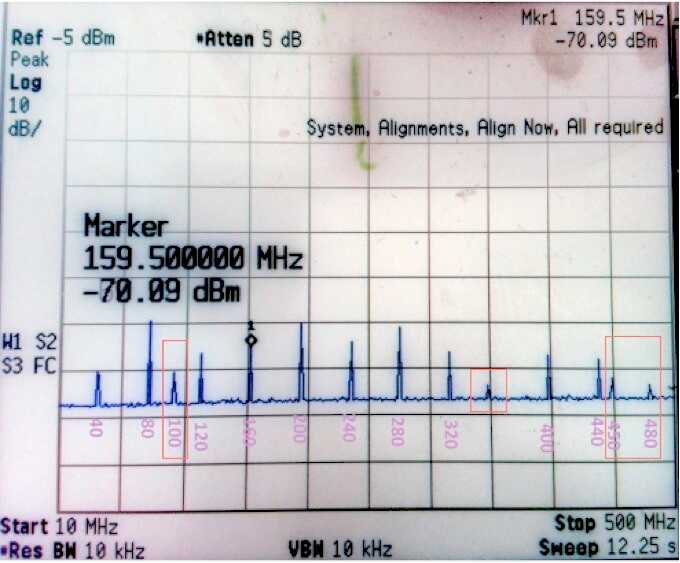

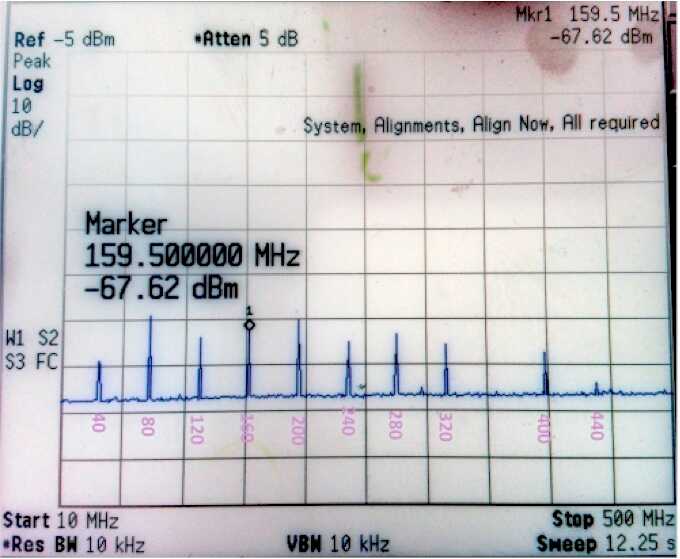

其次,两个测试案例比较了Vcc的功率谱(使用频谱分析仪通过交流耦合探测),范围从10MHz到500MHz 。参考情况B(图4b),观察到的尖峰主要由40MHz晶体振荡器,160MHz DDR2和80MHz闪存接口以及相关内部处理器PLL的谐波贡献。但在情况A中,由于较低的总去耦电容,Vcc频谱中出现额外的尖峰(图4a中用红色框出)。

Vcc上的噪声是由PDN阻抗与瞬态之间的相互作用引起的IC内所有同步切换信号的电流,即SSN。当更多的去耦电容正确放置在Vcc线上时,可以抑制SSN和Vcc噪声。

图4a电源测试用例A的Vcc频谱

图4b测试用例的Vcc功率谱B

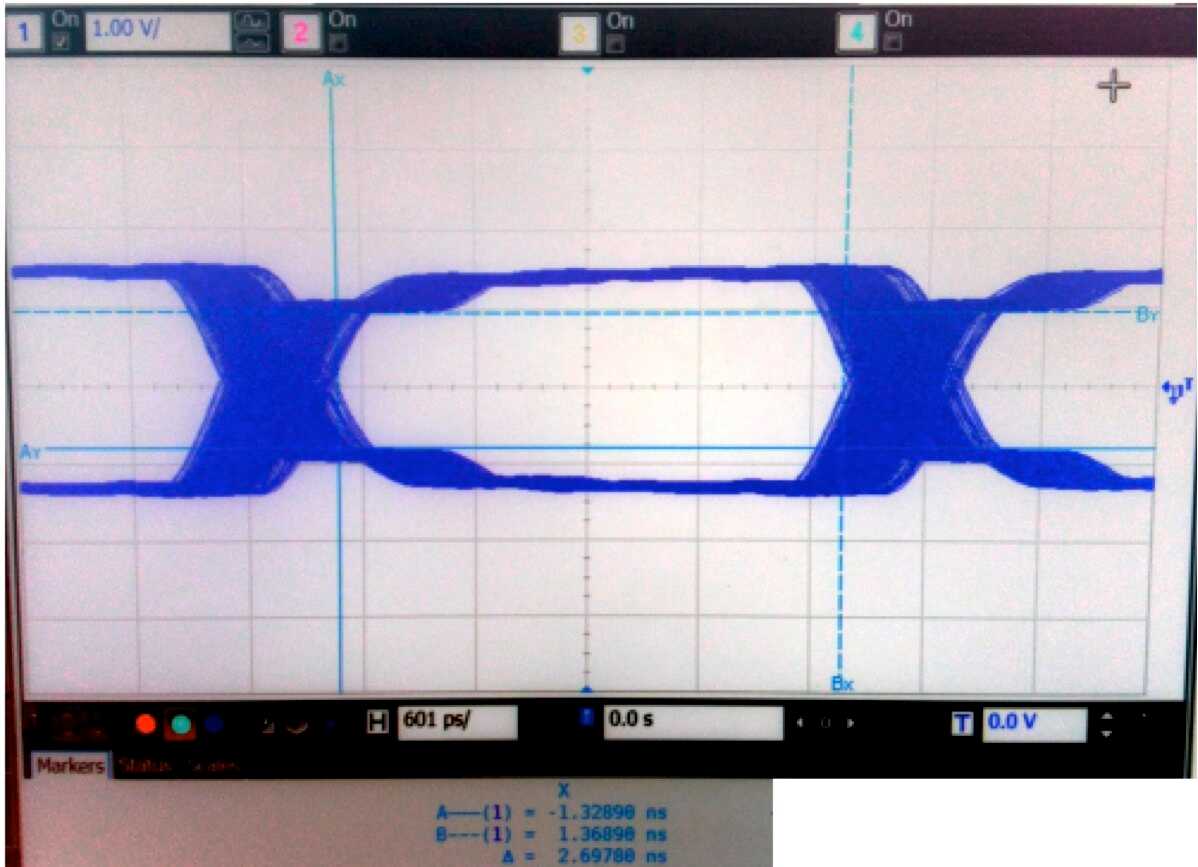

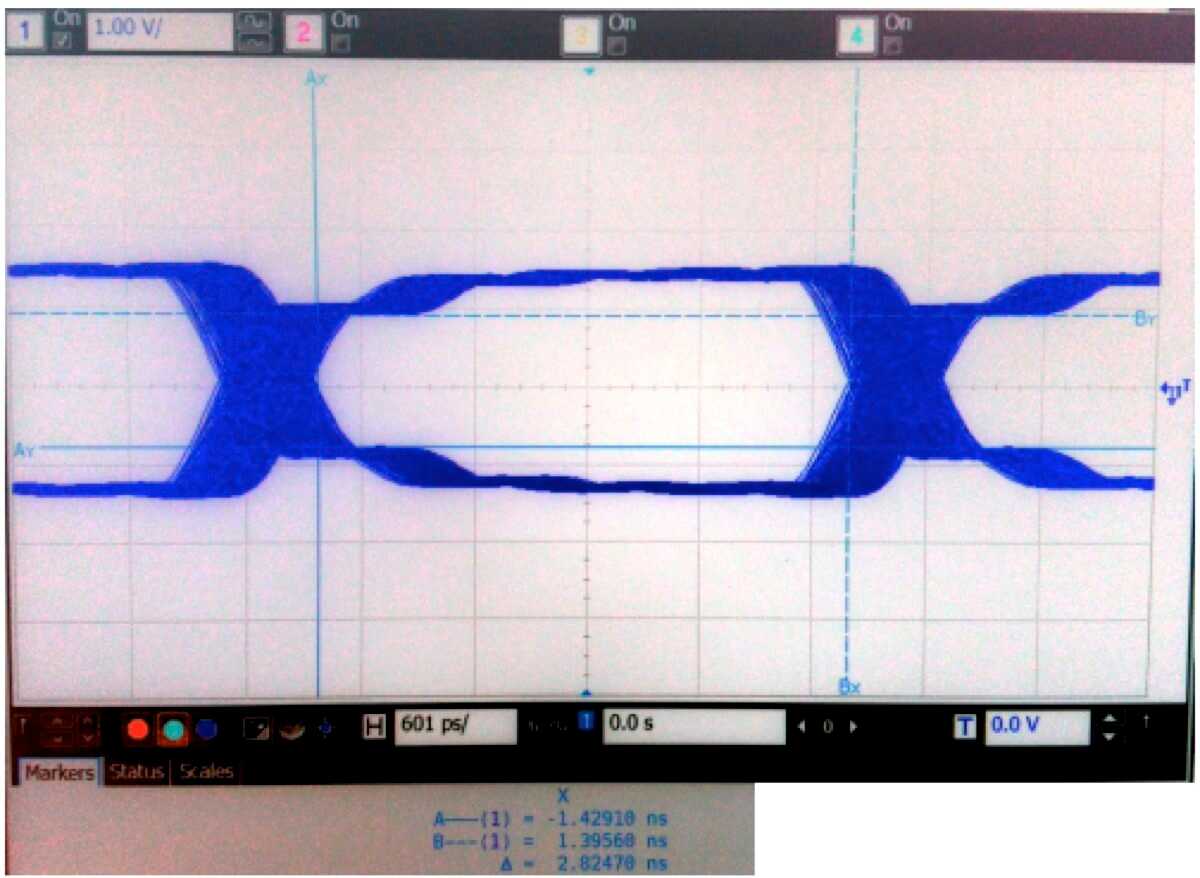

第三,比较两个测试用例的以160MHz(3.125ns单位间隔)运行的DDR2时钟信号的眼图开度。在情况B(2.825ns)与情况A(2.698ns)的情况下,较大的眼宽表明抑制Vcc噪声有助于减少处理器发送的信号中的抖动。

图5a测试用例A的DDR2时钟信号眼图

图5b测试案例B的DDR2时钟信号眼图

结论

在这个实际实验中证明了PDN阻抗对SSN和抖动的影响。至关重要的是,PCB PDN必须以严格的方式实施,以确保质量,稳健性和功能性。

- 相关推荐

- 热点推荐

- PCB打样

- 华强PCB

- 华强pcb线路板打样

-

电源完整性的设计说明2024-11-19 1833

-

电源完整性设计【硬件干货】2024-10-30 2880

-

电源完整性分析参考解决方案2024-10-11 1268

-

配电网是什么意思 配电网电压等级2023-04-03 8184

-

电源完整性设计与测试2022-08-30 4393

-

电源和信号完整性的分析与测试2022-01-07 1402

-

什么是电源和信号完整性?2021-12-30 2119

-

简单总结一些造成电源完整性的问题2021-10-29 2217

-

电源完整性(PI)概述2021-10-22 1513

-

电源完整性之同步开关噪声SSN2021-10-21 2173

-

电源系统优化——深入解读优化高速数据转换器的配电网络2021-07-17 2926

-

电源完整性(PI)设计以及测试方法2020-10-20 4328

-

基于最小路的配电网可靠性评估2018-01-05 949

-

配电网络柱上开关监测系统应用方案2016-09-21 5171

全部0条评论

快来发表一下你的评论吧 !