关于数字有源EMI滤波器解耦电路的设计方法的介绍和研究

描述

针对数字有源EMI滤波器(DAEF)信号检测点与注入点的耦合会降低EMI抑制性能问题,本文通过建立含有解耦电路的DAEF模型,仿真分析解耦电路对滤波特性的影响,提出一种DAEF系统解耦电路的设计方法。该方法基于实测阻抗匹配原则,在不改变原电路结构,不增加DAEF体积的前提下,大幅度提高了DAEF系统EMI抑制能力。对消技术可有效降低开关电源工作中产生的传导EMI。本文基于FPGA控制器搭建了含有解耦电路的DAEF控制系统平台,利用R&S公司的EMI接收机实验测试EMI,仿真及实验结果表明本文提出的解耦电路设计方法有效地提高了DAEF的滤波能力。

Abstract:Aiming at the problem that the coupling between EMI signal detection point and injection point in digital active EMI filter (DAEF) reduces EMI suppression performance, this paper presents a design method about decoupling circuit in DAEF system through building DAEF model with decoupling circuit and analyzing effect of the decoupling circuit on filter characteristics. Based on real tested impedance matching principle, and no changing original circuit structure and no increasing the volume of DAEF, this method greatly improves DAEF system EMI suppression performance. This paper builds a DAEF control system with decoupling circuit based on FPGA controller. Experiments results show that the proposed method effectively improves the filtering performance of DAEF.

Key words: Electro-Magnetic Interference, EMI filter, filter performance, decouple, impedance matching

1. 引言

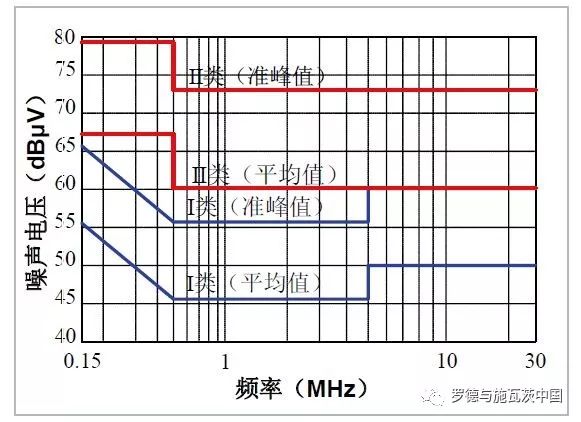

开关功率变换器的高频化使得其产生的高频传导EMI噪声越来越严重,为保证电子设备的正常工作,国标GB/T 21419-2013规定了传导EMI信号在0.15 MHz~30 MHz频率范围内的允许发射限值[1]。

传导EMI的一般抑制方法是在变换器前端加EMI滤波器。模拟无源EMI滤波器 (Passive EMI Filter,PEF) 电路拓扑简单,运行可靠[2],但其体积和损耗较大、滤波灵活性差。模拟有源EMI滤波器 (Active EMI Filter, AEF) 克服了PEF灵活性差的缺点,但由于速度、功率损耗和增益带宽的限制,在抑制高频噪声或强噪声电流方面能力不强[3]。进而出现了PEF与AEF相结合的混合模拟有源EMI滤波器 (Hybrid Active EMI filter, HAEF) [3,4],但其宽频率范围内的抑制效果不佳,另外清除运算放大器的偏置电压问题还有待解决。这些技术未从根本上解决EMI滤波器的体积和功耗问题。

随着FPGA的广泛发展,A/D转换速度和精度的大幅提高,加上数字处理器成本不断降低,使得数字有源EMI滤波器(Digital Active EMI Filter, DAEF) 实际应用成为可能 [5,6]。DAEF因不在主电路中串联器件,所以从根本上解决了EMI滤波器体积和功耗问题,且不受功率与电流的限制,但该方法中EMI信号的检测和注入点存在耦合,这个耦合会使得DAEF的滤波性能降级。

本文对DAEF系统中EMI信号检测与注入点的耦合作用进行仿真分析,提出一种解耦电路的设计方法,解决了这种耦合带来DAEF滤波性能降级的问题。

2. DAEF系统的设计及建模分析

2.1 DAEF的拓扑及原理

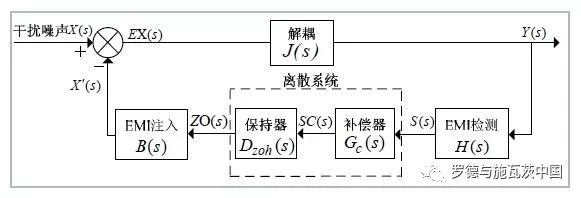

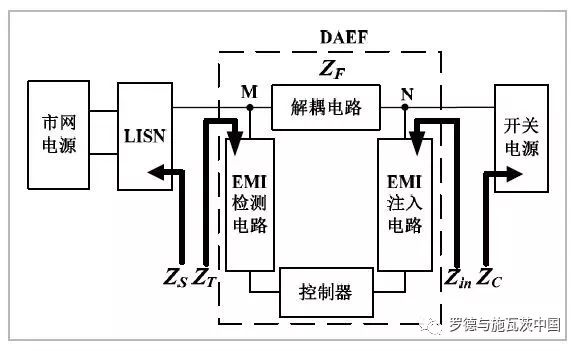

抑制共模EMI是开关功率变换器传导EMI抑制的主要任务,在低压交流电源端口的共模EMI电压为L线与N线对地EMI电压的平均值,减小其中任何一个均可减小共模传导EMI,由于两个信号在传输和抑制机理上相同,本文仅以抑制L线对地的传导EMI信号为例说明该方法。L线上DAEF抑制传导EMI的原理图如图1所示,DAEF系统包括EMI信号检测电路和注入电路、ADC采样、数字控制器、DAC输出和解耦电路6部分。

图1 DAEF系统应用原理框图

EMI信号检测电路由电阻RS和电容CS构成的高通滤波器实现,提取功率变换器在L线上产生的高频传导EMI信号;ADC将检测的EMI信号进行采样,得到相应的数字EMI信号;控制器对数字EMI信号进行EMI补偿控制,这里的控制器最好采用硬件描述语言编程和并行处理的FPGA;DAC把控制处理后的数字EMI信号转化为输出能力为0~20 mA的模拟EMI电流信号,该电流信号可以抑制86 dBμA (120 dBμV)的EMI信号。EMI信号注入电路是电阻Ri和电容Ci构成的低通滤波器,一方面把0~20 mA的模拟EMI电流信号注入到功率变换器输入端以消除其产生的EMI噪声,一方面利用电容Ci有效防止电源线上低频功率电流对DAC输出端口的损坏。 LD为检测和注入点之间的解耦电路。

2.2 DAEF的EMI控制方案

DAEF检测电源线L对地的传导EMI信号,经A/D转换采样、控制器补偿处理和D/A模拟输出,最后经注入电路注入到功率变换器的输入侧,形成一个闭环控制系统,其控制框图如图2所示,控制目标为使得沿L线传入供电电源的EMI信号Y(s)最小,即Y(s)=0。

图2 DAEF系统控制框图

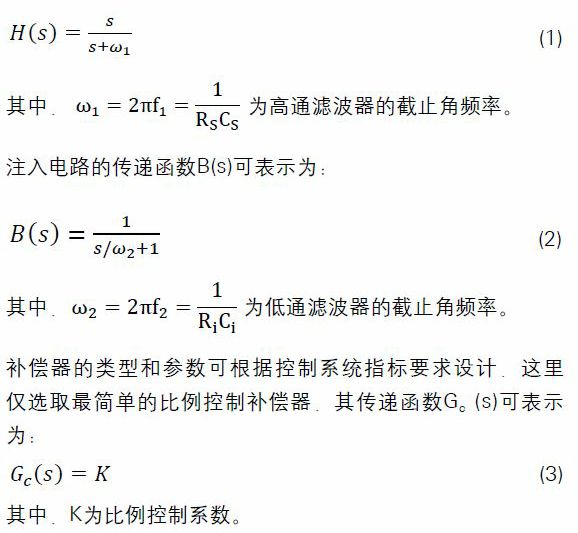

图2中,H(s)为EMI检测电路的传递函数,补偿器GC(s)为补偿控制算法的传递函数,Dzoh(s)为保持器的传递函数,B(s)为EMI注入电路的传递函数,J(s)为解耦电路的传递函数,Y(s)为经滤波之后的噪声信号;X(s)为功率变换器产生的未经滤波的EMI信号,X'(s)为经控制器处理后产生的反相补偿EMI注入信号。理想状况下,功率变换器产生的EMI信号X(s)和补偿注入的EMI信号X'(s)幅值相等、相位相反,相互抵消,实现抑制传导EMI的作用。

国标GB/T 21419-2013规定了低压交流端口传导EMI发射频率范围为0.15 MHz~30 MHz,如图3所示。因此提取EMI信号的RC高通滤波器的截止频率需在0.15 MHz以下;注入EMI信号的RC低通滤波器的截止频率需在30 MHz以上。

图3 GB/T 21419-2013规定的低压交流端口传导EMI发射限值

2.3 DAEF系统建模与分析

EMI检测电路的传递函数H(s)可表示为:

解耦电路可以等效为一个高阻抗解耦电感LD,其传递函数J(s)可表示为:

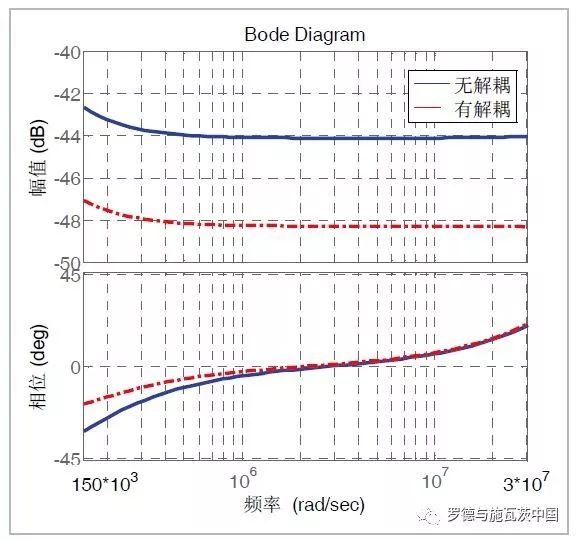

补偿器选纯比例补偿增益为100的情况下,对有解耦电路(J(s)=5.4×10-7s) 和无解耦电路(J(s)=1)时闭环DAEF控制系统进行仿真分析,得出其频率响应曲线如图4所示。

图4 DAEF系统频率响应曲线图

由图4可知,在0.15 MHz~30 MHz频率范围内,无解耦电路时DAEF的抑制能力仅在-44 dB,但是如果加入解耦电路DAEF的抑制能力达到了-48.3 dB,提高了4.3 dB。

3. 解耦电路的设计

在EMI信号检测电路和注入电路之间,传统方法为加入绕线式电感解耦,但这会增加EMI滤波器体积和功耗。本文提出一种在不改变原电路形式及结构的前提下,采用单匝电感作为解耦电路的方法。该单匝电感的磁芯材质、频率阻抗曲线和尺寸是该设计方法的重点。

3.1 解耦电感磁芯材料设计

由于镍锌铁氧体对于高频段的电磁干扰有很好的抑制作用,因此,本文选用镍锌铁氧体作为解耦电感的磁芯材料,该磁芯根据NiO与ZnO含量可工作在100 kHz~140 MHz频率之内。

在镍锌铁氧体中,NiO与ZnO的含量与镍锌铁氧体工作上限截止频率及相对磁导率μr有直接关系,镍锌铁氧体常用的配比如表1所示。

表1 镍锌铁氧体配比与截止频率的关系

由于传导EMI频率范围要求在0.15 MHz~30 MHz,所以选择上限截止频率为30 MHz的镍锌铁氧体配比:Fe2O3ZnO=50.224.9,所以镍锌铁氧体的相对磁导率μr为150。

3.2 解耦电感阻抗曲线设计

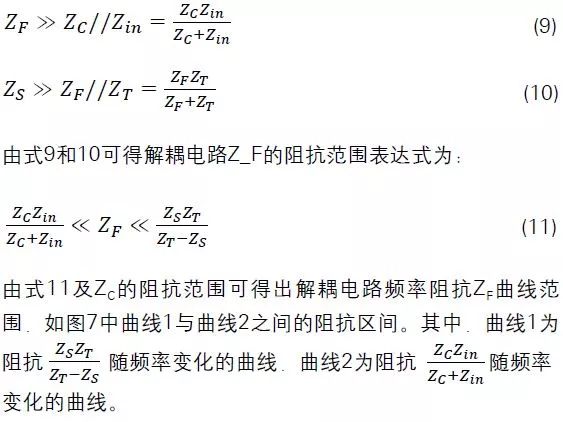

解耦电感的设计需要先确定其频率阻抗曲线范围,其次根据阻抗曲线进一步确定解耦电感的尺寸规格。

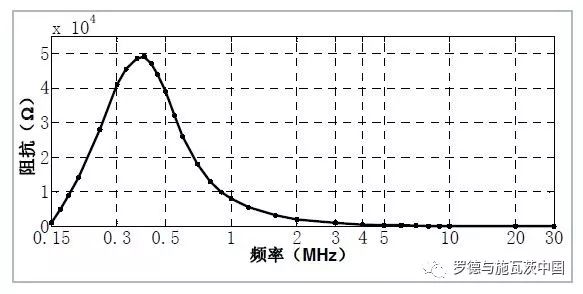

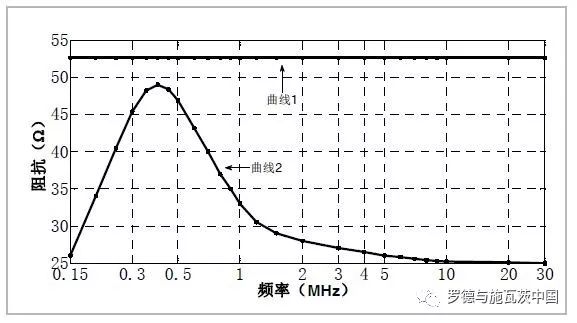

DAEF系统的等效阻抗电路如图5所示,其中ZS为从检测点M向市网电源端看的对地电源等效阻抗,由于LISN阻抗在0.15 MHz~30 MHz全频段稳定在50Ω,所以ZS在全频段满足ZS≈50Ω;ZT为从检测点M向EMI检测电路方向看的对地等效阻抗,在高频情况下电容可视作短路,所以ZT等效为RS;Zin为从注入点N向EMI注入电路看的对地等效阻抗,在高频情况下, Zin可等效为Ri; ZC为开关电源的对地等效内阻抗曲线,由双电流探头测试法得到[7],某品牌笔记本供电电源L线对地阻抗测量曲线如图6所示。

图5 DAEF系统等效阻抗电路图

图6 笔记本电脑供电电源L线对地阻抗测试曲线

由于ZF在全频段内应对从开关电源即噪声源流出的EMI信号呈现高阻抗,所以ZF的阻抗应远远大于从注入点N向EMI注入电路与开关电源并联反向看的对地等效阻抗,即满足式9;由于电源等效阻抗ZS应对流入LISN的EMI信号呈现高阻抗,所以ZS在全频段内应远远大于从检测点M向EMI检测电路与解耦电路并联方向看的对地等效阻抗,即满足式10。

图7 解耦电路阻抗Z_F的取值范围

3.3 解耦电感尺寸的设计

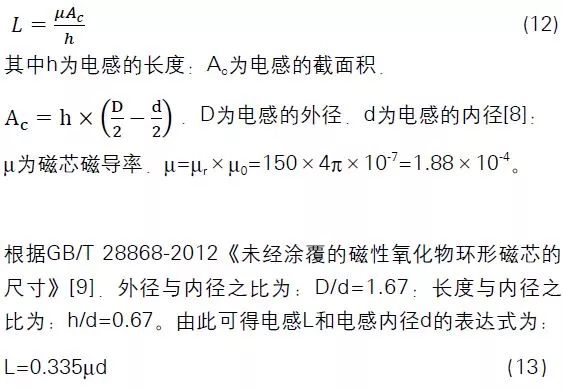

单匝电感的电感值与其内、外径及长度的关系为:

根据图7,可选取解耦电感在0.15 MHz~30 MHz频率范围内阻抗为50Ω。由于|ZF|=2πfL,f取中间频率15 MHz,可算出电感值为0.54 μH。由式13和D/d=1.67及h/d=0.67可计算出解耦单匝电感的尺寸规格为:D=14.31mm,h=5.74mm,d=8.57mm。

4. 实验验证

基于FPGA控制器建立DAEF控制器参数如下:

A/D转换器:14 bits,250 MSPS;

D/A转换器:14 bits,260 MSPS;

检测电路:Rs=1kΩ,Cs=0.1 μF;

注入电路:Ri=30Ω,Ci=1nF。

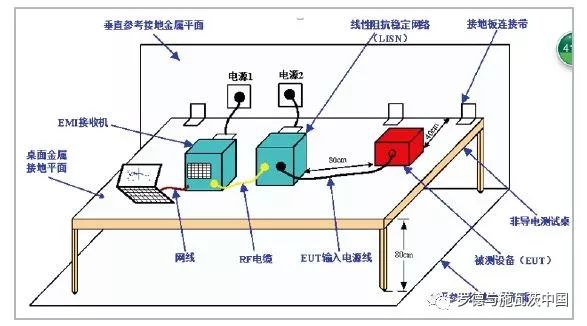

基于R&S公司的EMI接收机和线性阻抗稳定网络建立传导EMI测试平台如图8所示。测试平台设备型号及建立参数如下:

笔记本:华硕S550C

EMI接收机:R&S ESL3

LISN: ENV216 TWO-LISN V-NETWORK

被测设备:开关电源+DAEF

非导电测试桌:桌子高度0.8米,金属板厚2毫米,宽度为0.7米,长度为1.6米

垂直参考接地金属平面:铝金属板2毫米,水平宽度为1.6米,垂直长度为2米

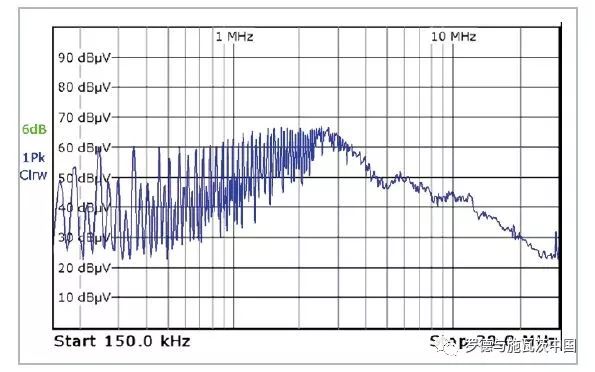

A/D转换器和D/A转换器均是高速、高采样率的器件,采用FPGA实现对数字EMI信号补偿控制处理。无EMI滤波器时,笔记本电脑供电电源L线对地传导EMI信号的频谱图如图9所示。

图8 EMI实验测量平台原理图

图9 无EMI滤波时L线对地传导EMI频谱图

从图9中可以看出,在不加EMI滤波器时,在0.5 MHz~5 MHz频段EMI噪声信号平均值约为55 dBμV,超过了国标限值46 dBμV。

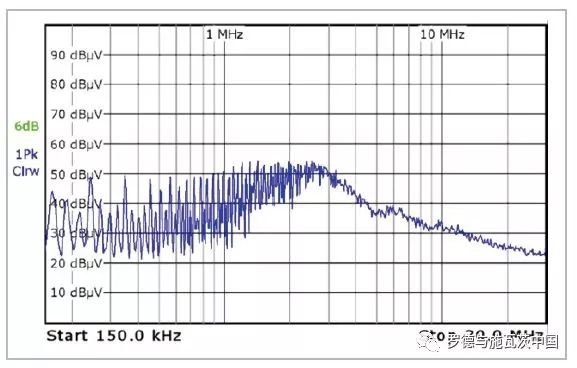

当用没有解耦电路的DAEF滤波时,笔记本电脑供电电源L线对地传导EMI信号的频谱图如图10所示。

图10 无解耦电路的DAEF滤波时L线对地传导EMI信号频谱图

由图10可知,采用无解耦的DAEF滤波时,L线对地的EMI得到抑制,均小于国标限值,采用DAEF达到了EMI滤波的目的。

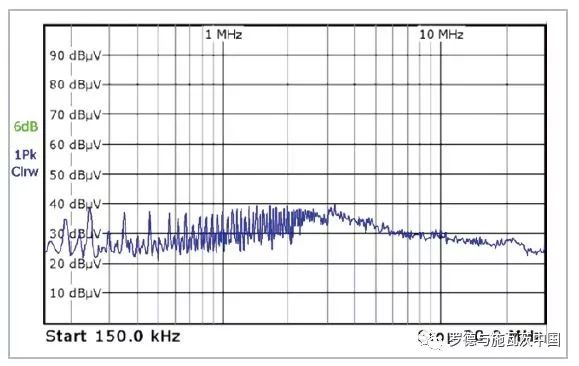

当用有解耦电路的DAEF滤波时,笔记本电脑供电电源L线对地传导EMI信号的频谱图如图11所示。

图11 有解耦电路DAEF滤波L线对地传导EMI频谱图

由上图11可知,在采用了有解耦电路的DAEF后,滤波效果不仅能达到国标限值,并且比没有解耦电路时滤波效果降低了5~10 dBμV。

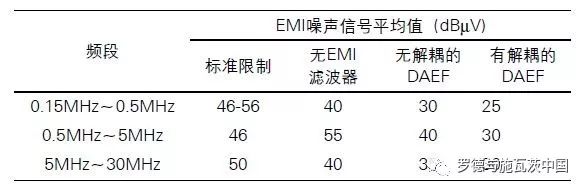

把无EMI滤波、无解耦的DAEF滤波、有解耦的DAEF滤波与国标限值对比如表2。

表2 各频段EMI噪声信号平均值

由表2可看出,DAEF对传导EMI有很好的抑制效果,DAEF的解耦电路有效的提高了DAEF的抑制能力,与仿真结果一致。

5. 结束语

本文针对DAEF系统信号检测点与注入点的耦合会降低EMI抑制性能问题,设计了带有解耦电路的DAEF系统及控制方案,建立了带有解耦电路的DAEF系统的模型,仿真分析了解耦电路对DAEF系统滤波性能的影响,给出了解耦电路的设计方法。利用R&S公司的EMI接收机实验测试EMI,基于FPGA搭建了DAEF控制系统平台,实验证明所提出的解耦电路设计方法有效的提高了DAEF的抑制能力,这将有效促进对数字有源EMI滤波器的进一步研究和广泛推广。

-

如何使用集成有源 EMI 滤波器降低 EMI 并缩小电源尺寸2021-08-31 2097

-

通过集成式有源EMI滤波器降低EMI并缩小电源尺寸的方法2022-11-04 928

-

有源滤波器中数字低通滤波器的设计及其DSP实现2010-05-13 1024

-

有源滤波器实用化保护电路与方法研究2011-08-10 898

-

QPI有源EMI输入滤波器2016-01-06 1054

-

三相有源电力滤波器滑模解耦控制方法研究_胡志坤2017-01-08 1090

-

并联有源电力滤波器解耦控制研究综述2018-03-22 1259

-

EMI滤波器设计原理与设计研究2018-06-07 19319

-

介绍关于有源滤波器ISim的特性与应用2018-07-05 5801

-

有源滤波器的原理2018-08-31 39155

-

有源EMI滤波器的工作原理,有源EMI滤波技术对比分析2020-11-13 10788

-

使用有源EMI滤波器缩减汽车系统中EMI滤波器的尺寸和成本2021-10-11 1609

-

如何通过集成式有源EMI滤波器降低EMI并缩小电源尺寸2023-03-20 1883

-

新型的有源EMI滤波器(AEF)电路分析2023-10-30 5318

-

独立式有源EMI滤波器 IC 如何缩小共模滤波器尺寸2023-11-27 1735

全部0条评论

快来发表一下你的评论吧 !