关于捷变频雷达频踪测试方法的介绍和分享

描述

捷变频频踪是捷变频雷达的核心分系统,本文提出了一种专门针对捷变频频踪测试的一种新方法,该方法不但实现了捷变频频踪参数的自动测量,还解决了捷变频点驻留时间、频率偏差,跳频频率集、换频时间等以往不容易测试的项目。是一种高效、创新的、更有信心的测量方法。

1 引言

同固定频率工作的雷达相比较,捷变频雷达在探测性能和抗干扰性能上都有明显提高。随着现代战争电磁环境变得越来越复杂,捷变频技术被广泛应用于雷达系统和导弹末制导系统中,捷变频体制所具有的抗干扰能力强、抑制杂波能力强、提高目标分辨能力等特点,在雷达制导中具有很强的优势。

由于捷变频雷达的相邻发射脉冲的载频在一个很大的范围内以很高的速度跳变,因此,要模拟产生捷变频雷达的模拟目标回波信号和模拟电子干扰信号在技术上有相当的难度,这也成了制约对捷变频雷达进行性能测试的关键因素。传统的测试方法都是使雷达工作在锁频(固定频率)状态下对其进行测试。但雷达导引头在锁频状态下的工作性能并不能真实反映其在捷变频状态下的工作性能,甚至有些技术性能是无法在锁频状态下进行测试的。常规方法在定频模式下,对点频测试,用频谱仪和定频信号源进行测试。这种方法不能反应雷达在捷变状态下的真实性能,且测试过程繁杂、周期长。但是要实现捷变频雷达的动态测量,就要求测试设备具有模拟雷达频率捷变状态下的测试功能,因此,要完成完整的捷变频雷达测试需要动态、宽带的信号分析仪进行信号采集并有专门的软件进行分析。

2 捷变频频踪概述

频综(Frequency synthesizer),又叫频率综合器、频率源,是有一个雷达“心脏”之称的分系统。他的主要功能是产生电子系统需要的各种形式的频率信号,比如产生单一频点连续波、跳频信号、步进频率信号、线性调频信号、非线性调频信号、IQ调制信号等各种各样电子系统所需要的信号形式。频综一般是根据整个系统的要求选用一个高稳定的振荡器,以此振荡器为基准通过采用分频、倍频、混频、功率放大等手段产生系统需要的各种频率信号,目前采用的技术主要有PLL、DDS、梳状谱产生、锁相介质振荡器、开关滤波组件、低噪声放大等。

目前捷变频频踪技术从其合成方法上基本可以分成三类:一种是模拟直接式(ADS),二是间接式(IS),它用锁相环(PLL)技术产生各种需要的合成频率;三是数字直接合成式(DDS)。三种方法各有特点,技术方法不同,频综的实现方案和电路结构, 以及体积、 成本、 功耗差别很大。 单从跳频速度分析直接式比间接式具有很大优势。 另一方面, 如前面所述现代化高性能雷达系统, 对频综各项技术性能均提出很高要求。例如: 动目标显示、 脉冲多普勒雷达, 为提高在强杂波背景下的动目标检测性能, 要求全相参频综具有极低的相位噪声、 杂散和很高的稳定性。 捷变频高性能频综技术是雷达系统的关键技术之一, 在工程应用的设计和研制中需要考虑各项技术性能, 对技术方法、 实现方案、 采用电路进行优化。当前能够产生捷变频速度最快的方式是采用DDS的方法,可以实现几到几百纳秒的时间切换。本文就以DDS频踪为例来阐述捷变频频踪的特点。 DDS是Direct Digital Frequency Synthesis(直接数字频率合成器)的简称。通常将DDS视为第三代频率合成技术,它突破了前两种频率合成法的原理,从“相位”的概念出发进行频率合成。 随着高速D/A和微电子技术的发展,DDS所能达到的频率越来越高,无杂散动态范围(SFDR)越来越大。DDS的基本原理如图1所示。

图1 DDS基本原理图

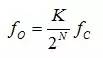

DDS的主要组成部分是累加器、波形存储器ROM和D/A转换器。累加器和波形存储器的位数决定了DDS的最小步进和由相位截断误差所引入的杂散,而D/A转换器的性能则是对SFDR有着非常大的影响。这里我们以ADI公司的捷变频器件AD9858为例, DDS的输出频率f0和时钟频率fc的关系为:

(1)

(1)

其中K为频率调谐字(Frequency Tuning Word),N为相位累加器位数。

AD9858当使用1000MHz时钟信号时,最小步进频率为:

(2)

(2)

由此可见,通过改变K可以方便的实现输出频率的变化,理论上DDS的跳频是即时的,跳频时间由数字器件的响应幅度决定,目前可以做到几个ns。

频综的主要技术指标有输出信号的功率、输出信号的带宽、输出信号的相位噪声、输出信号的杂散电平以及其他一些指标,捷变频频踪的跳频时间、线性调频频踪的调频线性度等。针对捷变频频踪而言,关注的指标有如下:

捷变频信号的杂散

捷变频信号的相位噪声

捷变频信号的频率切换时间

捷变频频点的频率稳定度

捷变频频点的驻留时间

捷变频频率集

捷变频频率数

捷变频频点的功率

捷变频频点的频率偏差

对于频踪的研发和测试来说,将被测项目精确、快速、方便的进行测试,是提高系统完成进度的重要保障。

3 捷变频频踪自动测试方法

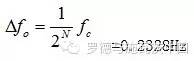

R&S公司的实时信号与频谱分析仪FSW提供了一种简便的捷变频频踪测试方法。FSW提供了高达500MHz分析带宽和67GHz的频率测试范围,K60是基于FSW硬件平台的一个软件,该软件是专门针对捷变频频踪测试所开发的,其创新点在于该仪器配合软件可以自动跟踪捷变频的频率变化和相位变化,并自动识别每个捷变频点,对于传统信号分析仪来说,是无法自动识别捷变频的频率变化的,尤其是当信号频率不在频谱仪的中心频率的时候,就无法正确分析信号的时频变化了。按照捷变频信号的特点,该软件进行了信号的描述如图2所示:

图2 捷变频信号图示及测试项目

按照图2所示的测试项目定义,FSW可以自动对捷变频信号的这些测试项目进行测量。

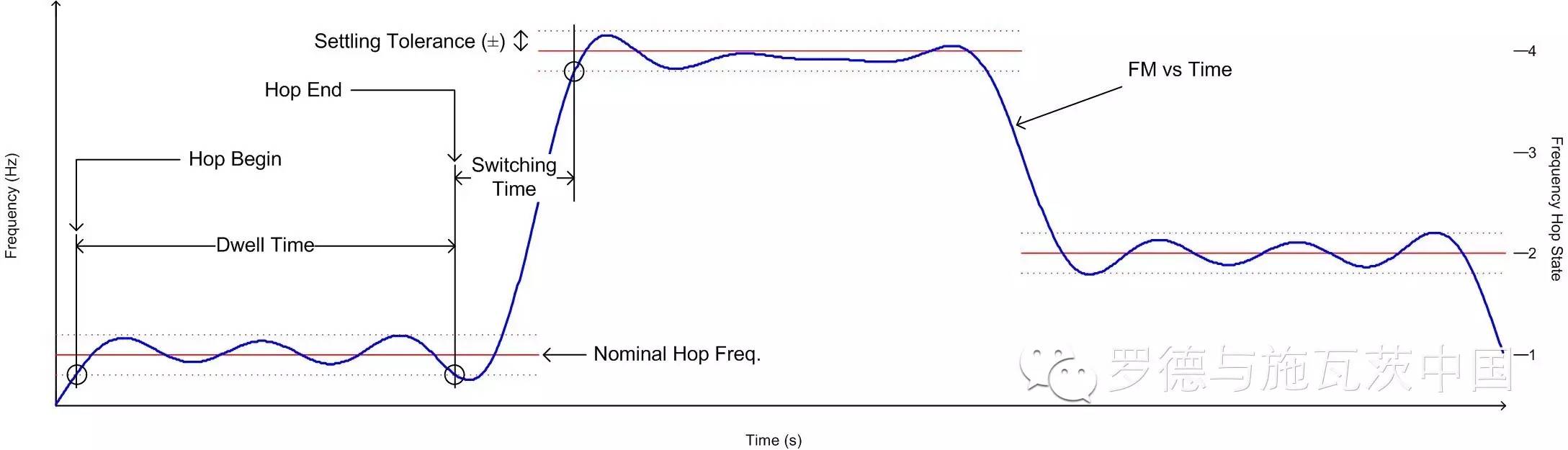

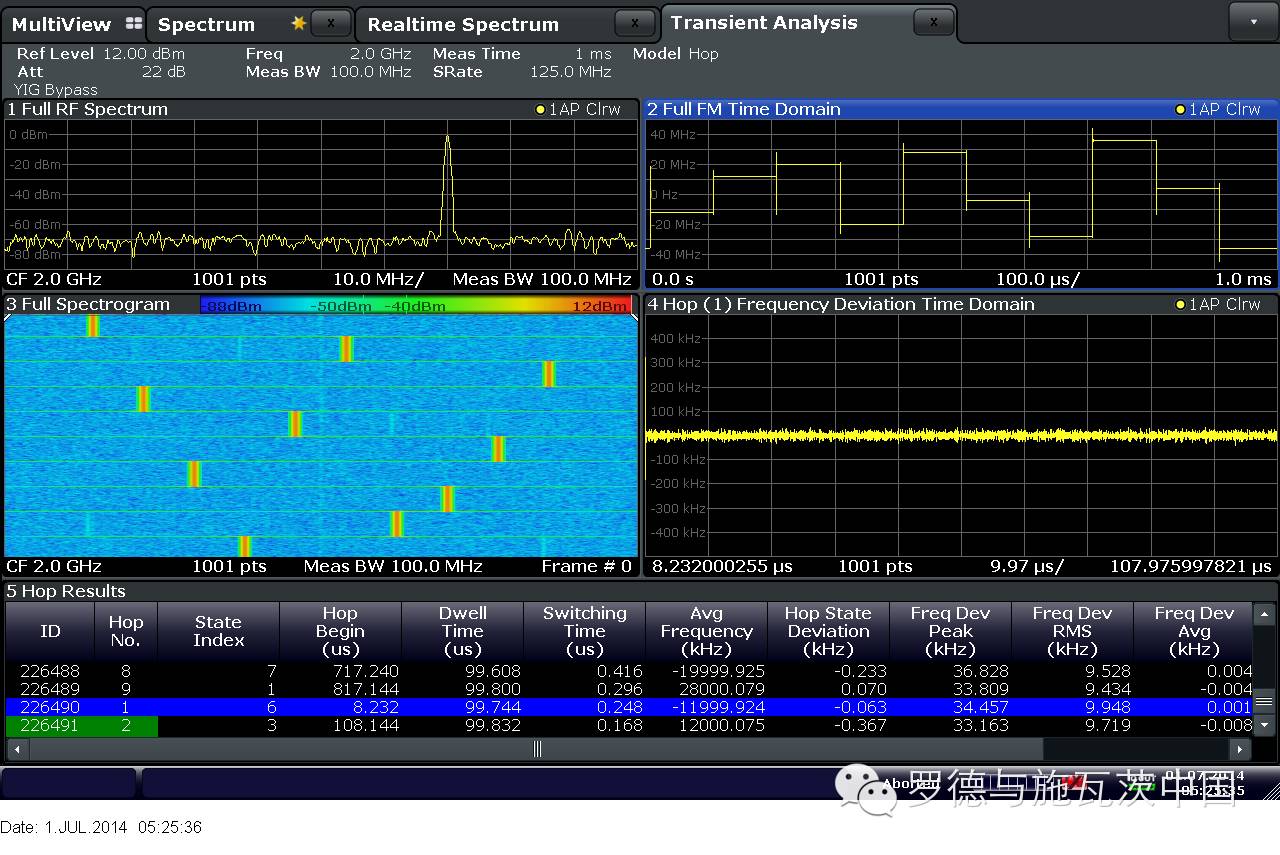

这里以一个10个捷变频点10万跳频速率频踪信号为例,图3显示的是捷变频频踪的实时频谱图,借助FSW的实时频谱功能,可以清楚的观测跳频信号的跳频频率集和那些常规测试手段难以发现的捷变频频踪中的瞬态杂散和泄露问题。图3中的下方红色标注的位置,可以看到本镇泄露信号,因为是大信号下面的小信号,所以常规频谱仪无法方便的看到。

图3 FSW显示捷变频的实时频谱

经过对信号的初步观测,就可以借助FSW的K60选件进行捷变频指标的方便测试了,图4是K60选件的测试起始界面,界面上可以实现多窗口显示,按照图上所显示的,其中包括频谱图、频率对时间趋势图、三维频谱图、每个捷变频点的频率偏差、测试项目表。其中测试项目表是把被测信号的所有要测试的指标按照表格的方式进行汇总。

图4 K60 测试界面

图4中的每个窗口都可以独立放大,也可以添加其他的测试窗口。比如对测试项目表放大后的图示如下图5:

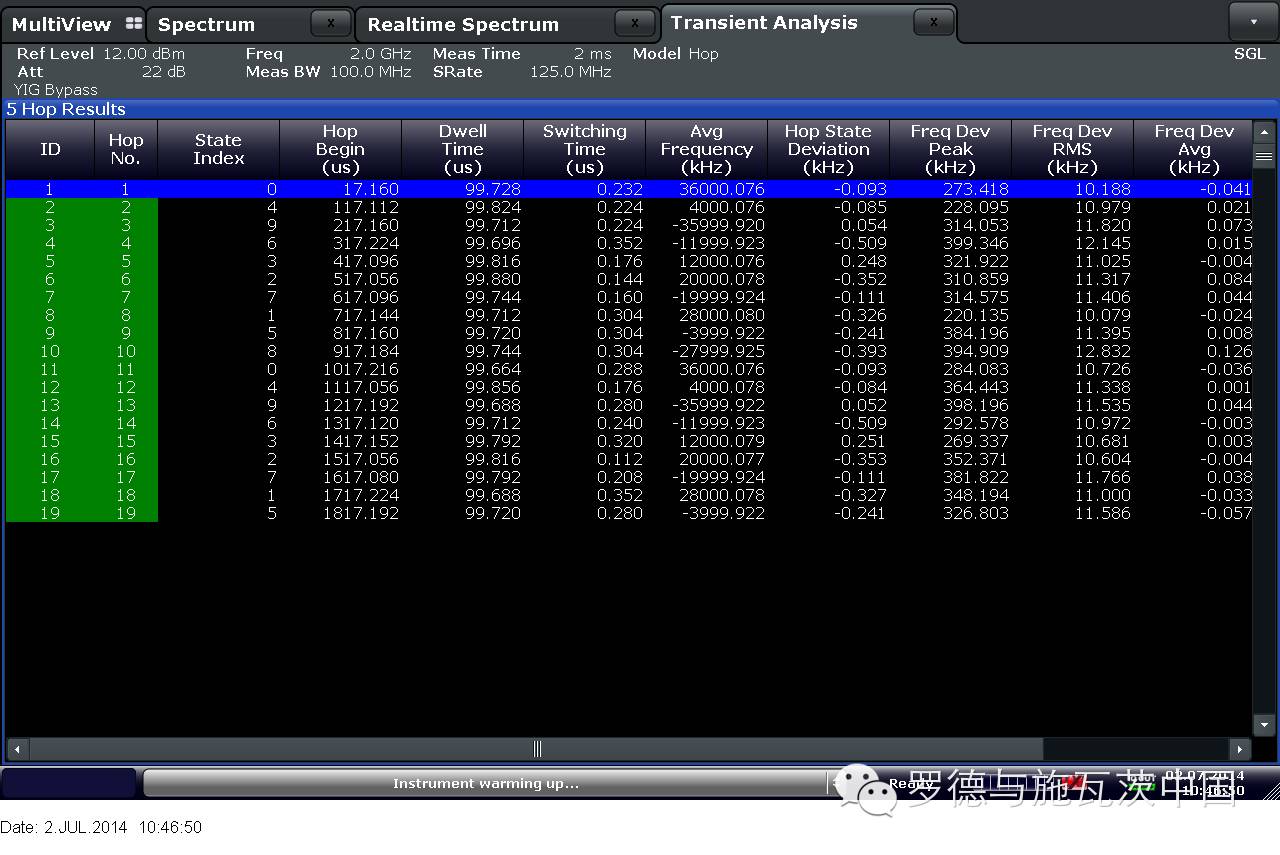

图5 K60自动测试结果显示

图5中显示了单次采集测试的结果,采集的长度是2ms, 该仪器支持的内存分析达到1G个样点,根据不同的带宽和采样率可以实现不同的测试时长,如测试带宽100MHz的情况下,最长可以采集3.3s的信号进行分析。从表格中的测试项目上可以看到该捷变频频踪的一些特性,测试结果如下:

跳频点状态(state Index):一共10个随机频点。

每个跳频点的时间(Hop Begin):每个跳频点的起始时间,第一个点的测试结果为17.16us

驻留时间(Dwell Time):每个跳频点的驻留时间,测试结果为99.728us。

频率切换时间(Switching Time):从一个频率到另外一个频率的切换时间,如频率1切换到频率4的时间是232ns。

平均频率(Avg Frequency):每个捷变频点和载频偏差精确频率。如第一个点的频率和载频的频率偏差36MHz。

状态偏差(Hop state Deviation):每个捷变频点和理想捷变频频率的偏差。如第一个点的测试值是93Hz。

频率偏差最大值(Frequency Deviation Peak):每个捷变频点在该点频率的稳定度偏差的最大值。如第一个捷变频点的偏差是273.418KHz。

频率偏差有效值(Frequency Deviation RMS): 每个捷变频点在该点频率的稳定度偏差的最大值。如第一个捷变频点的偏差是10.188KHz。

频率偏差平均值(Frequency Deviation Avg): 每个捷变频点在该点频率的稳定度偏差的最大值。如第一个捷变频点的偏差是41Hz。

平均功率(Average Power):每个捷变频点的功率值。第一个点的功率为-1.181dBm。

可以看出,通过K60选件对捷变频信号进行自动测量,不但精度高,而且可以大大提高测试效率。

4 结束语

以往对捷变频频踪测试没有一种便捷有效的方法,采用定频方式去测量,不但无法真正模拟真实条件下的测试状况,而且也给频踪的质量带来了性能的隐忧。借助R&S公司的FSW实时信号与频谱分析仪的跳频捷变频测试套件K60,实现了对捷变频频踪各个测试项目的全面的便捷性的测试方法,其具有创新的算法保证能够自动识别频率捷变,这大大提高了对捷变频频踪性能指标的信心,也大大提高了研发过程的工作效率。

-

L波段细步进捷变频频率综合器设计2010-04-22 2935

-

一种自主产生式的雷达回波模拟器中频部分的设计实现方法论述2019-07-16 2637

-

一种自主产生式的雷达回波模拟器中频部分的设计论述2019-07-19 1677

-

AD831的工作原理是什么?它在频踪式雷达本振中有哪些应用?2021-04-22 2795

-

VXI频率捷变雷达自动测试设备的设计2009-07-15 961

-

捷变频脉冲磁控管电性能测试方法 GB11487-19892010-05-04 1367

-

VSM-8500型广播级视音频捷变频邻频调制器2010-07-22 666

-

一种工作流系统在线监控方法_何频捷2017-03-14 1454

-

扫频仪测试实例介绍及扫频仪的原理与维修2017-11-18 1881

-

双踪示波器的使用方法及步骤分析(基本结构,工作原理及优点)2017-12-05 124043

-

led灯为什么有频闪_led灯频闪怎么解决_led灯频闪测试方法2018-01-17 94269

-

APHF系列宽带超高速捷变频频率综合器-小巧模块驱动快速跳频新2025-05-28 814

全部0条评论

快来发表一下你的评论吧 !