如何利用Speedgoat 系统验证 FPGA 算法的方法介绍

描述

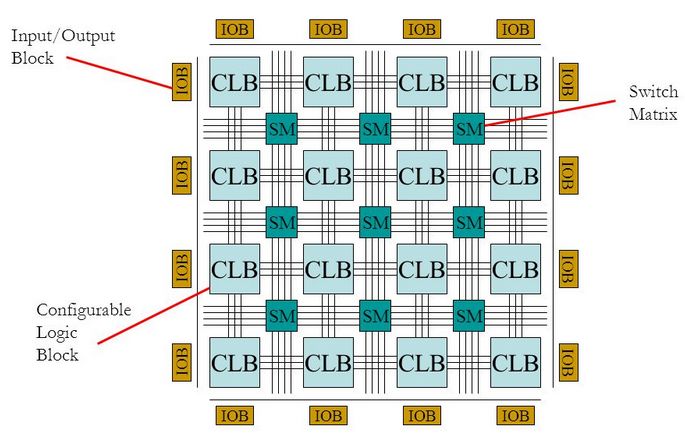

FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它作为专用集成电路(ASIC)领域中的一种半定制电路而出现,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。主要用于信号处理及各类高速模拟仿真。

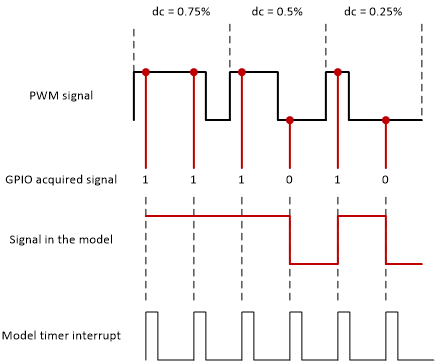

以PWM信号的捕获为例,说明FPGA与CPU(不考虑芯片专用外设)在处理上的差异。当CPU通过GPIO对PWM信号采样时,受限于CPU的运算周期,无法做到高速的采集,获得的信号与原始信号有较大偏差,并计算出错误的占空比:

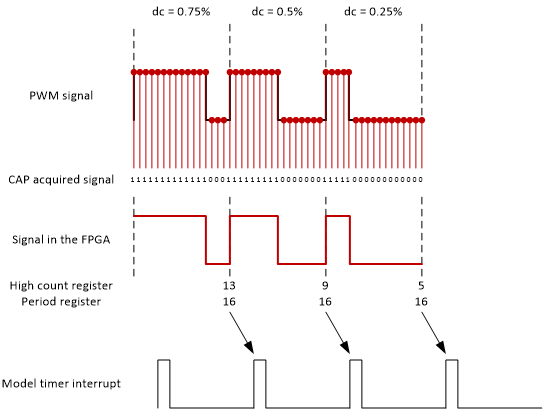

采用FPGA这种“硬电路”的方式采集信号,可以有效获得信号的信息,误差取决于采样周期(如100MHz下约为10ns):

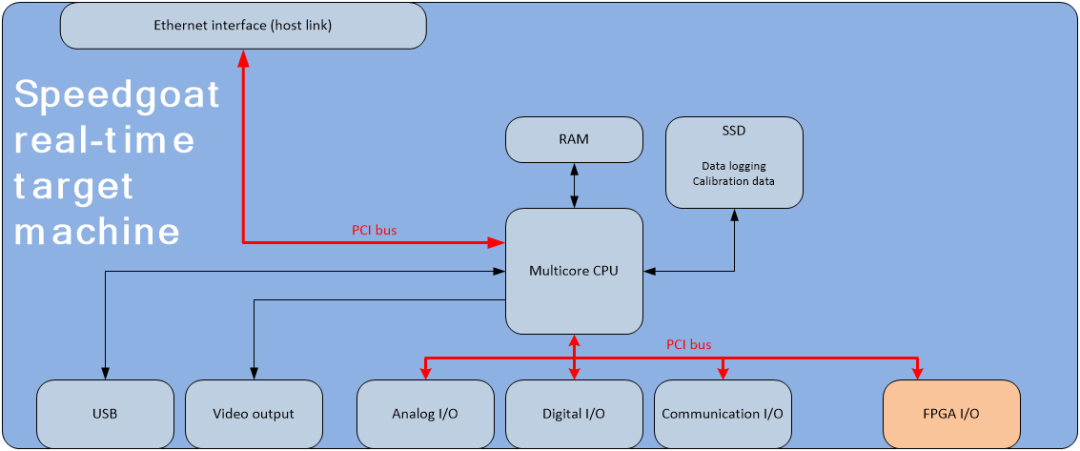

对于实时仿真而言,模型的计算只需要占空比信息即可,因此FPGA可以作为系统的“协处理器”存在,负责信号处理或高动态性部分模型运算,并将结果与CPU交互:

FPGA算法开发

FPGA的开发与传统CPU、DSP的开发有很大不同。FPGA以并行运算为主,以硬件描述语言HDL来实现。开发者需具备较强的数字电路知识及逻辑思维能力。

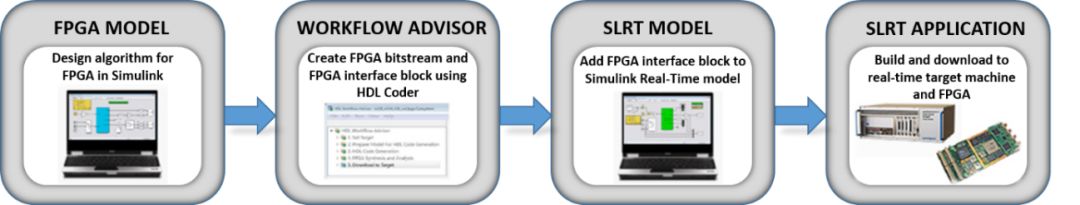

MATLAB/Simulink平台的HDL Coder工具箱,有效的降低FPGA算法开发的难度;使工程师只需具备基础知识即可在Simulink环境中搭建FPGA算法,并最终部署在Speedgoat或自己的FPGA平台上。以Speedgoat平台为例,基本步骤如下:

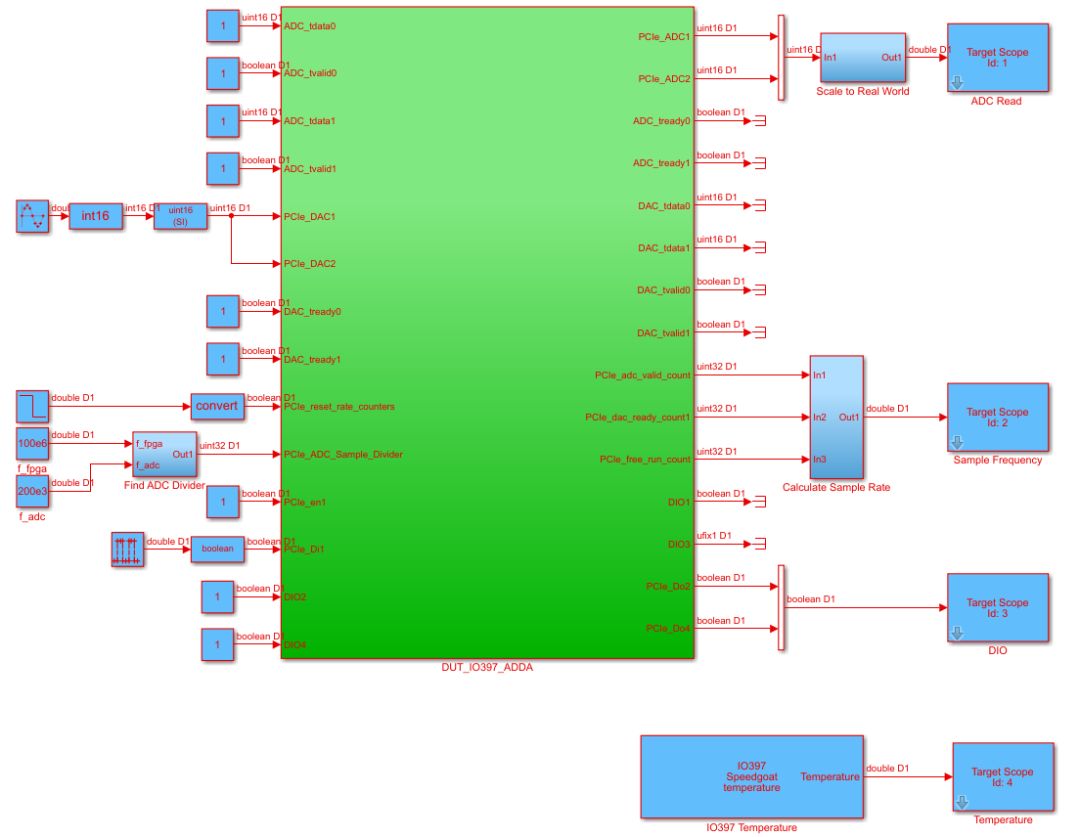

1. Simulink环境中搭建算法模型

开发者可以使用Simulink环境中的HDL Coder/DSP System Toolbox/Communication System Toolbox/ Vision HDL Toolbox等工具箱开发算法,并将算法放置在Subsystem内,仿真调试。Simulink环境支持以单精度浮点的方式开发FPGA算法,大大降低开发难度。

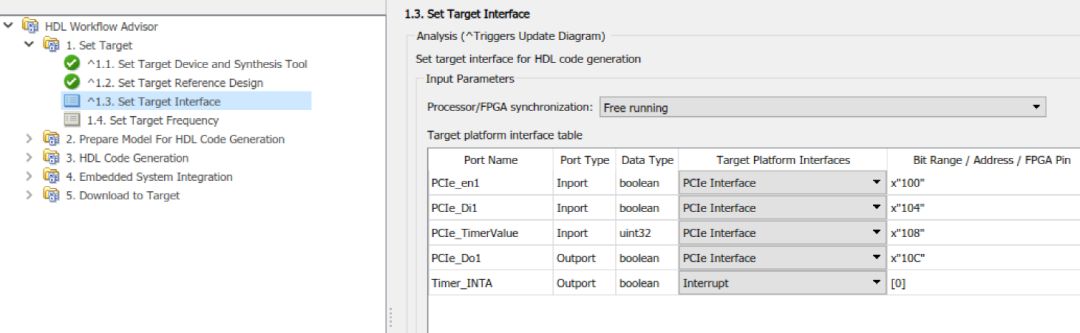

2. HDL Workflow Advisor

在Subsystem上右键选择HDL Workflow Advisor,并在弹出的界面中依次设置FPGA板卡、芯片主频,以及Subsystem inport和outport与硬件板卡IO通道的映射关系:

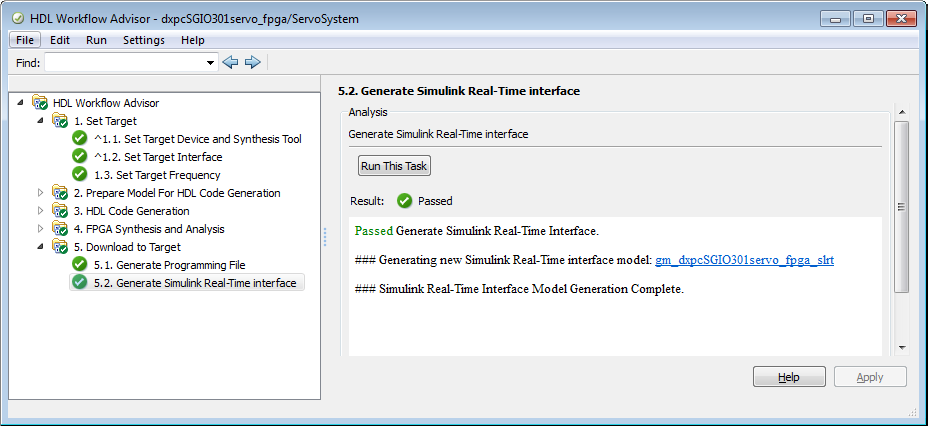

依次完成Workflow Advisor后续的task。HDL Workflow Advisor会完成模型检查、HDL代码生成、综合、分析、映射等工作(需要Xilinx相关软件,仅在后台调用)。在此过程中,依据设置,HDL Coder可以完成Delay Balance,关键路径寻找、代码模型链接等功能。

最终HDL Workflow Advisor可以生成一个接口模型,取代原先的算法Subsystem:

3. 编译下载运行

FPGA模型部分编译完,进一步完成整个模型的编译,生成可执行程序下载到Speedgoat硬件上,系统会自动区分CPU和FPGA,并配置两者间的通讯。

完整的流程如下:

详细流程可参见HDL Coder工具箱的帮助文档及Speedgoat相应帮助文档。

在不远的将来,MATLAB将完善物理模型对HDL代码生成的支持。届时物理模型在完成离线仿真后,可直接迁移到Speedgoat实时仿真平台,无缝过渡到基于FPGA的半实物仿真测试阶段,这对于电气、电力电子领域有重要的意义。

Speedgoat FPGA解决方案

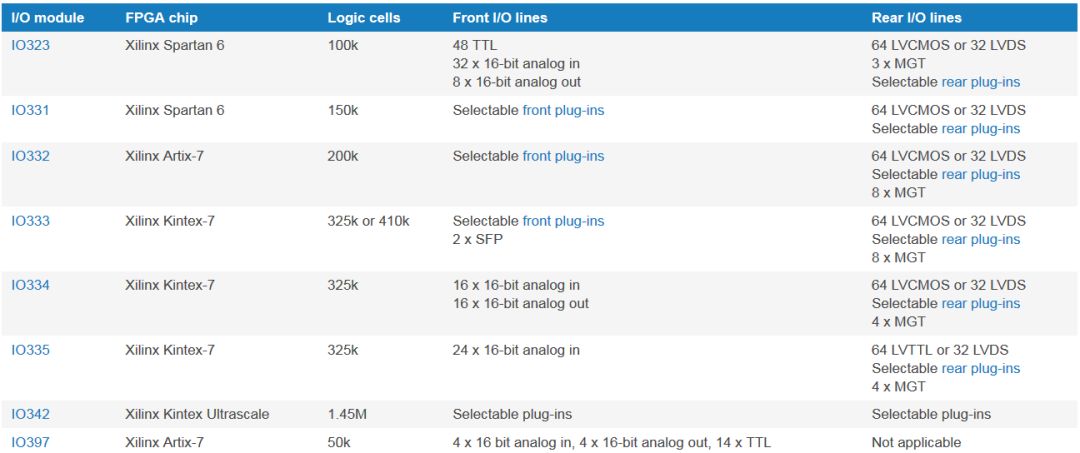

基于HDL Coder的模型化算法开发基础上,Speedgoat针对不同的应用领域,提供了大量的可编程FPGA硬件模块:

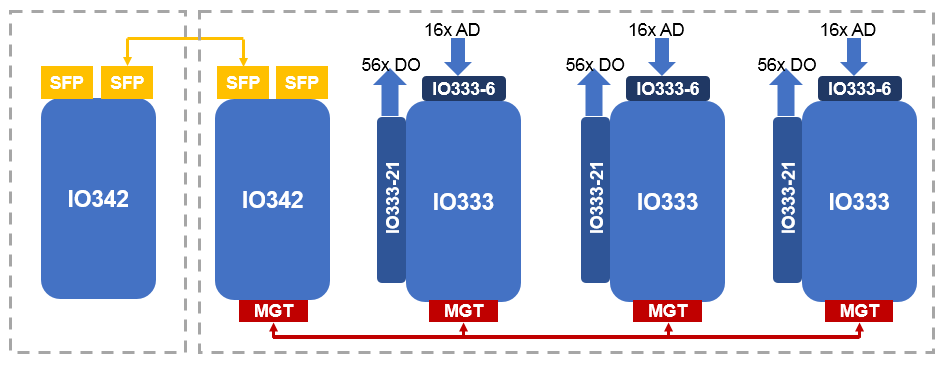

各模块具备不同的IO通道和芯片资源,完全支持HDL Coder的模型化算法开发。当单FPGA模块资源不够时,可通过Xilinx Aurora协议,将彼此直接连接,组成更大规模的FPGA“计算集群”:

-

在FPGA上建立MATLAB和Simulink算法原型的四种最佳方法2020-05-04 0

-

怎样去构建一种SoC系统验证平台?2021-04-28 0

-

介绍一个简单的存储系统验证平台tutorial2022-11-04 0

-

硬件验证方法简明介绍2022-11-26 0

-

基于Speedgoat的永磁同步电机控制Demo介绍2023-03-21 0

-

食品安全/质量管理系统验证问卷2010-02-02 346

-

基于FPGA的DSP算法快速验证2011-06-15 529

-

Xilinx发布Vivado 2015.1版加速系统验证2015-05-05 1187

-

基于FPGA的验证平台及有效的SoC验证过程和方法2017-11-17 13777

-

利用FPGA软硬件协同系统验证SoC系统的过程和方法2017-11-17 4417

-

有关FPGA设计验证的相关方法介绍-ppt资料下载2018-04-03 682

-

自动驾驶系统验证需要考虑的因素2019-07-11 3237

-

如何使用FPGA实现图像灰度级拉伸算法2021-04-01 919

-

基于架构设计的车载网联系统验证体系研究2024-01-24 622

全部0条评论

快来发表一下你的评论吧 !