关于一种实现条件编译的建模方法分析和介绍

描述

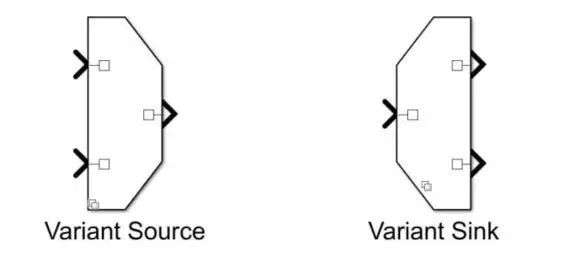

上次介绍过可以使用Variant Subsystem或者Model Variant实现带有条件编译的代码(条件编译助力Simulink模型平台化开发)。最近了解到,从MATLAB R2016a开始,又有一种新的方式可以实现C代码中的条件编译。这就是Variant Sourc模块的使用。

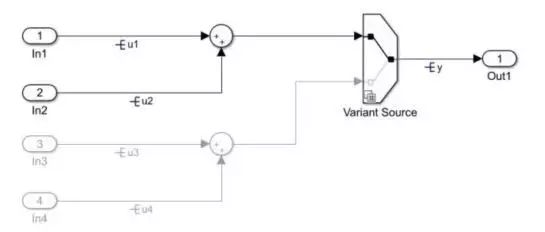

假设有如下模型:

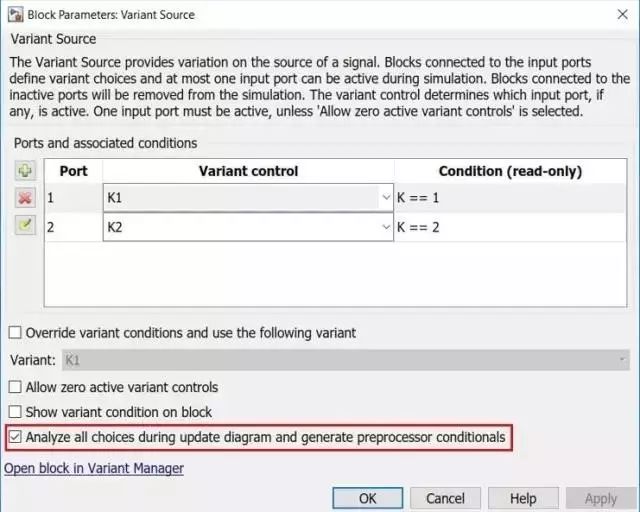

双击Variant Source模块,可以看到如下配置界面:

不难看出,除了要定义Simulink Variant对象K1、K2之外,还需要勾上Analyze all choices during update diagram and generate prepropcessor conditionals选项。显然,如果K==1条件成立,则Port 1分支对应的代码被编译,如果K==2,则Port 2分支对应的代码被编译。这里的K可以定义为Simulink Parameter对象,Storage Class定义为Define(Custom),并且需要指定宏定义的文件。

如此设置之下,得到的模型算法实现函数如下:

void testvariantSource_step(void)

{

real_T rtb_VariantMerge_For_Variant_So;

#if K1

rtb_VariantMerge_For_Variant_So = u1 + u2;

#endif

#if K2

rtb_VariantMerge_For_Variant_So = u3 + u4;

#endif

y = rtb_VariantMerge_For_Variant_So;

}

这种方式实现带有条件编译的代码也非常简单,条件编译的好处可以通过控制宏定义K控制需要编译哪部分代码,那么,如果不设置条件编译呢?

上述模型中,如果不再勾选Analyze all choices during update diagram and generate prepropcessor conditionals选项,我们得到如下代码:

void testvariantSource_step(void)

{

y = u1 + u2;

}

代码中只有当前参数条件下有效算法的代码。

跟上次介绍的条件编译相比,实现方式不同,应用场景也可能不同,如何取舍,这里就不去分析了。但是,在基于模型的开发模式下,到底在模型级别上做选择,还是通过C代码级别的条件编译做选择,这是个值得我们思考的问题。

-

讲解消息分发的一种编译期实现法2023-08-23 1044

-

一种AUTOSAR软件架构中RTE的实现方法2022-07-13 790

-

介绍一种使用WSL来编译nodemcu固件的方法2022-02-15 981

-

一种新型的交通视频背景建模方法2021-05-08 993

-

求一种有限元分析中PCBA的简化建模方法2021-04-19 1768

-

c语言之条件编译技巧与示例分析2020-08-26 3449

-

一种分层递阶机制的实时多层建模方法2018-01-16 1051

-

一种三相SPWM逆变器的建模和控制方法_董锋斌2017-01-22 963

-

一种AMR磁罗盘的误差建模与校准方法2016-08-17 2073

-

一种面向动态分析的PCB板等效建模方法_刘孝保2016-06-16 606

-

一种自动布局的BEPL建模工具设计与实现2010-01-15 618

-

一种窄带非高斯建模方法2010-01-12 808

-

一种复合故障预测动态建模方法2009-12-14 880

-

一种Flyback软开关实现方法2009-07-06 2294

全部0条评论

快来发表一下你的评论吧 !