关于DDR终端电压调节器的性能分析和应用

描述

随着工艺的进步,逻辑集成电路的工作电压越来越低,速度也越来越高。很多标准逻辑器件的接口驱动器都是对称的上下拉结构,只要相应位置的电压低于某个值或高于某个值,我们就可以得到确切的逻辑0或逻辑1状态。但是,随着电路工作频率的提高,这种简单的逻辑判断方法有时候就行不通了,于是就有新的逻辑接口层出不穷地冒出来,这些新的接口通常都有一个很重要的特征:它们是对称的,外电路也是对称的,下面的内容算是这样的一个例子。

DDR SDRAM是SDRAM的升级版,它可以在时钟信号的上升沿和下降沿各进行一次数据传输,因而可以在相同的时钟频率下将数据吞吐速率提升一倍。随着DDR存储器的潜力被不断挖掘,我们已经见到了DDR、DDR2、DDR3、DDR4和其它的一些特别版本,它们的工作电压越来越低,时钟速度也越来越快,但它们所采用的数据接口的逻辑却没有什么大的变化。实际上,这些存储器的数据接口所采用的逻辑都是一种被称为SSTL的逻辑,这个称呼是“Stub Series Terminated Logic”的首字母缩写。我实在不知道要如何用中文来准确地表达这个称呼,因为我不知道定义者是如何定义Stub的意义的,虽然我可以凭自己的猜测进行估计,但我觉得最好还是不要这样做。对此感兴趣的读者可以参考一个来自百度百科的翻译,它把SSTL称之为“短截线串联端接逻辑”。

SSTL的第一个版本是在1996年发布的,它所针对的应用是工作频率高于125MHz的存储器,由于工作电压为3.3V,这个版本被称为SSTL-3。SSTL的后续版本有SSTL-2、SSTL-18和SSTL-15,它们分别针对工作电压为2.5V、1.8V和1.5V的应用。

从驱动器的角度来看,SSTL的电路结构是这样的:

驱动器的输出是VOUT,经过串联电阻RS和传输线以后到达接收器一侧的电压是VIN。很显然,VOUT和VIN的值与驱动器的驱动能力有关,也和驱动器的供电电压VDDQ 、串联电阻RS 、终端匹配电阻RT和终端电压VTT的值有关。

对于SSTL-3来说,VDDQ=3.3V,VTT的取值是VDDQ的0.45倍,它被设定为1.5V。其他版本的SSTL都将VTT设定为VDDQ的0.5倍。

接收器在判断接收到的信号是高电平还是低电平的时候需要一个参考电压VREF,VREF的值和VTT的值是相同的。只要VIN电压高于VREF某个电压值即可判定输入为1,VIN电压低于VREF某个电压值即可判定输入为0。由于高速传输的信号很容易发生畸变,也很容易受到干扰,所以VIN高于VREF或低于VREF的量在很小的情况下就需要接收器判断出数据的真实值。在这里,数据0和1的电压相对于VREF基本上是对称的,与VTT之间的关系也是如此。

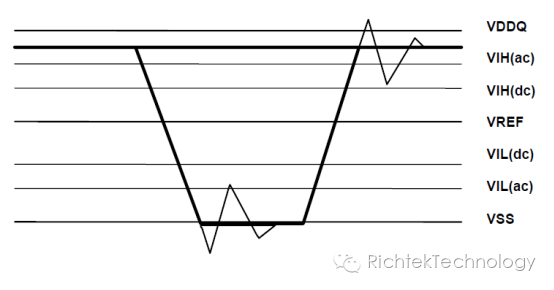

上图显示的是VIN的可能的波形的样子。当VIN电压高于VIH(dc)的时候,VIN的电压所代表的就是数据1;当VIN电压低于VIL(dc)的时候,VIN的电压所代表的就是数据0。叠加在波形上的振荡波形被称为交流部分,它们属于干扰,是我们不希望出现的东西,所以在标准中就规定了这些信号的幅度限制。很显然,如果交流部分的幅度下探到VIH(dc)以下或上探到VIL(dc)以上,则数据1或0的状态就受到了破坏,因而对它们的限制是很合理的。

由于VREF=VTT,在数据为1时就有电流从VIN处经电阻RT流入VTT,在数据为0时就有电流从VTT经电阻RT流入VIN处。

很显然,电流从VTT流出将导致VTT电压的降低,电流流入VTT则将导致其电压的升高。为了保证VTT电压的稳定,为VTT供电的电源管理电路需要在VTT电压降低时向VTT提供电荷(吐出电流),在VTT电压升高时将VTT处的电荷吸走(吸入电流),实现这样功能的电源器件被称为DDR存储器数据总线终端电压调节器,这个称呼实在是太啰嗦了,所以比较简单的说法是DDR终端电压调节器或DDR终端稳压器。我自己会比较喜欢DDR终端电压调节器这个说法,我很难说清楚为什么是这样,但我有一种感觉是来源于这种器件与普通的稳压器是有很大的区别的缘故。

DDR终端电压调节器的电流吸入和吐出的能力需要有多高呢?这是可以进行估算的,估算的时候需要考虑很多因素:总线的宽度(同时传输的数据的位数),需要终端匹配的存储器的数量(如果有多个存储器模组,总线就会有多个分支,每个分支的终端都需要进行匹配处理),VDDQ和VREF的高低以及终端匹配电阻RT的大小,信号的实际幅度(VIN的电压与VTT之间的压差直接影响着电流的大小)。

关于RT的大小,这其实是与总线的阻抗有关的,其取值通常为50Ω,但另外一种配置就是25Ω,这将导致电流增加一倍的效果。

早期的PC在解决这个问题的时候都是采用大电流的Buck架构开关转换器来完成DDR存储器的终端匹配电源供应的,我猜想这是基于如下的考虑:当所有的数据线都处于0或是1的状态时,VTT电源要吐出或是吸入的电流是巨大的;工作在PWM模式下的Buck既可以吐出电流,也可以吸入电流,它吸入的电流通过Boost的方式被送入Buck的输入端,还可以起到回收能源的效果。

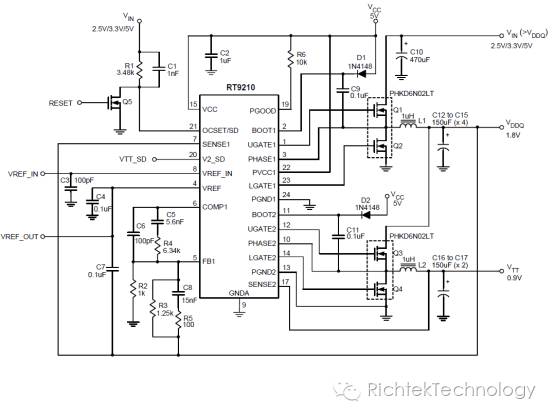

上图截取自RT9210的规格书,这是立锜的一款老产品,其中就含有两组Buck,可以分别为DDR存储器提供VDDQ和VTT供应,DDR存储器需要的VREF等电压也一并提供,但是,这样的产品却不是今天DDR存储器供电的常见选择。

常见的选择是这样的:

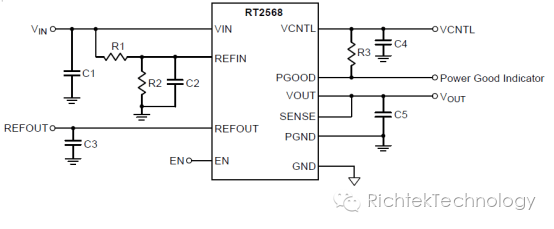

这是为VTT和VREF供电的电路图,所选型号是RT2568,这是一款工业级的DDR终端电压调节器,具有3A的电流吐纳能力。其内部电路框图是这样的:

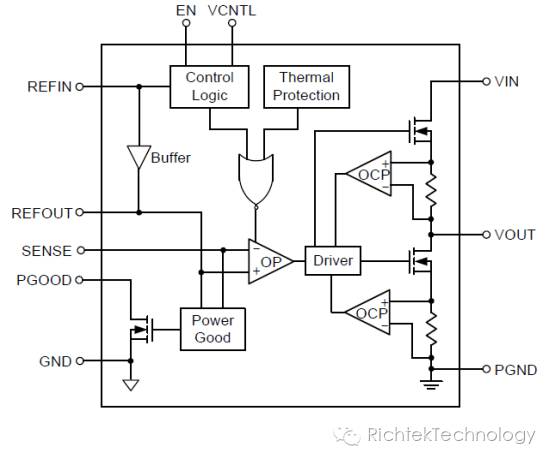

从中可以看到,从SENSE端检测到的输出电压VOUT(也就是我们需要的VTT)被拿来与经过缓冲处理的REFIN即REFOUT进行比对,如果发现VOUT高了,输出部分的下面那个MOSFET就会导通将VOUT端的电荷吸走以降低其电压,反之则导通上面那个MOSFET让电流从VIN处流入VOUT使输出电压上升,从而使输出电压VOUT稳定在和REFIN相同的电压上。

本来过去都是使用Buck来完成此功能的,现在大家都选择使用这种线性的方式,这种转换是如何完成的呢?要了解这一点,需要我们将目光投射到十几年前的***。

1998年9月,立锜科技在***的新竹成立,来自各种不同专业的大约15个人一起成立了一家全新的IC设计公司,定位于专业的模拟IC设计方向,启动资金为大家凑集起来的500万元新台币。由于这个时期是PC代工业在***正红火的时候,他们看上了PC应用中的电源管理需求,决心进入其中为大家服务并希望能藉此从中分到一杯羹。

在成立的当年(1998年),立锜的第一颗产品RT34063A就开发完成并投入量产。

第二年(1999年),立锜自制的测试机台RTT正式启用。同时,PC主机板的四合一PWM IC和ACPI 控制器也开发完成并投入生产。对于IC设计公司来说,测试机台的投入在成本上是排在第二位的,所以,立锜自制测试机台的做法对于降低成本、提升竞争力是很有帮助的。

第三年,也就是2000年,立锜迁入新的公司地址,并且通过了ISO2001的认证,用于USB端口的保护IC也上市了。与此同时,他们对DDR存储器终端电压调节器要采用Buck来完成的做法产生了怀疑,他们认为根本不需要那么大的电流吐纳能力就可以满足实际应用的需要,因为实际应用中出现数据总线上的数据同时为0或同时为1的机会是极少的。只要有0和1同时出现,流过RT的电流就会有相互抵消的效果。即使同时为0或1的数据会偶然出现,其延续时间也极短,由此造成的VTT电压波动是很小的,而且很容易被电容的储能能力弥补,于是乎一颗划时代的产品就出现在了这个世界上,它的型号是RT9173。直至今日,RT9173仍在生产中,你还可以从立锜科技的官网上查看到它的规格书。

RT9173的出现对市场的影响是巨大的。与Buck相比,它实在是太简单了,成本差异巨大,所以迅速获得了市场的认可,成为立锜在最短时间内累计出货量超过1亿颗的产品。而在这个时候,我还没有进入立锜,甚至还没有进入IC这个行业。

在我进入立锜以后,有人对我说后来的立锜上市就是因为RT9173,因为它为立锜赚了太多的钱。我很难说这一传说所说的是否是事实,因为其实在RT9173出现之前立锜就已经有了很多好产品,而在2003年上市以前我在深圳推给客户的产品还有很多强大的东西,关心我们的微信号的老朋友们在我过去的文章中已经多多少少看到过一些,所以我觉得把所有的功劳都放在RT9173上是有点过头的,但它的功劳肯定是大大的。

RT9173的设计是有专利的,它也是立锜的第一颗拥有专利的产品。但是,那时候的立锜还太过弱小,对于专利的理解也还不到位,所以,它的专利文件在写法上太过具体,其覆盖面积实在太小,保护自己的作用实在是不大,所以,后来的市场上就出现了很多和RT9173长得一模一样的产品。我不知道那些大公司抄袭小公司的产品是从何时开始的,但这大概是算一例吧,这也是立锜第一次成为被模仿者,而这对立锜来说还仅仅是个开头。

-

LP2996 DDR终端调节器资料说明2020-07-09 0

-

TPS51100 3-A接收器/源DDR终端调节器2020-10-15 0

-

LP2995DDR终端输出调节器相关资料下载2021-05-20 0

-

带限流器的电压调节器2009-04-17 1363

-

电压调节器分类及调压原理解析2010-08-09 2735

-

开关调节器的分析2011-01-01 915

-

电压调节器的分类_电压调节器的调压原理2020-01-10 12914

-

汽车交流发电机电压调节器原理2020-01-14 34603

-

3端电压调节器GN78L05ASR规格书2022-12-29 408

-

3端电压调节器GN78M05A规格书2022-12-29 401

-

在DDR存储器终端电压电源中增加电压下降可降低输出电容2023-03-10 1139

-

3-A信宿/源DDR终端调节器TPS51100 数据表2024-03-13 131

-

DDR终端调节器LP2998/LP2998-Q1数据表2024-03-28 200

-

DDR终端调节器LP2996-N LP2996A数据表2024-04-07 118

-

DDR-II终端调节器LP2997数据表2024-04-07 88

全部0条评论

快来发表一下你的评论吧 !