了解SMT参数及SMT参数对BLR的影响

描述

优化速度和时间不仅是在奥林匹克赛道上实现金牌愿望的要素,而且是用于封装到封装技术的内存到底部(逻辑)封装的坚固表面贴装(SMT)工艺的先决条件(POP)。 PoP技术具有镀锌半导体封装,因为它具有减少外形尺寸和小型化的先天优势,支持大批量制造(HVM)中的大量消费类和便携式电子产品。由于其在十多年的历史中具有强大的HVM历史,PoP是需要内存/处理器集成的汽车高级驾驶员辅助系统(ADAS)应用的理想技术。

了解SMT参数的影响

确保在存储球上适当的通量覆盖率首先要了解磁通量储存器中沉积时间的动态以及与提取的存储器封装相关的速度离开通量储存器。掌握这些条件可以为解决汽车设备的侵蚀性缺陷级别要求设定路径。例如,如果记忆球上的助焊剂覆盖率不足或过大,则可能的情况是违反焊球上50-70%磁通高度体积的典型经验法则。在过度覆盖的情况下,由于表面张力的影响,助焊剂材料可以迁移到存储器封装焊接掩模表面(参见图1)。这种情况可能导致SMT球缺口问题。另一方面,磁通覆盖不足会导致非湿路和电气开路(如图2和3所示)。

图1此图示显示球高度过高。

图2记忆包球偏移导致非湿(a)和球短路(b)如图所示这个x射线图像。

图3这是一个横截面记忆包球短路。

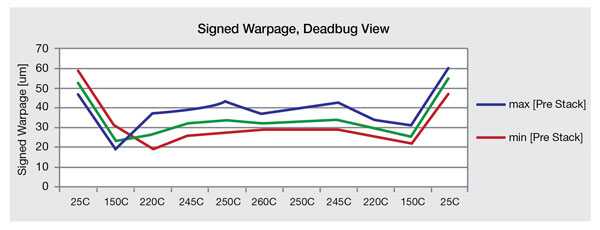

提取速度是控制磁通覆盖均匀性的另一个关键参数。开发安全的速度范围以抵消助焊剂穿线效应,以实现存储器封装焊球到底部封装的最佳提取和助焊剂转移,这是提高SMT产量的重点项目。通量深度和提取速度是串联的,很像半导体芯片和封装,因为它的相互作用取决于另一个。优化通量深度而不是提取速度(反之亦然)可以产生通量体积的变化,这反过来将增加焊点完整性的变化。当然,前面提到的SMT指南取决于存储器和底部封装之间的翘曲一致性(参见图4),这是推动制造汽车无缺陷SMT工艺因素的典型第一步 - 专注于PoP组装。通量变化的分歧不仅会导致SMT产量问题,还会导致板级可靠性(BLR)期间焊点裕度减小。

图4此图显示了叠前配置中内存和底部封装之间的翘曲一致性。

SMT参数对BLR的影响

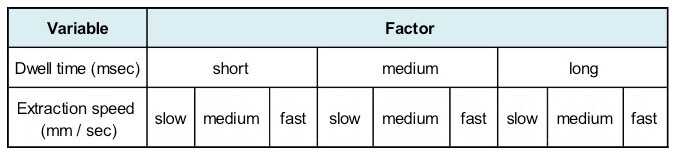

为了进一步研究非优化SMT条件的BLR影响,例如存储器封装BGA焊球的焊剂沉积时间和存储器封装离开浸渍托盘的提取时间,进行了实验设计(DoE)。在该DoE内(参见图5),在短,中,长停留时间评估了助焊剂浸渍盘中存储器封装的沉积时间。

图5此表描述了DoE。

时间谱的高端是低端的3倍。类似地,在慢,中和快三个级别评估存储器包提取速度。提取速度的高端约为低端的2.5倍。在-40℃至125℃(根据IPC 9701)条件下监测BLR性能,以确定对上述SMT参数的响应,作为存储器封装角和非角焊料球的原位电阻变化测量的函数。通过两个独立的测试网监视存储器封装角和非角BGA,以便在BLR期间清楚地指定存储球易感性。能源部背后的驱动力是为汽车设备保持令人羡慕的零缺陷目标,以了解PoP SMT装配过程中的工艺余量。

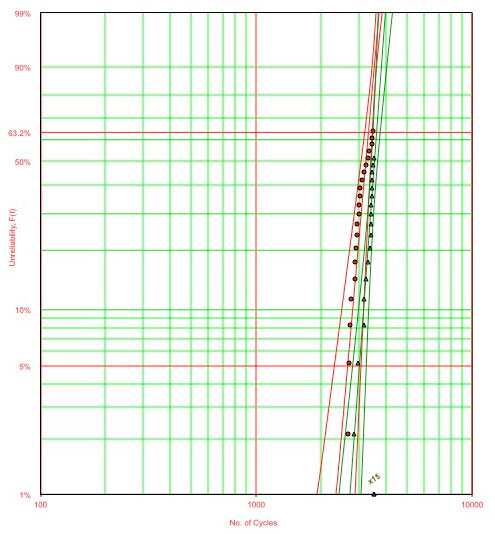

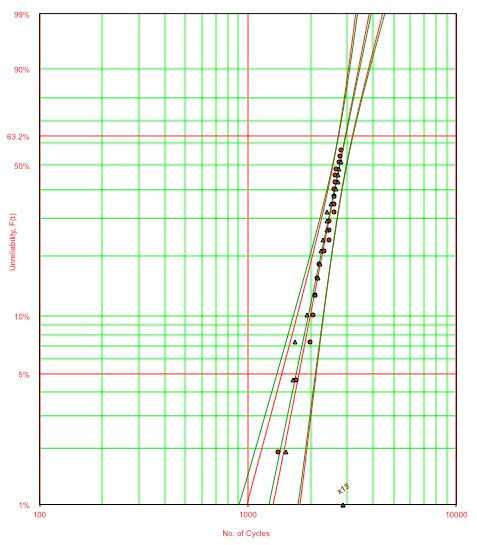

SMT表征的结果很有趣,在某些情况下违反直觉。在停留时间和提取速度处于该范围的高端的情况下(高意味着更长的停留时间和更快的提取速度),可靠性裕度降低,如Weibull分析所示,在5%的循环到失效时(参见数字) 6 - 8)。该假设是较长通量停留时间的组合导致材料体积沉积在存储器封装表面上,从而减少焊球本身上的通量。来自沉积过程的焊球上的通量体积的不均匀性以及更快的提取速度导致不稳定的通量转移的完美风暴。由于焊剂转移不良,冶金焊接过程会在焊料回流过程中受到影响,这会对焊点可靠性产生不利影响。

图6SMT DoE表征的结果很有趣。

图7这是一个显示优化条件的内存非角(红色)和内存角(绿色)的Weibull图。

图8内存非拐角(红色)和记忆角(绿色)的Weibull图显示非优化条件。

-

手动SMT展示jf_24750660 2023-03-29

-

SMT基本工艺2010-11-26 0

-

SMT基本常识—SMT元器件种类2014-05-28 0

-

细化了解SMT加工技术,掌握好SMT加工2014-06-07 0

-

SMT基础了解2016-05-24 0

-

SMT02现货SMT02信号源2018-01-13 0

-

SMT和SMD有什么区别呢?2019-03-07 0

-

影响SMT锡膏特性的主要参数2019-09-04 0

-

E4418CORE-V1C电气参数及SMT工艺2016-08-08 770

-

有哪些工艺参数与因素会对SMT贴片焊膏的印刷质量造成影响2020-01-10 2922

-

SMT模板印刷的两种操作方式及技术参数设置2020-02-03 6031

-

SMT贴片机编程过程中需对哪些参数进行操作2020-03-21 5929

-

SMT贴片加工中印刷工艺参数设置起到怎样的重要作用2020-06-08 4646

-

SMT工厂的贴片工艺基本流程和原理2020-06-12 11855

-

SMT贴片工艺参数的设置包括哪些2021-06-15 2535

全部0条评论

快来发表一下你的评论吧 !