最佳DFT设计实践的详细过程解析

描述

1。简介

SoC子组件(IP)通常来自各种来源 - 内部和外部 - 因此设计人员必须确保RTL是可测试的。如果RTL存在可测试性问题,则无法满足测试覆盖率目标,并且需要修改RTL,这意味着需要对合成,验证和自动测试模式生成(ATPG)进行多次迭代。

这里我们将讨论基本的设计实践,以确保适当的可测试性。

2。时钟控制

对于ATPG工具生成模式,翻牌的时钟和复位必须是完全可控的;也就是说,工具可以在需要时触发时钟 - 它不能被任何其他不可控制的信号门控。

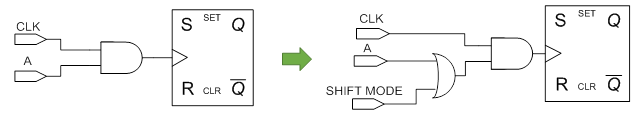

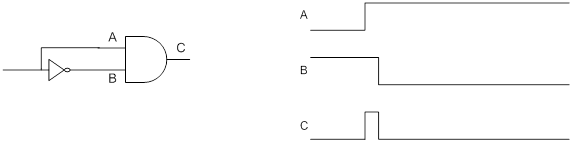

2.1由组合逻辑门控的时钟

In如果时钟由组合逻辑选通,则应使用移位/测试模式信号添加超控,以确保正确的移位和放大。捕获时钟传播。

图1:移位期间SHIFT_MODE = 1

2.2内部生成的时钟

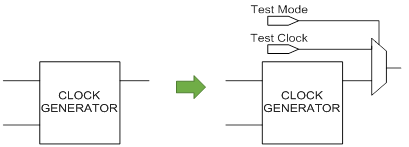

对于所有内部生成的时钟,应提供旁路。如果需要这个时钟,比如我们需要PLL时钟进行全速测试,那么就应该在它们上面添加一个时钟控制逻辑。

图2:绕过所有内部生成的时钟

这方面的一个例子是时序生成的时钟:

这里的时钟由触发器的输出产生,因为这个生成的时钟不能由ATPG工具直接控制,我们需要添加时钟控制逻辑。

图3:从触发器产生时钟的旁路

2.3测试时钟选择

必须确保测试时钟频率始终大于或等于功能时钟频率,这样我们就不会最终对逻辑进行测试不足。

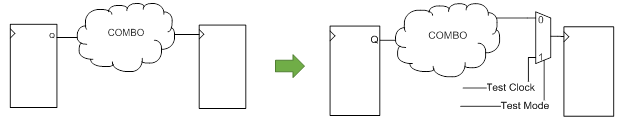

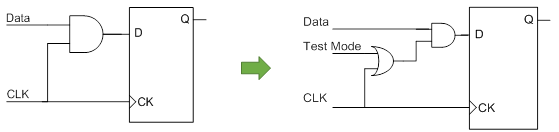

2.4使用时钟作为数据

当时钟用作设计中的数据时,必须始终确保我们使用测试模式信号进行门控此数据路径(即数据锥的时钟)。否则可能导致竞争条件产生不准确的模拟结果。

图4:消除竞争条件

3 。非时钟锁存器

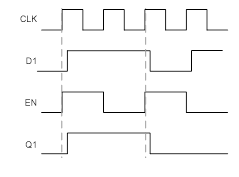

静态时序分析(STA)团队仅关闭那些时钟控制的顺序元素的时序。如果锁存器的使能/时钟来自触发器的输出,则STA团队不检查它的时序,这可能导致错误的数据锁存。它将在模拟或硅片上捕获。如果锁存器的使能是有效时钟(门控或非门控),则可以防止这种情况。

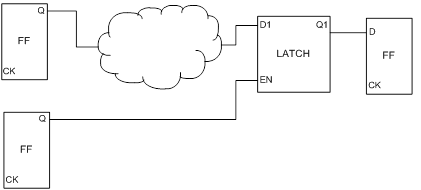

图5:未计时锁存器

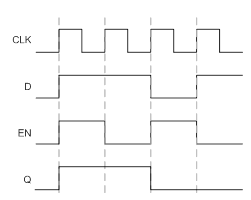

零延迟(ATPG/空闲):

生成模式时的ATPG工具适用于零延迟型仿真模型。数据在时钟边缘之前被采样,因此从工具的角度来看,在这种情况下,在模式生成期间输出总是很高。

图6(a ):零延迟

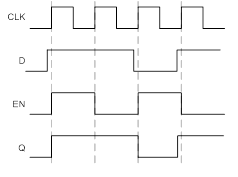

数据相对于时钟偏差(模拟):

在仿真中,由于数据和时钟之间的设计偏差,我们可以有两种情况,数据来自早期或晚期,在这两种情况下,我们都将开始失败。

图6(b):早期数据

图6(c):数据延迟

4。复位控制

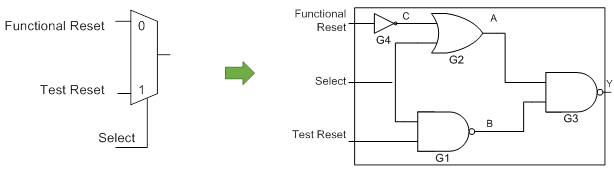

如前所述,触发器的时钟和复位必须是完全可控的。为实现此目的,将多路复用器置于复位路径中,如下所示。多路复用器的第一个输入是如前所述的功能复位。第二个输入是DFT(测试)控制的RESET,DFT使用选择线(测试模式)在测试模式下切换到受控复位。

图7:使用多路复用器进行复位控制

4.1复位路径中的开关逻辑级联

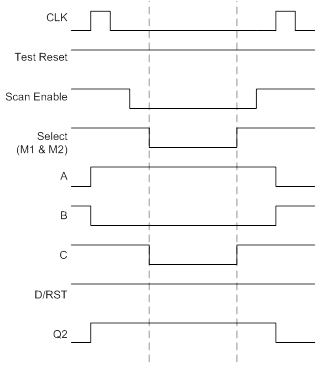

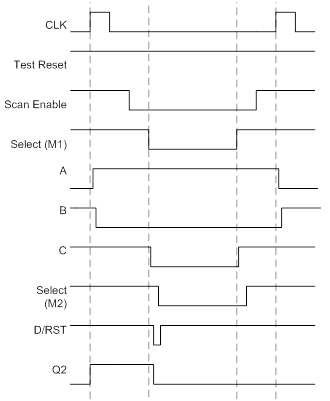

选择信号(重置覆盖)不由定时组计时,因此该信号中的任何随机偏差都不得影响任何触发器的状态。如果两个或多个这样的开关逻辑如图所示级联,这可能会导致触发器的RESET引脚出现故障,从而破坏其状态。

图8(a):级联复位控制逻辑

零延迟(ATPG):

由于ATPG的零延迟,选择线M1& M2将同时切换,因此复位RST始终为高。

图8(b):零延迟ATPG

M1与...之间的延迟M2(模拟)

由于互连延迟,M2进行后期转换而不是M1,导致复位时的毛刺复位。

图8(c):真实模拟场景

为了解决这个问题,只应使用一个多路复用器在重置路径中。

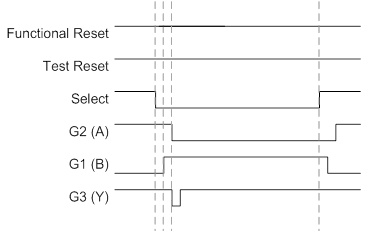

4.2用于控制复位的开关逻辑的合成

如上所述,在复位翻牌前添加多路复用器。在合成期间,该多路复用器可以转换为复合门(AOI - AND OR INVERT),如图9(a)所示。

图9( a):合成的多路复用器

这种情况可能会导致触发器复位时出现毛刺,导致错误输出。

图9(b):失败的情况

为防止毛刺,应使用RTL中的pragma保留此多路复用器,以便将逻辑合成为无干扰的多路复用器,而不是任何随机的AOI组合工作作为多路复用器。

5。组合逻辑输入的常见来源

组合逻辑(例如2输入AND门或2输入OR门),其输入由相同的源驱动,其中一个被反转将无论驱动节点的状态如何,都保持相同的恒定输出值,但当驱动节点改变状态时,输出可能包含一个毛刺。

图10:具有公共输入源的两个输入AND门

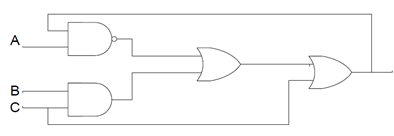

6。组合循环

当组合逻辑的输出反馈到其输入之一时,形成组合循环。 ATPG工具模拟设计,假设组合元素中的零延迟,这可能导致一个或多个输入组合的未确定输出。

图11:组合循环

如上所示,输入组合(A,B,C)=(1, 0,0)将在电路中产生振荡。为了防止这种情况,该工具打破了循环并将其建模为反馈路径中的TIEX块,从而导致覆盖范围丢失。因此应该避免这种循环。

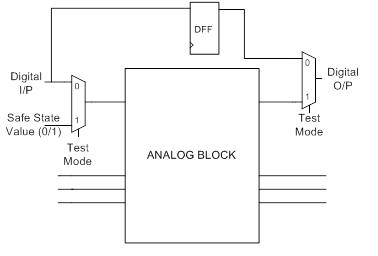

7。模拟模块

使用ATPG工具时,测试期间所有模拟模块都需要特殊处理。许多模拟模块都可以嵌入数字逻辑,我们应该确保所有这些逻辑都是可测试的。模拟模块接口的数字输入/输出需要完全可控和可观察。同时,模拟输入/输出应包装或安全说明。可以根据测试用例要求将模块的模拟部分保持在低功耗状态(断电或休眠),以及模拟输出处于高阻态或驱动恒定值,因此需要特别小心在这种情况下,通过安全地说明阻塞来进行护理。

8。电压和温度触发屏蔽

SOC内置电压和温度检测电路,以便在超出规定范围时产生中断。在测试期间,这些信号需要被禁用或屏蔽,因为有多个测试,如极低电压(VLV)测试,高压应力测试等,如果这些中断信号未被屏蔽,它们将开始显示失败。

图12:模拟包装器

9。结论

使我们的设计对DFT友好非常重要。上面的简单实践可以节省大量的设计时间,精力和挫折感。因此,建议设计人员确保遵循所有上述设计实践。

- 相关推荐

- 热点推荐

- PCB打样

- 华强PCB

- DFT设计

- 华强pcb线路板打样

-

MES系统的最佳实践案例2024-10-27 4095

-

云计算平台的最佳实践2024-10-24 1471

-

Windows 10迁移的最佳实践2023-09-07 459

-

SAN设计和最佳实践指南2023-09-01 870

-

SAN管理最佳实践指南2023-08-29 631

-

虚幻引擎的纹理最佳实践2023-08-28 700

-

解析什么是DFT友好的功能ECO?2023-05-05 3191

-

什么是DFT友好的功能ECO呢?2023-03-06 3795

-

DevOps最佳实践2022-08-15 1731

-

变量声明最佳实践?2019-09-30 1636

-

Dockerfile的最佳实践2019-07-11 1540

-

机器学习实践指南——案例应用解析2018-04-13 2300

-

【资料不错】MOSFET开时米勒平台的形成过程的详细解析!2017-10-25 24731

-

C编程最佳实践.doc2012-08-17 2882

全部0条评论

快来发表一下你的评论吧 !