传统的移位寄存器与光耦合器隔离移位寄存器有什么不同

描述

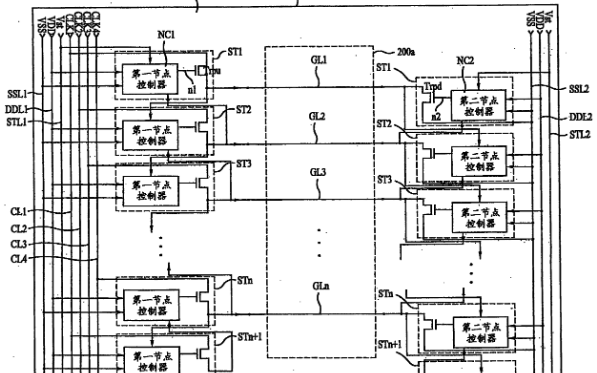

传统的移位寄存器,如74HC595,需要数据,时钟和选通逻辑信号。图1中的电路只需要两个逻辑信号来隔离和控制移位寄存器器件。对于每个发送的位,两个光耦合器中的一个接收短驱动脉冲:一个光耦合器用于高发送位,另一个用于低位,并且在脉冲发送所有位之后,电路最终并发1和0脉冲选通数据到输出寄存器。电路隔离侧的两个逻辑门封装将两个负脉冲信号解码回数据,时钟和选通脉冲。两个与非门形成RS锁存器,捕获串行输入(SERIN)的数据状态。另外两个与非门形成一个AND,将两个脉冲源组合成SRCK移位时钟。最后,NOR门(或另外四个NAND门)产生RCK选通脉冲。您可以根据需要级联移位寄存器设备。

除了观察光耦合器的最大数据速率并确保脉冲之间的关闭时间之外,您对信号没有时序限制。最后的锁存脉冲还会产生额外的上升SRCK边沿,可用于加载下一个序列的第一位。在这种情况下,最后关闭的光耦合器确定第一位的RS锁存状态。你也可以忽略额外的时钟;它对输出没有影响。通过限制LED电流和更新速率,可以使脉冲尽可能短,从而实现低功耗。例如,使用40微秒脉冲和1毫秒周期,平均驱动电流为80μA。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

- 相关推荐

- 热点推荐

- 寄存器

- PCB打样

- 华强PCB

- 华强pcb线路板打样

-

移位寄存器右移是怎么移位的2024-07-12 5110

-

移位寄存器的工作原理 移位寄存器左移和右移怎么算2024-01-18 14748

-

移位寄存器的设计与实现2022-09-06 6432

-

移位寄存器的原理2019-07-15 77546

-

移位寄存器实验报告_移位寄存器原理2017-12-22 29580

-

寄存器与移位寄存器2016-05-20 1296

-

移位寄存器及其应用实验2012-07-16 7398

-

移位寄存器,移位寄存器是什么意思2010-03-08 18267

-

线性移位寄存器2010-01-12 2275

-

可越位的移位寄存器2009-04-10 601

-

集成移位寄存器2009-03-20 1203

全部0条评论

快来发表一下你的评论吧 !