怎样编写自己的PCB设计检查器

描述

编写自己的PCB设计规则检查器

1.0简介

本文介绍了编写设计规则检查器(DRC)的系统方法用于PCB设计。在原理图工具中捕获PCB设计后,必须运行DRC以查找违反设计规则的行为。这必须在后端处理开始之前完成。通常,原理图工具的供应商提供DRC,大多数设计人员只是使用它。

但是,供应商工具是通用的,可能并不总是足够灵活,可以处理某些独特的要求。可以将要添加到DRC的新功能的请求发送给供应商,但这将花费金钱和时间,特别是如果必须多次执行此操作。幸运的是,大多数工具供应商都提供易于使用的机制,您可以编写自己的DRC以更好地满足您的独特需求。不幸的是,这个强大的工具还没有被广泛认可或利用。在本文中,我们提供了一些有关如何充分利用它的实用指南。

因为DRC必须遍历PCB设计的整个原理图,包括每个符号,每个引脚,每个网络,如有必要,可以生成每个属性,无限数量的有用“副产品”。正如第4.0节所解释的那样,它们可以很好地标记出微妙的设计规则违规。例如,一个副产品文件可能包含设计中的所有去耦电容。如果数字远小于或大于预期,这可能会引发可能的电源线dv/dt问题的红旗[1]。这些副产品文件可能非常需要,但它们是绝对不是由任何商用DRC生成的。

此DRC的另一个好处是可以轻松快速地更新它以适应新的设计功能,例如影响设计规则的新属性。此外,一旦在这个领域获得了足够的经验,那么许多其他可能性将出现。

例如,如果您可以编写自己的DRC,您当然可以编写自己的物料清单(BOM)生成工具,这又可以更好地处理某些独特的要求,例如在哪里获取组件不属于原理图数据库的“额外硬件”(插座,散热片或螺钉)。或者您可以编写自己的Verilog netlister,它足够灵活,适合您的设计环境,例如在哪里可以获取Verilog模型或某些独特组件的计时文件。事实上,当DRC遍历设计原理图时,它可以收集所有必要的信息,以输出用于模拟的Verilog网表和/或用于PCB制造的BOM。

这将很难讨论这些主题没有提供一些编程代码。为此,我们需要使用原理图捕获工具作为示例。在本文中,我们使用来自Mentor Graphics的ViewDraw,它是PADS-Designer产品系列的一部分。此外,我们使用ViewBase,它只是一个C例程库,可以调用它来访问ViewDraw数据库。使用ViewBase,您可以轻松地在C/C ++[2] [3]中为ViewDraw编写完整且有用的DRC。请注意,我们在此讨论的原则适用于任何其他PCB原理图工具。

2.0开始

2.0.1输入文件

除了原理图数据库之外,DRC还需要一些输入文件来告诉它如何处理某些情况,例如自动连接到电源平面的合法电源网名。例如,如果电源网称为POWER,则它会通过后端打包实用程序自动连接到电源平面,例如ViewDraw的 pcbfwd 。以下是这些输入文件的列表,这些文件应放在固定的全局位置,以便DRC可以在运行时自动查找/读取它们并在内部存储信息。

可选择创建名为legal_pwr_net_name的文件包含POWER信号的所有合法网络名称,例如VCC,V3_3P,VDD。请注意,字母大小写可能对某些PCB布局/布线工具很重要,并且通常VCC与Vcc或vcc不同。 VCC可以是5.0V电源,V3_3P可以是3.3V电源。

legal_pwr_net_name是可选的,因为后端打包实用程序的配置文件通常必须包含合法电源/地网名称列表。如果来自Cadence Design Systems的Allegro是放置/布局工具,则该文件名为allegro.cfg,用于 pcbfwd ,它必须具有以下条目:

接地VSS CGND GND GROUND

电源VCC VDD VEE V3_3P V2_5P + 5V + 12V

如果DRC可以直接读取allegro.cfg而不是legal_pwr_net_name,那将会更好(引入错误的可能性更小)。

通常,电源/接地引脚不会出现在元件符号上。相反,该符号具有一个属性(可以称为SIGNAL),该属性指定哪个引脚是电源还是接地,并指定该引脚应连接到的网络的名称:

SIGNAL = VCC:10

SIGNAL = GROUND:20

DRC可以读取此属性并确保网络名称是legal_pwr_net_name文件中的名称。如果没有,该电源引脚将不会连接到电源层,这是一个非常严重的错误。

某些符号必须带有电源/接地引脚,因为它们未连接到正常电源/接地层。例如,ECL器件的VCC引脚可以连接到VCC或GROUND;其VEE引脚可以连接到GROUND或-5.0V平面。此外,电源/接地引脚可以在进入电源/接地平面之前首先连接到滤波器。

此引脚和过滤器之间的网络可以有任何名称,DRC将无法检查此信息。 DRC可以将此报告为错误,用户必须将其筛选出来,或者仅为此设计将网名添加到legal_pwr_net_name文件中。这是可能需要legal_pwr_net_name等文件的一个原因。最后,legal_pwr_net_name将被DRC读入1)找到上拉电阻,2)检查设计中POWER网名的字母大小写,以及3)检测任何未使用的引脚直接连接到POWER。

可选择创建一个名为legal_gnd_net_name的文件,其中包含GROUND信号的所有合法网络名称,例如GROUND,VSS和F_GND。再次注意,字母大小写可能对某些PCB布局/路由工具很重要。此外,如果DRC可以直接读取上面提到的allegro.cfg文件而不是legal_gnd_net_name,那将更好。

legal_gnd_net_name与上面讨论的legal_pwr_net_name具有相同的目的。此外,它将被DRC读入1)找到下拉电阻,2)检查GROUND网络名称的字母大小写,以及3)检测直接连接到GROUND的任何未使用的引脚。

(可选)创建legal_lib_path_name文件,其中包含所有合法符号库路径和名称。这非常重要,因为常见和严重的错误是使用未经授权的库中的符号。在PCB设计阶段,通常会创建临时组件符号并将其放在本地符号库目录中以进行测试。最终版本将从此出来并放在公司或全局库目录中,它们可能与本地版本的重要方式不同。设计人员通常忘记用公司符号替换本地符号并引入设计错误。

legal_lib_path_name是可选的,因为对于大多数原理图工具,库信息包含在启动该工具所需的初始化文件中。对于ViewDraw,该文件名为viewdraw.ini,并在工具启动时自动创建(通过脚本)。库规范条目如下所示:

DIR [r]/corp_lib/pcb/symbol_libraries/viewdraw/fct(fct)

fct是众多ViewDraw中的一个子可以来自fct(快速CMOS技术)部件符号的库。 DRC可以而且应该直接读取此初始化文件(如果存在),因为设计人员可以动态添加新库。

创建一个名为legal_pullup_res的文件,其中包含合法的上拉电阻用于端接和未使用的输入引脚。通常,公司有资格并允许其设计人员使用的电阻列表。此外,电阻值也很重要。如果未使用的输入引脚被上拉,则该值应为5K或更高。

创建一个名为legal_pulldown_res的文件,其中包含用于端接和未使用输入引脚的合法下拉电阻。如果使用一个电阻来拉低未使用的输入引脚,则其值应该很小,以防止任何漏电流将引脚电压增加到触发阈值以上。

创建一个名为legal_decoup_cap的文件,其中包含合法的去耦电容。同样,公司可能要求其设计人员仅使用符合电源线dv/dt要求的某些合格零件。

创建一个名为legal_comp_attr的文件,其中包含组件符号应具有的所有必需属性,例如PART_NO,GEOM,REFDES,SIM_CLASS。它们可以由BOM生成工具,Verilog网表和其他工具使用。

创建一个名为legal_pin_attr的文件,其中包含组件符号应具有的所有必需的引脚属性,例如PIN_NAME,PINTYPE,PIN_NO 。

2.0.2设计目录结构

DRC运行的第二个条件是固定的单一设计目录结构,由所有PCB设计共享。没有它,DRC就不知道在哪里可以找到原理图数据库以及存储输出文件的位置。这种结构可能非常复杂,并且具有许多层级,以支持所有PCB设计活动,例如设计规则检查,BOM生成,Verilog仿真,静态时序分析,信号完整性分析,布局/布局,PAL/FPGA设计(综合)和模拟)和文件控制。但是对于DRC而言,如果使用ViewDraw,以下内容就足够了:

图1 - 目录结构

pcb_info目录应至少包含两个文件。第一个是design_def,另一个是design_type。 design_def应包含PCB部件(组件)编号和其他所需信息,不仅适用于DRC,还适用于所有其他工具。 design_type应包含设计类型信息,即PCB。如果此设计目录结构由其他类型的设计(例如ASIC或FPGA)共享,则design_type应指定它,以便设计自动化工具可以针对不同的设计类型采取适当的操作。如果pcb_info目录丢失或为空,则表示设计目录不是标准目录。在这种情况下,DRC应退出并给出错误消息。

schem目录包含原理图数据库,可由我们的DRC使用的ViewBase直接访问。 sch子目录包含描述工作表上的符号位置和其他信息的原理图文件。 wir子目录包含设计的网表和所有符号属性。 ViewBase例程可以直接访问它们。

drc目录应该存储DRC的输出文件。

3.0 A PCB DRC

3.0.1包装器程序

我们的DRC是用C语言和C例程的ViewBase库编写的。后者提供了对ViewDraw原理图数据库的轻松直接访问。它的每个例程访问一个数据项或遍历两个数据项之间的一个关系。但是DRC不应该直接运行:它应该“包装”在用Perl或UNIX shell语言编写的包装程序中。包装器程序执行以下操作:

检查图1中描述的PCB设计目录结构是否有效。

可选择运行后端打包程序,例如 pcbfwd 用于ViewDraw。该程序可以检查在DRC中难以检查的一些设计规则违规,例如网络名称允许的字符数和类型。它还可以将值(例如R4)分配给尚未分配值的符号参考指示符属性。

检查第2.0.1节中讨论的所需输入文件是否存在,并将它们提供给DRC。/li>

查找PCB设计名称并将其提供给DRC。

向DRC输入其输出文件的路径和名称。

设置所需的工具环境变量,例如用于ViewDraw和ViewBase的WDIR。

调用DRC程序。

根据请求打印帮助消息。

打印用户和运行时信息。

执行后期处理。这可以像检查DRC的输出文件到修订控制工具一样简单,也可以像主动处理DRC的输出文件一样复杂,例如从其他数据源添加更多信息或执行排序。 C可能不是排序数据或解析文件的最佳工具。例如,要使用第二个字段以数字方式对文件进行排序,使用UNIX排序命令要容易得多:

sort + 1n source_file> sorted_file

3.0.2 DRC开发:main()函数

让我们调用DRC程序drc.c,它可以有两个主要功能:drc_net()和drc_inst()。前者遍历所有网络,后者遍历所有实例(符号),寻找设计规则违规。这两个函数还可以生成副产品输出文件,这将在第1.0节和第4.0节中讨论。

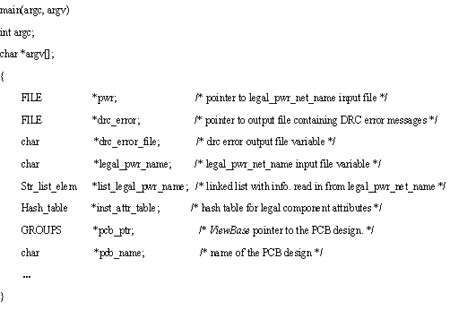

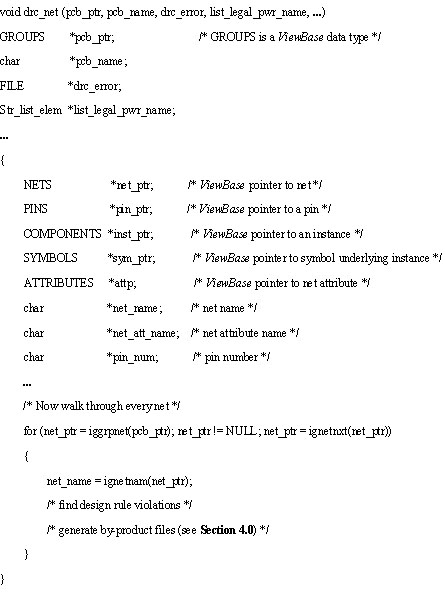

drc.c应该首先包括所有C,ViewBase和用户创建的头文件,例如stdio.h,viewbase.h和hash_table.h。现在设置drc.c以接收输入参数,声明变量和文件指针指向输入和输出文件,使ViewBase指向ViewDraw数据库,并创建链接列表和散列表以存储从输入文件读入的信息。 main()函数的一部分如下所示。

输入和输出文件名以及PCB设计名称在调用DRC时由DRC的包装程序(参见第3.0.1节)输入。数据结构Str_list_elem和Hash_table在drc.c包含的头文件中定义。 GROUPS是一个ViewBase数据类型。

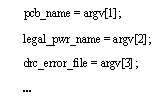

接下来,main()函数应该通过检查argc是否等于预期数量来确保传入正确的输入数。如果是,则为变量分配输入参数:

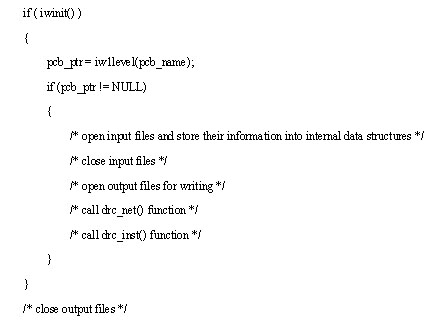

此时,main()函数可以初始化ViewBase数据结构并使ViewBase指针pcb_ptr指向PCB设计。如果设计存在且有效,则main()函数应该:

打开所有输入文件以进行读取,并将其信息存储到内部数据结构中,例如Str_list_elem和Hash_table。关闭输入文件。

打开所有输出文件进行写入。它们可以是设计规则错误/警告文件以及副产品文件。

调用drc_net()和drc_inst()函数来完成实际工作。

关闭所有输出文件。

main()中的C和ViewBase代码的大纲这是:

这里,iwinit()和iw1level()是ViewBase例程。前者初始化所有加载器例程,这是必需的。后者加载一层PCB设计(整个设计)。要仅加载一个工作表,请使用iw1sheet()例程(我们的DRC中未使用该例程)。请注意,必须将正确的设计指针,文件指针,链接列表,变量名等传递给drc_net()和drc_inst()函数:

drc_inst(pcb_ptr,pcb_name,drc_error,list_legal_pwr_name,.. 。);

如果您的设计是分层的并且使用异构组件符号,那么请确保DRC可以正确处理它们。

3.0.3 DRC开发: drc_net()函数

drc_net()遍历PCB设计中的所有网络,查找违反设计规则和/或生成副产品输出文件。代码大纲如下:

这里,iggrpnet()和ignetnxt()是ViewBase例程,用于抓取PCB设计中的每个网络。 ignetnam()也是一个用于查找网络名称的ViewBase例程。 NETS,PINS,COMPONENTS,SYMBOLS和ATTRIBUTES是ViewBase数据类型.drc_net()可以查找以下设计规则违规:

非法网络名称。如果ViewDraw自动分配了网络名称,其格式为$#...#N#...#,其中第一个#...#是工作表编号,第二个#...#是网络编号。 PCB设计人员分配的网络名称必须以字母开头,后跟30个或更少字符。

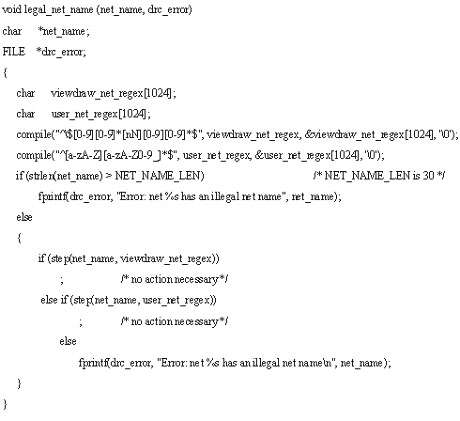

drc_net()应调用函数legal_net_name()来执行此任务。在UNIX中,regexp.h头文件大大简化了C中的正则表达式匹配/检查,该文件必须包含在DRC程序中。 drc_net()应该将网名变量和设计规则违规文件指针传递给legal_net_name(),它看起来像:

后端打包工具 pcbfwd 还可以检查非法网名,但其功能仅限于简单的正则表达式。上面给出的代码可以处理任何正则表达式。此外,在运行pcbfwd之前或之后是否查找非法网名是一个权衡问题。对于简单的网络名称,请使用pcbfwd。

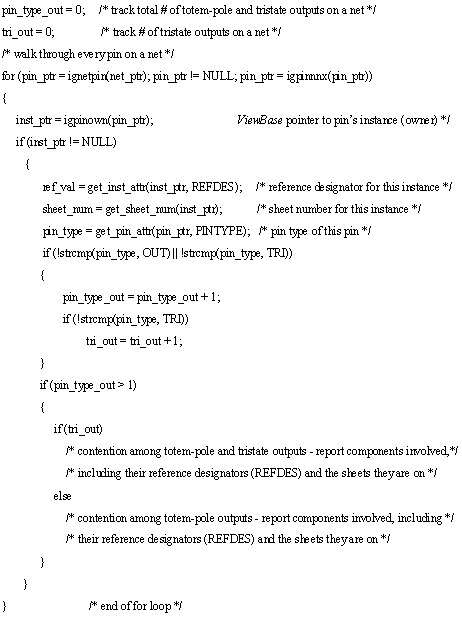

网络上的总线争用,这是一个严重的错误。有2种。一个是图腾柱输出之间的争用,另一个是图腾柱和三态输出之间的争论。代码大纲如下:

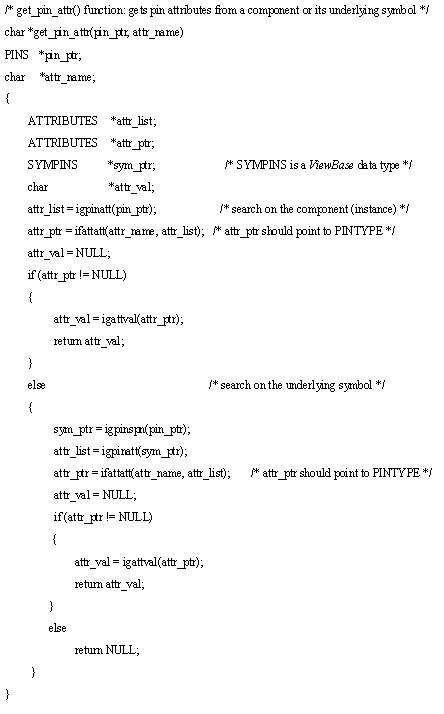

这里,ignetpin()和igpinnnx()是ViewBase例程,它们抓取网络上的每个引脚。 igpinown()例程返回指针的实例(所有者)的指针。函数get_inst_attr(),get_pin_attr()和get_sheet_num()分别返回所请求的实例属性(引用指示符REFDES),引脚属性(PINTYPE)和引脚实例所在的工作表编号。 get_pin_attr()函数的大纲如下:

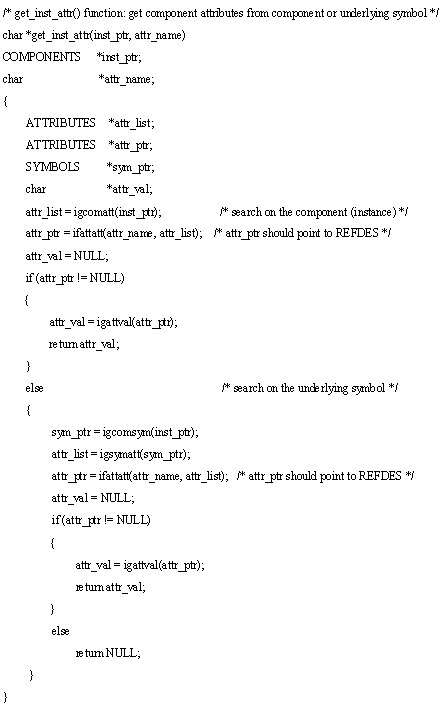

get_inst_attr()函数的大纲如下:

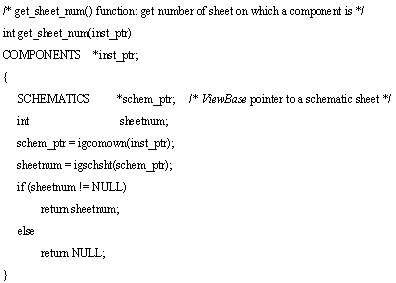

get_sheet_num()函数的大纲如下所示:

POWER和GROUND网络的非法名称。它们与存储在内部数据结构中的信息(如链表)进行比较。

报告有负载但没有驱动程序的网络,反之亦然。这是通过跟踪网络上每个引脚的引脚类型来完成的。应该有1个输出引脚或多个三态输出引脚和至少1个输入引脚。此外,请提供此网络上所有组件的参考标志和符号以及所涉及的引脚。

报告所有未接通上拉电阻或其上拉电阻未连接的集电极开路输出POWER。

如果网络的负载超过正常负载,则应打印警告,为了获得良好的信号完整性,该负载应小于8.

3.0.4 DRC开发:drc_inst( )函数

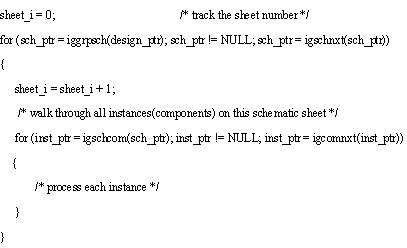

drc_inst()函数类似于drc_net(),除了前者遍历每个原理图工作表及PCB设计中的所有实例以查找违反设计规则或通过以下方式生成:产品输出文件。它的代码大纲是:

我们之前对drc_net()函数的讨论提供了充足的C和ViewBase代码示例,这里不再重复。以下是drc_inst()可以检查的设计规则违规的部分列表:

非法或缺少符号库别名。 PCB设计中的所有符号必须来自公司符号库。使用来自错误库的符号是一种非常常见的错误来源,尤其是对于仅依靠符号来处理设计的后端处理工具。

缺少符号和/或引脚属性,例如指定组件几何的属性和引脚的类型(in,out,bi,tri)。

符号和/或引脚属性的非法值。例如,引脚类型的值可以是IN,但不能是INPUT。这会影响后端打包工具(如 pcbfwd,)如何向放置/布局工具提供信息,例如Allegro。

符号上参考指示符的值,尤其是对于系列组件,例如电阻器,电容器和电感器。大多数信号完整性工具要求这些值以字母R,C和L开头,以便可以将它们分析为系列元素而不是分立元件。此外,drc_inst()可以根据description属性检查它们的值,以确保两者匹配。

非法去耦电容。这可能导致POWER线路dv/dt问题。

非法的上拉和下拉电阻。

符号的POWER或GROUND引脚未连接到POWER或GROUND平面。

未使用的输入引脚没有通过电阻上拉或下拉,或者此电阻没有直接连接到POWER或GROUND网络。

如果上拉或下拉超过1个未使用的输入引脚,则发出警告

在直接连接到POWER或GROUND网络的非专用POWER和GROUND引脚上发出警告。

如果使用Tab键,请检查它是否引用了正确的替代方案组件,例如它们的部件号是否有效以及它们的几何形状是否与默认组件的几何形状匹配。

3.0.5 DRC不应该做什么

虽然我们的DRC可以做很多事情,有些东西可以通过其他方式更好更容易地检查。一个伟大而必要的帮手是后端封装实用程序,它为放置/布局工具打包PCB设计。对于ViewDraw,它是 pcbfwd,,可以设置它来检查许多设计规则违规和设计错误。

DRC和 pcbfwd之间存在重叠 pcbfwd 运行之前运行。理想情况下, pcbfwd 应仅运行以打包设计,因此DRC可以检查得越多越好。但是你应该平衡开发超级强大的DRC与免费提供的 pcbfwd的现有功能的努力。本节简要讨论了这些问题。

pcbfwd 由其配置文件控制,如果Allegro是放置/布局工具,则称为allegro.cfg。其BeginChkRules - EndChkRules部分可用于检查许多错误,例如同一符号上的重复属性,非法网络和网络属性名称,错误的异构包,异构符号上的冲突属性以及缺少的属性。例如,要捕获异构符号上的冲突属性,请将以下行放入allegro.cfg:

CHKBRD _HETERO_ATT ERR 0

有些事情既不是DRC也不是 pcbfwd 可以检查,例如PCB设计中的预期冗余。假设一个组件包含4个相同的部件,2个用于设计,那么它们可以打包到同一个组件或2个组件中以实现冗余。如果需要一个组件,则两个组件的符号必须具有相同的参考标号,例如U4。如果需要2个组件,则符号必须具有不同的参考标志,例如U4和U5,必须由设计人员认真添加。没有已知的简单方法来捕捉此类错误,而精心设计师可能是唯一的保证。

另一个例子是虽然DRC和/或 pcbfwd 可以检查是否symbol具有所需的几何属性GEOM,它们无法检查其值是否与原理图符号匹配。一个不匹配可能在ViewDraw符号上指定的引脚数与Allegro占用空间上的引脚数之间。

Allegro的 dev_check 实用程序可以捕获此特定错误。首先,在ViewDraw原理图上运行pcbfwd以创建Allegro设备文件,这些文件与Allegro脚印文件一起输入 dev_check 。假设引脚68,69和70位于Allegro占位面积上但不在ViewDraw符号上,则 dev_check 可以捕获此信息。这些引脚可能是无连接或安装孔,甚至是错误地遗漏在ViewDraw符号之外的POWER/GROUND引脚。必须为NC属性分配无连接和/或安装孔引脚,并将POWER/GROUND引脚分配给SIGNAL属性。以这种方式修改符号并重新运行 pcbfwd 和 dev_check 。

最后,DRC输出的质量取决于原理图的质量。例如,如果错误地将引脚类型指定为输入引脚的OUT,则DRC将生成错误的错误消息。组件符号质量应该仔细和系统地控制,因为它会影响所有其他工具。

4.0超越DRC

除了检查设计规则违规,DRC还可以生成有用的副产品输出文件,如前所述。输入开关可以告诉DRC是否为每次运行生成它们。虽然这些文件不包含DRC错误或警告消息,但它们可以标记潜在的设计问题。例如,一个文件可以包含所有网络的列表以及每个网络上的负载数量。如果该数量超过合理值,则可能导致信号完整性问题。 PCB设计人员可以快速浏览此文件并查找此类问题。这些副产品文件的数量可以是所需数量。部分列表如下。

按网名排序的所有网络列表以及每个网络所在的工作表。附加信息可能包括该网络连接的符号的引脚号和类型(及其参考标号)。该文件由drc_net()函数创建。它可用于查找网络所在的工作表。

所有网络的列表以及每个网络的负载数量。这是由drc_net()函数生成的。为了获得良好的信号完整性,网络应该不超过8个负载。

跨越工作表边界的网络列表。这有助于设计人员在实验室中调试设计。

具有网络属性及其属性的网络列表。 Designer可以检查这些网络是否具有正确的属性。此文件由drc_net()函数生成,代码大纲为:

此处,ignetatt()和igattnxt()是ViewBase例程以获取网络上的每个属性。 igattnam()获取属性名称。 net_att是指向输出文件的文件指针。

所有未使用的引脚的列表,应该上拉或下拉。报告上拉和下拉电阻。该文件由drc_inst()函数生成。

所有去耦电容及其值的列表。附加信息可能包括它们所在的原理图表。设计人员应快速检查此文件,以确保PCB上有足够的去耦电容。该文件由drc_inst()函数生成。

所有分立元件及其值的列表,例如上拉/下拉电阻,传输线终端电阻/电容。附加信息可能包含它们所在的原理图表。设计师可以快速检查数字是否合理。该文件由drc_inst()函数生成。

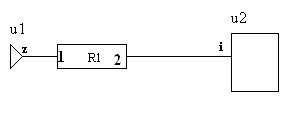

此列表的另一个重要用途是PCB设计的信号完整性和时序分析[4]。该领域的大多数工具都可以自动处理所谓的系列元素,通过将它们的效果组合到传输线分析结果中,但将它们从输出文件中取出。一个这样的元件是图2中的R1,它是串联终端电阻器。当信号完整性工具报告净延迟时,它将从u1.z到u2.i,包含R1的效果,而不是从u1.z到R1.1,并从R1.2继续到u2.i.这是正确的时序分析。

图2 - 串联终端电阻

但是,为了一个信号完整性工具自动识别一系列元素,必须满足一些条件。例如,电阻的参考标志必须以字母R后跟数字和字母C的电容开始。另一个条件是每个系列元素符号必须具有值为DISCRETE的TYPE属性。没有这些条件,这些元素就无法正确处理。

一个常见问题是模板设计被许多其他PCB复制。为了避免可能的参考标志冲突,模板设计中的电阻和电容通常称为XR1和XC1。必须在信号完整性工具的数据库中将它们更改为R10001和C10001(数字应大于原始PCB设计中使用的任何可能的参考标志符号)。通过使用我们的DRC生成的离散组件列表,可以找到XR和XC参考标志。

5.0结论

显然,有编写自己的PCB设计规则检查器的许多优点和必要条件。尽管这项工作并非微不足道,但它也不是火箭科学,也可以由对现有编程或脚本语言有深入了解的任何人完成。好处是无限的,可以大大超过努力。

6.0参考文献

1。 Luke L. Chang,“VAX 9000存储器配电系统的瞬态分析”,数字电源系统,1990年秋/冬

2。 Brian W. Kernighan& Dennis M. Ritchie,“C编程语言”,第2版,Prentice Hall,1988年

3。 Bjarne Stroustrup,“The C ++ Programming Language”,3rd Edition,Addison-Wesley,1997

4。 Luke L. Chang,“高速电路板的静态时序分析”,IEEE Spectrum,1997年3月

Luke L. Chang是英特尔存储元件部门的高级验证负责人(哈德逊,马萨诸塞州)。在此之前,他曾在多家高科技公司担任过工程和管理职位,涉及硬件设计/验证和电子设计自动化(EDA)领域。

- 相关推荐

- 热点推荐

- PCB设计

- 华强pcb线路板打样

-

常规的PCB设计检查表2023-02-22 781

-

怎样去编写属于自己的PCB设计规则检查器?2021-04-26 1923

-

PCB设计检查中的视觉检查2020-11-13 2613

-

PCB设计之后需要进行哪些检查?2020-09-08 2587

-

如何进行PCB规则检查器DRC的设计2020-03-27 4514

-

PCB设计时应该注意检查什么2019-08-20 4506

-

PCB设计的六个检查阶段2019-05-15 4789

-

编写PCB设计规则检查器系统方法2018-09-10 1629

-

PCB设计规则检查器编写技巧2013-10-08 2028

-

编写属于自己的PCB设计规则检查器2009-12-27 1054

-

编写PCB设计规则检查器技巧2009-11-17 1218

全部0条评论

快来发表一下你的评论吧 !