共模扼流圈综述

描述

电源滤波器的设计通常可从共模和差模两方面来考虑。共模滤波器最重要的部分就是共模扼流圈,与差模扼流圈相比,共模扼流圈的一个显著优点在于它的电感值极高,而且体积又小,设计共模扼流圈时要考虑的一个重要问题是它的漏感,也就是差模电感。通常,计算漏感的办法是假定它为共模电感的1%,实际上漏感为共模电感的 0.5% ~ 4%之间。在设计最优性能的扼流圈时,这个误差的影响可能是不容忽视的。

漏感的重要性

漏感是如何形成的呢?紧密绕制,且绕满一周的环形线圈,即使没有磁芯,其所有磁通都集中在线圈“芯”内。但是,如果环形线圈没有绕满一周,或者绕制不紧密,那么磁通就会从芯中泄漏出来。这种效应与线匝间的相对距离和螺旋管芯体的磁导率成正比。共模扼流圈有两个绕组,这两个绕组被设计成使它们所流过的电流沿线圈芯传导时方向相反,从而使磁场为0。如果为了安全起见,芯体上的线圈不是双线绕制,这样两个绕组之间就有相当大的间隙,自然就引起磁通“泄漏”,这即是说,磁场在所关心的各个点上并非真正为0。共模扼流圈的漏感是差模电感。事实上,与差模有关的磁通必须在某点上离开芯体,换句话说,磁通在芯体外部形成闭合回路,而不仅仅只局限在环形芯体内。

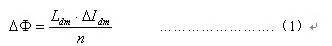

如果芯体具有差模电感,那么,差模电流就会使芯体内的磁通发生偏离零点,如果偏离太大,芯体便会发生磁饱和现象,使共模电感基本与无磁芯的电感一样。结果,共模辐射的强度就如同电路中没有扼流圈一样。差模电流在共模环形线圈中引起的磁通偏离可由下式得出:

式中,是芯体中的磁通变化量,Ldm是测得的差模电感,是差模峰值电流,n为共模线圈的匝数。

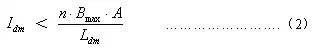

由于可以通过控制B总,使之小于B饱和,从而防止芯体发生磁饱和现象,有以下法则:

式中,是差模峰值电流,Bmax是磁通量的最大偏离,n是线圈的匝数,A是环形线圈的横截面积。Ldm是线圈的差模电感。共模扼流圈的差模电感可以按如下方法测得:将其一引腿两端短接,然后测量另外两腿间的电感,其示值即为共模扼流圈的差模电感。

共模扼流圈综述

滤波器设计时,假定共模与差模这两部分是彼此独立的。然而,这两部分并非真正独立,因为共模扼流圈可以提供相当大的差模电感。这部分差模电感可由分立的差模电感来模拟。

为了利用差模电感,在滤波器的设计过程中,共模与差模不应同时进行,而应该按照一定的顺序来做。首先,应该测量共模噪声并将其滤除掉。采用差模抑制网络(Differential Mode Rejection NETWORK),可以将差模成分消除,因此就可以直接测量共模噪声了。如果设计的共模滤波器要同时使差模噪声不超过允许范围,那么就应测量共模与差模的混合噪声。因为已知共模成分在噪声容限以下,因此超标的仅是差模成分,可用共模滤波器的差模漏感来衰减。对于低功率电源系统,共模扼流圈的差模电感足以解决差模辐射问题,因为差模辐射的源阻抗较小,因此只有极少量的电感是有效的。

尽管少量的差模电感非常有用,但太大的差模电感可以使扼流圈发生磁饱和。可根据公式(2)作简单计算来避免磁饱和现象的发生。

-

什么是共模扼流圈,怎样绕制?2024-02-05 3508

-

共模扼流圈的工作原理 共模扼流圈的优缺点 共模扼流圈的应用2023-12-21 3272

-

CST如何导出和使用共模扼流圈的S参数呢?2023-06-08 5738

-

串模扼流圈、共模扼流圈选择方法2023-06-06 2138

-

共模电感(扼流圈)选型2022-02-11 2132

-

开关电源串模扼流圈、共模扼流圈选择方法2022-01-10 1295

-

信号线用共模扼流圈怎么使用?2021-04-09 1902

-

开关电源中串模扼流圈和共模扼流圈选择技巧2020-10-06 5943

-

共模扼流圈的磁芯用什么材料_共模扼流圈结构2017-10-30 7827

-

共模扼流圈简介2012-08-09 3015

全部0条评论

快来发表一下你的评论吧 !