高速pcb设计的信号完整性问题

描述

在髙速PCB电路原理全过程中,常常会碰到信号完整性难题,造成数据信号传送品质不佳乃至错误。那麼怎样区别髙速数据信号和一般数据信号呢?许多人感觉数据信号頻率高的就是说髙速数据信号,其实要不然。人们了解一切数据信号能够由正弦数据信号的N次脉冲电流来表达,而数据信号的最大頻率或是数据信号网络带宽算是考量数据信号是不是髙速数据信号的规范。

图一

图二

图三

图四

图五

1、防护

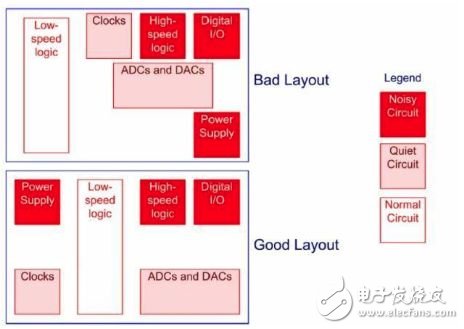

一块儿PCB板上的电子器件有各式各样的边值(edge rates)和各种各样噪音差别。对改进SI最立即的方法就是说根据元器件的边值和敏感度,根据PCB板上电子器件的物理学防护来保持。

图1是1个案例。在事例中,供电系统开关电源、大数字I/O端口号和髙速逻辑性这种对钟表和数据转换电源电路的高风险电源电路将被非常考虑到。

第一位合理布局中置放钟表和统计数据转化器在邻近于噪音元器件的周边。噪音将会藕合到比较敏感电源电路及减少她们的特性。下一个合理布局干了合理的电源电路防护将有益于控制系统设计的信号完整性。

2、特性阻抗、反射面及终端设备配对

特性阻抗操纵和终端设备配对是髙速电路原理中的基础难题。一般每一电路原理中频射电源电路均被觉得是最关键的一部分,殊不知某些比频射更高频的数字电路设计反倒忽略了特性阻抗和终端设备配对。

因为特性阻抗失配造成的几类对数字电路致命性的危害,参照图为:

a.模拟信号将会在接受机器设备键入端和发射点机器设备的輸出端间导致反射面。反射面数据信号被弹回而且顺着线的两边散播直至最终被彻底消化吸收。

b.反射面数据信号导致数据信号在根据传输线的响铃效用,响铃将危害工作电压和数据信号延迟和数据信号的彻底恶变。

c.失配数据信号相对路径将会造成数据信号对自然环境的辐射源。

由特性阻抗不配对造成的难题能够根据终端设备电阻器降至最少。终端设备电阻器一般是在挨近接收端的电源线上置放一到2个吸收合并元器件,简易的作法就是说接双小的电阻器。

终端设备电阻器限定了数据信号上升时间及消化吸收了一部分反射面的动能。特别注意的是运用阻抗匹配并不可以彻底清除毁灭性要素。殊不知用心的采用适合的元器件,终端设备特性阻抗能够很合理的操纵数据信号的一致性。

并并不一定的电源线都必须特性阻抗操纵,在某些诸如此类紧凑 PCI 规格型号规定中的特点特性阻抗和终端设备特性阻抗特点。针对其他沒有特性阻抗操纵标准规定的别的规范及其设计师并沒有刻意关心的。

最后的规范将会变化很大从1个运用到另外运用中。因而必须考虑到电源线的长短(有关与延迟时间 Td)及其数据信号上升时间(Tr)。通用性的对特性阻抗操纵标准是 Td(延迟时间)应超过 Tr 的 1/6。

3、内电层及内电层切分

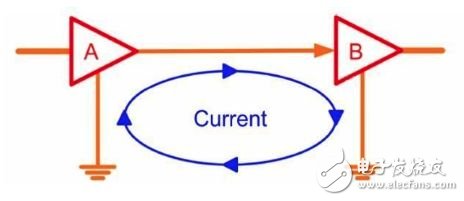

在电流量环路布置时会被数字电路设计者忽略的要素,包含对单端数据信号在2个门电路间传输的考虑到(图2)。从门 A 流入门 B 的电流量环路,随后再从地平面图回到到门 A。

门电路电流量环路中存有2个潜在性的难题:

a、 A 和 B 二点间地平面图必须被联接根据1个低特性阻抗的通道

假如地平面图间连接了很大的特性阻抗,在地平面图脚位间将会出現工作电压倒风。这就必将会造成全部元器件的数据信号幅度值的失帧而且累加键入噪音。

b、 电流量流回环的总面积应尽量的小

环路如同无线天线。一般說話,这种更大环路总面积将会扩大了环路辐射源和传输的机遇。每1个电源电路设计师都期待流回电流量都可以立即顺着电源线,那样就最少的环路总面积。

用大规模接地装置能够一起处理左右2个难题。大规模接地装置能够出示全部接地址间小的特性阻抗,一起容许回到电流量尽可能立即顺着电源线回到。

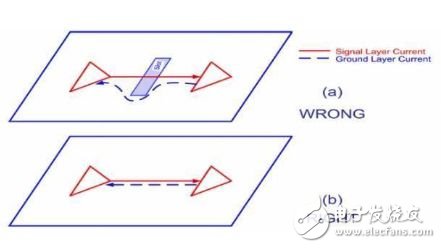

在 PCB 布置中1个普遍的不正确是在虚梁打过孔和打槽。图3显示信息了当这条电源线在1个开了槽的不一样层上的电流量流入。控制回路电流量将强迫绕开打槽,这就必定会造成1个大的环流控制回路。

一般来讲,在地开关电源平面图上是不能打槽的。殊不知,在某些难以避免要打槽的场所,PCB 设计师务必最先明确在打槽的地区沒有数据信号控制回路历经。

一样的标准也适用混和数据信号电源电路 PCB 板中除非是采用好几个地质构造。尤其性能ADC电源电路中能够运用分离出来模拟信号、模拟信号及时钟电路的地质构造合理的降低数据信号间的干挠。

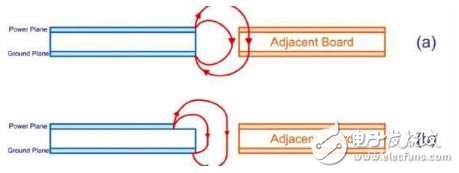

必须再度注重的,在某些难以避免要打槽的场所,PCB 设计师务必最先明确在打槽的地区沒有数据信号控制回路历经。在含有1个镜像系统差别的电源层中也应留意虚梁地区的总面积(图4)。

在主控板的边沿存有开关电源平面图层对地平面图层的辐射源效用。从边缘泄露的电磁感应动能将毁坏邻近的主控板。见图为4a。适度的降低开关电源平面图层的总面积(图4 b),以致于地平面图层在必须的地区内相叠。这将降低电磁感应泄露对相邻主控板的危害。

4、串扰

在PCB布置中,串扰难题是另外最该关心的难题。图为中显示信息出在1个PCB中邻近的三对并列电源线间的串扰地区及关系的电磁感应区。当电源线间的间距太钟头,电源线间的电磁感应区将相互关系,可能会导致数据信号的转变就是说串扰。

串扰能够根据提升电源线间隔处理。殊不知,PCB 设计师一般依赖于日渐缩紧的走线室内空间和狭小的电源线间隔;因为在布置中沒有大量的挑选,进而难以避免的在布置中导入某些串扰难题。显而易见,PCB 设计师必须必须的管理方法串扰难题的工作能力。

一般业内认同的标准是 3W 标准,即邻近电源线间隔最少应是电源线总宽的 3 倍。可是,具体工程项目运用中可接纳的电源线间隔取决于具体的运用、办公环境及布置沉余等要素。

电源线间隔从这种状况转化成另这种及其每一次的测算。因而,当串扰难题难以避免时,就应当对串扰定量化。这能够根据计算机仿真技术性表达。运用仿真器, 设计师能够决策信号完整性实际效果和评定系统软件的串扰危害实际效果。

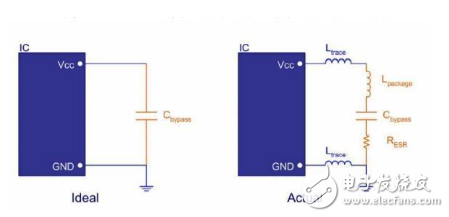

5、开关电源去耦

开关电源去耦是数字电路设计中国际惯例,退耦有利于降低电源插头上噪音难题。迭加进开关电源上的高频率噪音将会对邻近的大数字机器设备都是产生难题。典型性的噪音于地弹、数据信号辐射源或是大数字元器件本身。

非常简单的处理开关电源噪音方法是运用电容器对土里的高频率噪音去耦。理想化的退耦电容器为高频率噪音出示了这条对地的低阻通道,进而消除了开关电源噪音。

根据具体运用挑选去耦电容器,大部分的设计师会挑选表贴电容器在尽量挨近开关电源脚位,而容值应大到充足为可预料的开关电源噪音出示这条低阻对地通道。

选用退耦电容器一般会碰到的难题是不可以将退耦电容器简易的当做电容器。有下列几类状况:

a、 电容器的封裝会造成内寄生电感器;

b、 电容器会产生某些等效电阻;

c、 在开关电源脚位和退耦电容器间的输电线会产生某些等效电感器;

d、 在地脚位和地平面图间的输电线会产生某些等效电感器;

从而而引起的效用:

a、 电容器将会对特殊的頻率引起共振效应和由其造成的互联网特性阻抗对邻近频率段的数据信号导致更大的危害;

b、 等效电阻(ESR)还将危害对髙速噪音退耦所产生的低阻通道;

下列小结了从而对1个大数字设计师造成的效用:

a、 从元器件上 Vcc 和 GND 脚位找出的导线必须被作为小的电感器。因而提议在布置中尽量使 Vcc 和 GND 的导线短而粗。

b、 挑选低 ESR 效用的电容器,这有利于提升对开关电源的退耦;

c、 挑选小封裝电容件将会降低封裝电感器。更换更小封裝的元器件将造成溫度特点的转变。

因而在挑选1个小封裝电容器后,必须调节布置中元器件的合理布局。在布置中,用 Y5V 型号规格的电容器替换成 X7R 型号规格的电容件,可确保更小的封裝和更低的等效电感器,但一起也会为确保高的溫度特点花销大量的元器件成本费。

在布置中还应考虑到用大空间电容器对高频噪音的退耦。选用分离出来的电解电容和贴片电解电容能够非常好的提升元器件的性价比高

-

高速PCB信号和电源完整性问题的建模方法研究2024-09-21 648

-

高速PCB的信号和电源完整性问题研究2024-09-19 606

-

高速PCB设计,信号完整性问题你一定要清楚!2024-04-07 1808

-

分析高速PCB设计信号完整性问题形成原因及方法解决2024-01-11 2527

-

PCB设计中的信号完整性问题2023-11-08 1963

-

高速pcb的信号完整性问题主要有哪些?2023-04-11 1073

-

高速电路信号完整性分析与设计—PCB设计12022-02-10 1296

-

高速PCB设计信号完整性问题形成原因及方法解决资料下载2021-03-27 1242

-

信号完整性问题与PCB设计2021-03-23 1139

-

高速PCB设计信号完整性问题形成原因是什么?2021-03-17 1786

-

如何克服高速PCB设计中信号完整性问题?2020-09-17 3732

-

高速PCB设计的信号完整性问题分析2019-06-18 1260

-

基于信号完整性分析的高速PCB设计2015-01-07 2771

-

高速PCB设计的信号完整性问题2012-10-17 3304

全部0条评论

快来发表一下你的评论吧 !