内存架构怎么影响存储器系统的性能

描述

自20世纪90年代中期以来,内存技术大多根据其运行速度来命名。 PC100 SDRAM设备将以100MHz数据速率运行,PC133以133MHz数据速率运行,依此类推。虽然这种品牌推广惯例的变化随着时间的推移而发生变化,但大多数都让潜在买家了解存储设备的运行速度。

简单地说,大多数存储器技术,实际上是当今所有的主流存储器技术,已经为自己打上了峰值数据速率,这一直是并将继续成为计算时的最重要因素之一。记忆系统的性能。然而,在真实系统中运行的存储器设备在100%的时间内不以其峰值数据速率运行。

从写入切换到读取,在特定时间访问某些地址以及刷新数据都需要在数据总线上保持一定的不活动状态,从而无法充分利用内存通道。另外,宽并行总线和DRAM核心预取都经常导致不必要的大数据访问。

内存控制器在给定时间内可以访问的可用数据量称为有效数据速率,并且高度依赖于系统的特定应用程序。有效数据速率随时间变化,通常远低于峰值数据速率。在某些系统中,有效数据速率可降至峰值数据速率的10%以下。

通常,这些系统可以从内存技术的变化中受益,从而产生更高的有效数据速率。在CPU的产品领域也存在类似的现象,近年来AMD和Transmeta等公司表明,在测量基于CPU的系统的性能时,时钟频率并不是唯一重要的因素。

内存技术也已经成熟到高峰和有效数据速率可能与之前不匹配的程度。虽然峰值数据速率仍然是存储器技术的最重要参数之一,但是其他架构参数可以极大地影响存储器系统的性能。

影响有效数据速率的参数

有几类参数影响有效数据速率,其中一类会导致不活动时间段到数据总线上。在这个类中的参数中,总线周转,行周期时间,CAS延迟和RAS到CAS延迟(tRCD)导致许多系统架构师的大多数延迟问题。

总线周转本身会在数据通道上造成很长时间的不活动。以GDDR3系统为例,该系统不断将数据写入存储设备的打开页面。在此期间,存储系统的有效数据速率与其峰值数据速率相匹配。

但是,现在假设在100个时钟周期内,存储器控制器从读取切换到写入。由于此开关的惩罚是六个周期,因此有效数据速率降至峰值数据速率的94%。如果在这100个周期内,存储器控制器将总线从写入切换回读取,则会丢失更多周期。

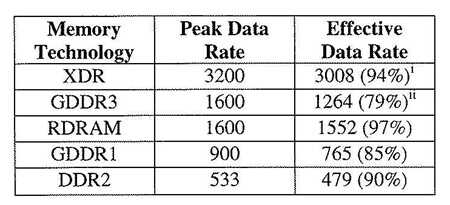

这种内存技术在从写入切换到读取时需要15个空闲周期,进一步将有效数据速率降低到峰值数据速率的79%。表1显示了几种高性能存储器技术的相同计算结果。

表1 - 两个总线转向的有效和峰值数据速率-counds每100个周期

显然,所有的内存技术都不是平等的。需要许多总线周转的系统设计人员可以从选择XDR,RDRAM或DDR2等更高效的技术中受益。另一方面,如果系统可以将事务分组为非常长的写入和读取序列,则总线转向对有效带宽的影响最小。但是,其他延迟增加现象(如银行冲突)可能会通过降低有效带宽对其性能产生负面影响。

DRAM技术都要求银行的页面或行在访问之前打开。一旦打开,在经过称为行周期时间(tRC)的最小时间段之前,不能打开同一存储体中的不同页面。对开放银行的不同页面的存储器访问被称为页面未命中,并且可能导致与tRC间隔的任何未满足部分相关联的延迟惩罚。

对于尚未开放足够周期以满足tRC间隔的银行的页面未命中被称为银行冲突。虽然tRC确定了银行冲突延迟的大小,但是在给定DRAM中可用的银行将直接影响银行冲突发生的频率。

大多数存储器技术有四个或八个存储体,并且在几十个周期内具有tRC值。在随机工作负载下,具有八个存储区核心的存储库冲突将比具有四个存储区核心的存储体冲突更少。虽然tRC和银行计数之间的相互作用很复杂,但它们的累积影响可以通过多种方式量化。

内存读取事务

考虑三种简单的内存读取事务。在第一种情况下,内存控制器发出每个事务,以便它与先前事务产生存储冲突。控制器必须在打开页面和打开后续页面之间等待一段时间tRC,从而增加与循环页面相关的最大延迟时间。在这种情况下,有效数据速率很大程度上与I/O无关,主要受DRAM核心电路的限制。在当今最高端的内存技术中,最大银行冲突率将有效带宽降低到峰值的20%到30%之间。

在第二种情况下,每个事务都以一个随机生成的地址为目标。在这里,遇到银行冲突的可能性取决于许多因素,包括tRC与存储器核心中存储体数量的相互作用。 tRC值越小,开放页面越早循环,导致银行冲突处罚越低。此外,存储器技术具有的存储体越多,存储体随机地址访问冲突的可能性就越低。

在第三种情况下,每个事务都是页面命中,在打开的页面中寻址各种列地址。控制器不需要访问封闭页面,允许100%的总线利用率,从而实现有效数据速率等于峰值数据速率的理想情况。

虽然第一和第三种情况涉及相当简单的计算,但随机情况受到DRAM或存储器接口中未特别包含的其他功能的影响。内存控制器仲裁和排队可以大大提高银行冲突率,因为可以发出更多可能的非冲突事务而不是那些导致银行冲突的事务。

但是,添加内存队列深度并不一定会增加两种不同内存技术之间的相对有效数据速率。例如,即使增加了内存控制器队列深度,XDR的有效数据速率也比GDDR3高20%。这种差异的存在主要是由于XDR的银行数量较多且tRC值较低。通常,较短的tRC间隔,较高的存储体计数和较大的控制器队列会导致较高的有效带宽。

许多限制效率的现象实际上是与行访问粒度相关的问题。 tRC约束基本上要求内存控制器从新打开的行访问一定数量的数据,以确保数据管道保持满员。实质上,为了保持数据总线不间断运行,打开一行后必须读取最少量的数据,即使不需要额外的数据。

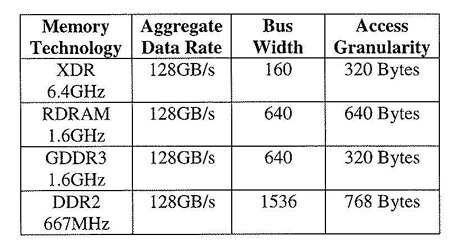

降低内存系统有效带宽的另一类主要特性属于列访问粒度类别,它决定了每个单独的读写操作必须传输多少数据。相反,行访问粒度决定了每行激活需要多少单独的读写操作(通常称为每个RAS的CAS操作)。

列访问粒度也可能对有效数据速率产生很大的影响,但影响较小。由于它规定了单次读取或写入中传输的最小数据量,因此列访问粒度对通常一次只需要少量数据的系统造成问题。例如,一个16字节访问粒度的系统,每两行需要8个字节,必须读取总共32个字节才能访问这两个位置。

由于只需要32个字节中的16个,系统经历了有效数据速率降低,相当于其峰值数据速率的50%。两个体系结构参数决定了内存系统的访问粒度:总线宽度和突发长度。

总线宽度是指连接在内存控制器和内存设备之间的数据跟踪总数。它设置了最小访问粒度,因为每个数据跟踪必须为给定的内存事务携带至少一位数据。反过来,突发长度指定每个通道必须为给定事务携带的位数。每个事务每个数据跟踪发送一位数据的存储器技术据说具有一个突发长度。总列访问粒度很简单:

列访问粒度=总线宽度x突发长度

许多系统架构师仅通过添加来增加内存系统的可用带宽更多的DRAM设备和增加内存总线的宽度。毕竟,如果400MHz数据速率的四个链路为您提供1.6GHz的总峰值带宽,则八个链路将为您提供3.2GHz。添加DRAM设备,电路板上的更多迹线以及ASIC上的相应引脚使总聚合峰值带宽加倍。

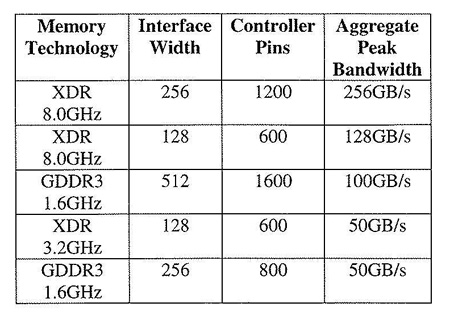

表2显示了使用不同内存技术和总线宽度可实现的总聚合峰值带宽以及每种配置所需的总控制器引脚数。

表2 各种存储器技术和总线宽度的总峰值带宽以及所需的控制器引脚数

然而,此增益是有代价的。首先,主要关注挤出每一盎司峰值带宽的架构师已经达到了他们在物理上设计其内存总线的宽度的可行最大值。找到具有256或甚至512位宽存储器总线的图形控制器并不罕见,这些存储器总线需要1,000个或更多控制器引脚。

封装设计人员,ASIC布局规划人员和电路板设计人员无法找到要布线的区域这些信号使用廉价的,商业上可行的手段。仅增加总线宽度以获得更高的峰值数据速率的另一个问题导致从列访问粒度限制减少的有效带宽。

假设特定存储器技术的突发长度等于1,则对于单个存储器事务,512位宽系统的访问粒度为512位(或64字节)。如果控制器只需要较小块的数据,则会浪费剩余数据,从而降低系统的有效数据速率。

例如,一个控制器只需要来自前面提到的内存系统的32字节数据将浪费剩余的32个字节,导致有效数据速率等于峰值数据速率的50%。请记住,这些计算都假定突发长度为1。随着存储器接口数据速率的增加趋势,大多数新技术的最小突发长度大于1。

核心预取

称为核心预取的功能主要负责最小突发长度的增加。 DRAM核心电路无法跟上I/O电路速度的急剧增加。由于无法再从内核串行获取数据以满足控制器请求,因此内核通常会为I/O提供远大于DRAM总线宽度的数据集。

本质上,核心向接口电路传输足够的数据以使其保持足够长的时间以使核心为下一个操作做好准备。例如,假设DRAM核心只能每纳秒响应一次操作。但是,该接口可以维持每纳秒两位的数据速率。

DRAM内核不是浪费接口的一半功能,而是每次操作取两个位而不是一个。在接口传输数据之后,核心已准备好响应下一个请求而没有任何延迟。添加的核心预取导致最小突发长度增加2,并将直接影响列访问粒度。

对于添加到总线宽度的每个附加信号,存储器接口将传输另外两位数据。因此,最小突发长度为2的512位宽存储器系统的访问粒度等于1,024位(128字节)。许多系统对最小访问粒度问题不敏感,因为它们以非常大的块访问数据。但是,有些系统依靠内存系统来提供小型数据单元,并从使用更窄,更高效的内存技术中受益。

表3 当今主流内存技术的单个内存通道的访问粒度和总线宽度值

结论

有效数据速率变得越来越重要存储器技术提高其峰值数据速率。在做出内存决策时,设计人员必须深入研究已发布的内存规范,并了解特定技术的功能如何与手头的应用程序进行交互。

内存系统设计人员必须超越峰值数据速率规范,就像CPU设计人员逐渐停止使用千兆赫作为唯一的性能指标一样。虽然峰值数据速率在内存接口方面仍然是最重要规范的标题,但有效数据速率开始为系统设计人员和架构师提供空间。明天产品的性能将在很大程度上取决于其内存系统的有效利用。

Victor Echevarria是Rambus公司内存接口部的RDRAM产品经理。他于2002年加入Rambus担任系统工程师。在加入Rambus之前,Victor与安捷伦科技公司合作,后者开发了用于高速数字采样示波器的软件。

-

内存储器分为随机存储器和什么2024-10-14 4222

-

内存储器一般由rom和ram组成吗2024-08-06 4361

-

内存储器与外存储器的主要区别2024-05-22 9100

-

STM32F7系统架构和存储器映射2023-09-08 514

-

存储器和总线架构2021-08-05 1069

-

单片机的片内存储器和片外存储器到底有什么区别2019-08-15 11243

-

内存储器和外存储器的分类与区别2019-05-26 42935

-

具有不同的存储器单元和存储器架构的微控制器介绍2019-01-24 4698

-

内存储器的分类2019-01-07 35708

-

相变存储器(PCM) :新的存储器技术创建 新的存储器使用模式2018-05-17 3339

-

KeyStone存储器架构详解2011-08-15 4147

-

KeyStone存储器架构2011-08-13 4701

全部0条评论

快来发表一下你的评论吧 !