怎样减少信号完整性悲观

描述

随着纳米几何尺寸的生产设计数量的增加,信号完整性(SI)已从一些前沿设计师的关注发展成为一个普遍的噩梦适合所有设计师。

虽然已经发展了几种方法来解决这些SI挑战,但是在130纳米以下的几何形状中,意外电气效应和迅速增长的设计复杂性的汇合导致了指数SI报告的违规行为。因此,设计受到延长的设计时间表的影响,并且通常会错过市场窗口。

延长130纳米以下设计周期的一个关键因素不仅是噪声灵敏度的提高,而且还有一些SI闭包方法中存在的过度悲观情绪,特别是SI分析引擎。虽然需要合理的余量来构建必要的保护带以帮助设计人员充满信心,过度的悲观情绪会大大增加设计周期并导致过度设计。

过度设计通常会导致拥堵增加,从而影响产量,增加功率,包括泄漏和#151; 90纳米及以下设计的主要问题。

这种过度悲观主义大部分来自用于估算SI的基础模型以及用于简化分析过程的一些权衡。然而,通常,由于过度修复和过度约束设计实现,分析中的快捷方式导致更多的设计迭代。因此,在选择SI闭包或分析解决方案时,应特别注意确保对错误违规进行充分过滤。

2Noise-glitch假失败过滤

SI分析将确定由于切换相邻攻击者网络而在给定受害者网络上可能发生的最坏情况故障。在毛刺分析期间,有许多技术可用于过滤悲观情绪,例如使用逻辑关系和时序窗口来确定可以同时切换的攻击者网络集。

这种类型的过滤通常会将毛刺违规次数减少两到三倍。下一级过滤确定计算的故障是否可能导致功能违规。

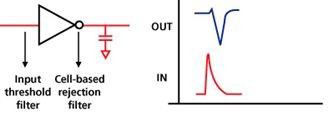

最基本的毛刺检查是根据预定义的阈值电压(电源的40%)检查毛刺的高度。这种方法通常会产生数以千计的违规行为,其中绝大多数都是错误的(见图1)。

这是因为CMOS逻辑门充当低通滤波器,因此大多数噪声毛刺被接收逻辑门衰减。如果噪声在到达存储元件(如触发器或锁存器)之前被抑制,则不会导致功能问题。

图1&#151 ;基本噪声干扰滤波

第二级故障滤波超出了简单的噪声峰值阈值滤波。它是基于单元的拒绝,依赖于毛刺在通过一个逻辑阶段传播时的行为方式。基于单元的拒绝确定接收器输入处的噪声是否会传播到输出。

检查细胞排斥有两种方法。一种是使用预先表征的拒绝曲线,另一种是利用相关的寄生效应对接收机进行实时仿真,以了解它在存在计算的噪声时的行为。

后一种方法更加真实,并且会过滤更多违规行为,因为前一种方法必须使用毛刺的悲观近似作为等腰三角形。然而,虽然基于单元的拒绝通常会比输入峰值检查减少5-10倍的噪声干扰,但这种方法在低于90纳米的几何尺寸下耗尽了蒸汽,并且仍然报告了许多不一定构成任何问题的悲观故障。设计问题(见图1)。

3高级毛刺滤波

噪声传播扩展了基于单步的基于单元的抑制方法,并在多个逻辑门之间传播SI毛刺以注册端点。允许这些毛刺与沿路径的其他串扰引起的毛刺相结合。

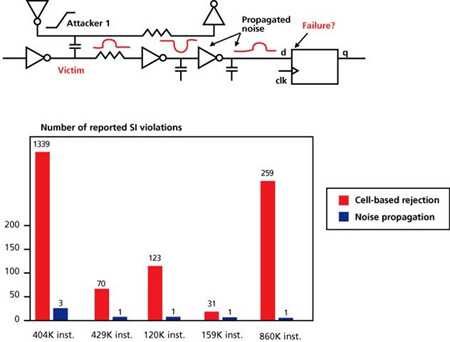

实际上,只有那些大到足以导致顺序元件(锁存器/触发器)发生功能故障的毛刺才会被标记。几个真实的客户设计已经证明,使用噪声传播与基于单元的抑制相比,报告的SI毛刺数量显着减少,通常为一个或两个数量级(参见图2)。

图2 - 噪声传播和毛刺悲观减少

噪声传播通过逻辑门传播毛刺并检查确保功能有效性寄存器不是不稳定的。与传统方法相比,噪声传播到寄存器端点可将误判数量减少一个数量级。

噪声传播最好通过即时晶体管级仿真实现,而不是通过预先表征传播表。传播表不能准确地考虑噪声源的组合,例如在多个输入处具有毛刺的单元,或传播噪声,电源噪声(IR降或接地反弹)和串扰的组合。

当毛刺通过接收器传播时,它会动态降低接收器的保持强度,使其对输出端的串扰更加敏感。此外,传播表的表征是繁琐的,通常需要数周时间来创建必要的数据以涵盖所有可能的输入毛刺场景。

4SI延迟减少悲观

虽然逻辑和时序窗口的使用将减少SI延迟计算的悲观性,但由于SI而具有几纳秒的额外负余量并不罕见。因此,在存在SI的情况下关闭时间是非常具有挑战性的。很多SI延迟悲观主义是由于悲观的时序窗口迭代,噪声转换(转换)的表示和传播,以及攻击者和受害者网络的对齐方式。

5定时窗口迭代

由于SI延迟变化取决于时序窗口,时序窗口取决于SI,因此精确分析需要在SI延迟计算和静态时序分析之间进行迭代。加速SI分析的一种常用技术是首先计算SI延迟效应(忽略时序窗口),然后仅在关键路径上进行迭代。然而,这种加速会增加悲观情绪,因为非关键网络的时间窗和时滞会被高估。因此,非关键网络攻击关键网络的影响也将是悲观的,并导致过度的延迟变化。

更好的方法是从标称时序窗口开始,对所有网络执行快速迭代,逐步重新计算时序窗口发生变化的网络。这样,用于最终SI延迟变化计算的所有网络都使用实际的时序窗口和转换。

6SI转换传播

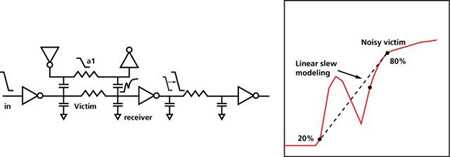

大多数时序和SI分析仪使用线性斜坡来模拟转换,但这对于具有颠簸非线性转换的噪声网络来说并不是一个很好的近似。线性斜坡往往更加悲观,特别是如果它们以相同的方式测量转换,以用于噪声和非噪声转换。使用传统测量(例如20-80%的电源)将极大地高估噪声转换对下游逻辑路径的影响。

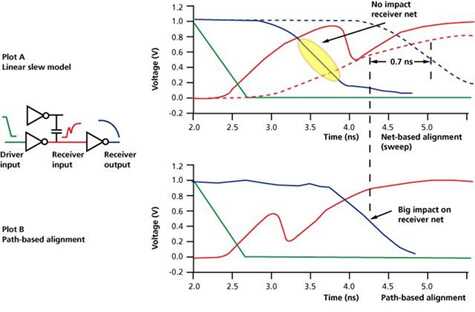

例如,在图3中,攻击者A1定时在受害者切换为高电平的同时切换为低电平,从而导致SI引起的路径延迟增加。由此产生的红色凹凸上升波形很难用线性回转模型精确建模。

如果转换阈值是Vdd的20-80%,则会报告大的转换退化,导致下游路径上出现相当大的延迟悲观。所需要的是SI延迟方法,其准确地考虑接收器输出的有效转换影响。

图3—由于线性回转造型不足造成的悲观情绪

另一个错误来源是受害者网络的驱动模型。通常,驱动程序使用2D表进行建模,其中表具有一组输入转换和输出负载。

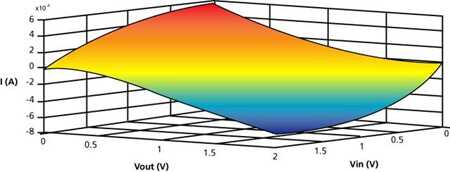

但是,将开关波形映射到相应的转换值是“多对一”映射。换句话说,可能存在具有相同转换值的许多不同波形。受串扰影响的开关波形恰好存在这种情况,导致不准确的串扰路径延迟。为了精确地模拟这样的波形,基于电流源需要更精确的驱动器模型,或者在非线性波形的情况下,基于驱动器的实际晶体管。如图4所示,基于电流的延迟模型独立于特征化的“良好表现”的转换值,有助于消除传统延迟表的不准确性。给定任意输入波形,它可以精确计算接收器门输出的延迟。

图4—延迟测量和基于电流的延迟模型

接收器输入和输出的转换和延迟的精确计算可以通过基于电流的延迟模型来实现,该模型将输出电流表征为输入和输出电压以及内部电容的函数,包括米勒电容。

攻击者的位置

受害者的延迟根据攻击者的相对切换时间,网络可能会发生很大变化。 SI延迟分析将确定对齐攻击者所造成的最坏情况延迟变化,同时尊重受害者和攻击者时间窗口施加的约束。

然而,这种方法存在两种悲观来源。首先,最坏情况的攻击者/受害者对齐可能发生在受害者的时间窗口的中间,因此可能不会改变其前沿或后沿到达时间。其次,受害者网络的最坏情况延迟可能是由于过渡后沿的噪声而发生的 - 太迟而无法影响接收门。

为了解决第一个悲观来源,攻击者对齐应该找到最大化受害者时间窗口扩展的,同时应该拒绝其他对齐。即使是那些产生较大延迟但对时序窗口影响较小的那些。

为了解决悲观的第二个来源,应在接收器输出而不是输入端进行SI延迟测量,以确保攻击者的对齐确实会对下游逻辑产生最大的影响。这种称为基于路径的对齐(见图5)的技术消除了局部的基于网络的最坏情况结果(局部最大值),而是提供了考虑下游路径的全局最坏情况结果(全局最大值) )。

图5—基于路径的对齐和SI延迟悲观减少

如图5中的情节A所示,传统对齐会在接收器输入的波形尾部产生噪声冲击(红色),但是这对接收器输出波形(蓝色)没有影响。然而,线性回转模型将接收器输入波形解释为点红色波形,这导致悲观接收器输出点蓝色波形。

在图B中,基于路径的对齐导致最坏情况的接收器输出波形(蓝色),这是由受害者网络上更早的攻击者对齐引起的。请注意,接收器输出波形中没有可感知的压摆性能下降。最终结果是线性回转模型的路径延迟悲观减少了700ps。

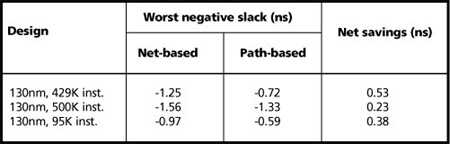

基于路径的对齐已经证明,在几种工业设计中,SI对延迟的不良悲观情绪显着减少(见表1)。

表1—基于路径的对齐悲观减少结果

表1比较了三种130nm设计中基于路径的对齐与最差情况下基于网络的对齐的使用。当使用基于路径的对齐时,最坏情况下的负松弛显着减少,使得更容易实现SI闭合。

基于路径的对齐的另一个好处是它能够利用接收器的固有滤波,以便在明确定义的平滑接收器输出上执行转换和延迟测量。即使对于毛刺幅度大于电源电压一半的非常崎岖的波形也是如此。因此,接收器输出上的压摆测量也不那么悲观。非常重要,因为它影响下一个逻辑阶段的延迟。

8结论

随着工艺技术的缩小,潜在的SI问题的数量非线性增加。这使得设计闭合几乎无法实现,除非工程师采用使用先进滤波技术(如噪声传播和基于路径的对齐)的精确SI分析。这些技术将使设计人员能够处理少数真实的SI违规行为,按时完成设计项目并按时交付。

期待65纳米工艺及以下工艺将需要在减少SI分析悲观主义方面取得进一步进展。特别是,需要基于统计和概率的技术来逼真地处理片上工艺变化,并且沿着长关键路径的最坏情况SI延迟的不可能累积增加。

责任编辑:ct

- 相关推荐

- 热点推荐

- pcb

- 华强pcb线路板打样

-

何为信号完整性?信号完整性包含哪些2021-12-30 2872

-

信号完整性原理分析2009-11-04 1287

-

什么是信号完整性2009-06-30 5874

-

ESD保护时怎样维持USB信号完整性2009-12-30 2624

-

信号完整性与电源完整性仿真分析2011-11-30 2109

-

电地完整性、信号完整性分析导论2016-02-22 1357

-

信号完整性与电源完整性的仿真分析与设计2016-12-14 2137

-

怎样学好“信号完整性”?2017-08-29 21541

-

信号完整性系列之信号完整性简介2021-01-20 2587

-

信号完整性系列之“信号完整性简介”2021-01-23 2599

-

信号完整性与电源完整性的仿真2021-09-29 1646

-

什么是信号完整性?2023-06-27 3603

-

信号完整性分析科普2023-08-17 9235

-

信号完整性与电源完整性-电源完整性分析2024-08-12 3274

-

听懂什么是信号完整性2024-12-15 1385

全部0条评论

快来发表一下你的评论吧 !