时钟域交叉分析方法

描述

片上系统(SOC)设计的最大挑战之一是不同的块在独立时钟上运行。通过处理器总线,存储器端口,外围总线和其他接口集成这些块可能很麻烦,因为当异步接口未正确同步时可能导致不可预测的行为。

检查正确的同步通常是一个耗时的手动设计过程。通常,时钟域交叉(CDC)的许多可能问题被忽视,导致主要的下游设计问题。

市场上出现了许多工具来识别CDC的问题。不幸的是,这些工具经常报告数百个明显的问题,其中许多通常是虚假的。这仅用于结构性CDC分析。如果要更深入地检查,必须在设计中添加断言。此时,错误错误的数量会增加,通过它们所需的时间也会增加,并找到真正的问题点。

有一种方法可以减少这个过程的痛苦。它需要明确的同步规则和CDC分析方法,该方法可以与设计中不可避免的ECO(工程变更单)顺利运行。此外,您的CDC工具必须支持轻松拒绝漏报的方法,并支持不需要在每个设计ECO上重新生成的豁免技术。

同步规程

同步中的挑战是有很多方法可以做到这一点。虽然每种方法都有优势,但在设计中 - 以及在设计组织内 - 临时使用不同技术会使审查过程复杂化。

今天没有工具可以完全按下CDC验证。总是需要一定程度的设计智慧来解释结果并考虑系统级的含义。必须对各种同步技术做出这些判断将不必要地使审查过程复杂化。

许多成功的公司已经认识到这一点,并且只是强制要求必须通过预先设计的单元格或使用一小组预先批准的技术来执行同步。虽然这可能会略微限制创作自由,但同步质量的信心可以弥补这种损失。

应该预先批准的技术取决于他们必须支持的应用范围。作为最严格的级别,可以强制要求所有同步通过预定义的同步单元进行。

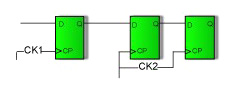

最常见的同步单元支持单比特,通用总线和快速到慢速的数据同步。更轻松的方法允许手工制作这个逻辑,但仍然需要从一组有限的样式中绘制插入的逻辑。在后一种情况下,通常需要添加变体 - 同步器的同步复位或半周期移位以降低元稳定性或数据丢失的可能性。图1a和1b显示了两种常见的同步技术。

图1a - 单位亚稳态同步

图1b - 多位同步

在选择CDC工具时,务必确保该工具支持设计中所需的所有技术。更复杂的工具允许设计人员基于各种同步样式定义方法,包括最常用的技术,用户命名的同步单元和用户定义的结构,这些结构将与域交叉结构进行模式匹配。

虚假域名交叉

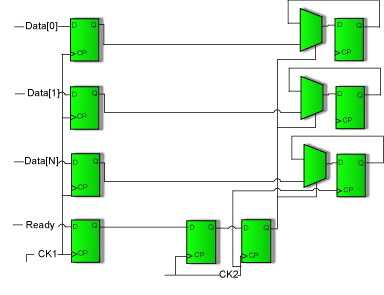

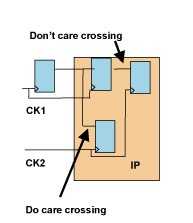

许多时钟域交叉通常是由复位或配置信号引起的(见图2)。虽然技术上可以在这些准静态信号上发生同步问题,但它将是一次性事件,并且由于此后信号是有效静态的,因此可以在设备的大部分正常运行时间内有效地忽略它们。

消除这些错误路径的最佳方法是使用与合成或静态时序分析相同的技术 - 声明错误路径。例如,您的CDC工具可能表明rst_n占交叉的50%以上,而配置[0]和配置[1]则占25%。如果您不想查看这些情况,可以通过错误路径约束轻松地抑制它们:

cdc_false_path-from rst_n

cdc_false_path-from config [*]

错误交叉的另一个来源是功能错误的路径。作者不知道今天会自动消除功能错误路径的任何CDC工具,可能因为该分析可能非常昂贵并且可以说除了设计者通过一些简单约束指定的值之外几乎没有增加价值。

例如,考虑使用CPU主机和多个I/O接口从机(如PCI或USB)驱动的总线。总线仲裁器的设计使得从机可以与CPU通信,反之亦然,但从机无法直接与从机通信。但是,CDC分析可能会显示usb_ck和pci_ck等域之间的域交叉。同样,使用错误路径约束可以很容易地拒绝这些:

cdc_false_path-从use_ck到pci_ck

cdc_false_path-从pci_ck到usb_ck

在某些情况下,通过指定直通点可以进一步优化错误路径:

cdc_false_path-from(state)-through(thru-point)-to(end)

这是必要的改进,当确定从/到对在功能上是有效的,但只能通过某些路径。

图2 - 假时钟域交叉的例子

FIFO同步

虚假域交叉的另一个有趣的来源可以是FIFO同步器中的推断内存。通常的做法是在将每个指针同步到相对的域之前对读和写指针进行灰度编码,以便比较和生成满标志和空标志。在读数据信号周围可能发生微妙且很少提到的错误交叉问题。想想如何在RTL中描述这一点:

总是@(posedge read_clk)

如果(read_en == 1'b1)read_data <=> =>

always @(posedge write_clk)

如果(write_en == 1'b1)mem [write_addr] <=> =>

这是一个非常合理的FIFO核心描述除了CDC分析将检测写入和读取时钟之间的域交叉和“read_data”之外。

事实上,这个域名交叉是虚假的,这是一个有趣的原因。虽然理论上可以从与写入相同的地址进行读取(同时),但大多数同步器设计会在读取和写入之间强制执行一些延迟,从而确保在同一地址中不会发生写入和读取。相同的周期(任何一个时钟)。这种延迟确保读取数据至少在几个周期内有效地准静态,因此不能成为域交叉。

一个好的CDC工具可以自动检测和拒绝这些情况。

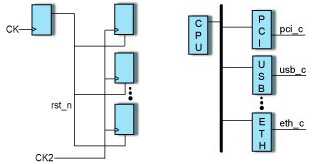

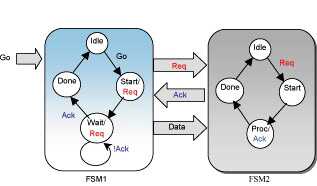

握手同步

一种非常常见且稳健的同步多个数据信号的方法是握手技术,如图3所示。这很受欢迎,因为握手技术可以轻松管理时钟频率的变化,同时最大限度地减少交叉口的延迟。但是,握手逻辑比标准同步结构复杂得多,大多数工具都不会自动识别。在这些情况下,传统的隐式CDC分析将报告所有交叉数据信号的非同步域交叉。

图3 - 握手同步是时钟域交叉中常用的技术

各种正式工具都有属性(断言)检查握手结构的特性 - 例如,在目标寄存器完成数据捕获之前,不得取消置位REQ。但是所有这些技术都要求设计人员手动识别握手并为每个这样的结构插入这些断言。

虽然检查这些属性有好处,但这仍然给设计人员带来了确保所有握手确实已被分析的主要负担。同样,这些结构将导致错误的CC报告,只能通过手动检查来消除。

一些最新的CDC工具可以自动检测一大类握手结构,大大减少了CDC报告中的漏报。这也允许工具对握手结构进行功能分析和隐式检查,完全不需要设计人员定义和插入这些检查。

第三方IP

今天几乎所有的设计都包含一些外部知识产权(IP),无论是内部开发还是商业收购。对于如图4所示的IP,除了进入的检查检查之外,重复检查内部域交叉和同步技术几乎没有价值。在大多数情况下,您无法更改IP的内部,因此任何报告的问题都只是额外的噪音。更重要的是分析围绕该IP和其他设计的CDC,其中IP域和设计域之间的交互可能导致新问题。

某些CDC工具提供约束来屏蔽指定IP内部的所有域交叉报告,同时仍报告其他逻辑与这些IP之间的交叉。这使得检查更容易,更有效。

图4 - 与IP块相关的时钟域交叉点

评论和ECO分析

即使已经消除了所有这些杂散源,也可能需要检查大量可能不同步的域交叉。这些可能来自在复位或配置信号意义上不是准静态的信号,但已知在使用之前“足够长时间”是稳定的。

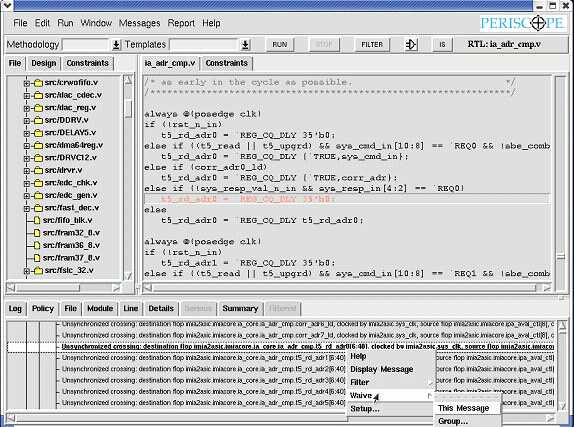

一旦审查并批准此类案件,除非您选择,否则无需再次查看。处理这些案件的一种实用方法是放弃,在RTL代码内部或外部应用,以标记案件已经过审查和批准。

易于使用和灵活的点 - 和如图5所示,单击豁免方法优于“正式放弃”一种或多种违反任何类型的行为。应该智能地应用这些豁免,适应RTL代码的更改,因此很少需要更新它们。如果需要,这些豁免和他们压制的CDC仍然可以进行设计审查或最终通过,以重新验证所有域名交叉点。

图5 - 豁免违规的点击式方法

功能分析

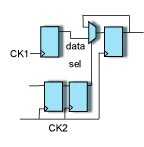

CDC的功能分析是自然延伸到结构分析。每个识别的同步结构带有一个或多个功能要求。例如,考虑一个常见的多路复用循环同步器,如图6所示。

图6 常用的多路复用再循环同步器

多路复用器驱动目标域中的寄存器,并且仅在选择时允许数据从源域传递,否则多路复用器将寄存器输出值再循环。选择“sel”必须与指定域同步。

到目前为止,这是一项结构性检查。在这种情况下所需的功能检查是当选择“sel”变高时源数据信号“data”是稳定的。由于选择和数据信号是自动识别的,因此应该是自动检查。

此类中的其他检查包括快速到慢速域跨越保持时间,灰色编码检查,握手检查等等。这些检查不会减少,也可能增加报告的问题数量,但在准确的结构识别基础上这样做,大大降低了误报的可能性。

-

FPGA跨时钟域处理方法(一)2023-05-25 3207

-

跨时钟域处理方法(二)2023-03-28 1864

-

揭秘FPGA跨时钟域处理的三大方法2022-12-05 2672

-

关于跨时钟域信号的处理方法2022-10-09 8555

-

SpinalHDL里用于跨时钟域处理的一些手段方法2022-07-11 3169

-

多时钟域的设计和综合技巧系列2022-04-11 5836

-

介绍3种方法跨时钟域处理方法2021-09-18 23590

-

关于跨时钟域的详细解答2021-04-27 5293

-

三种跨时钟域处理的方法2021-01-08 2344

-

vivado约束案例:跨时钟域路径分析报告2020-11-27 7011

-

多时钟域的同步时序设计和几种处理异步时钟域接口的方法2020-07-24 5499

-

关于FPGA中跨时钟域的问题分析2019-08-19 4059

-

FPGA界最常用也最实用的3种跨时钟域处理的方法2017-11-15 14834

-

跨时钟域信号的几种同步方法研究2012-05-09 1345

全部0条评论

快来发表一下你的评论吧 !