pcb设计和电源之间怎样来权衡

描述

在进行比较复杂的板子设计时,你必须进行一些设计权衡,而这些权衡会存在一些影响到PCB的电源分配网络设计的因素。

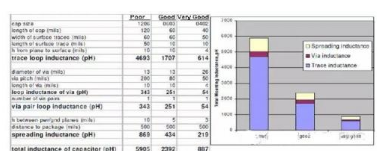

当电容安装在PCB板上时,会存在一个额外的回路电感,这个电感就与电容的安装有关系。回路电感值的大小依赖于设计,回路电感的大小取决于电容到过孔这段线的线宽和线长。走线的长度即连接电容和电源/地平面的长度、两个孔间的距离、孔的直径、电容的焊盘等等。如图1所示为各种电容的安装图形:

图1 最佳的和最差的电容布局

对于电容的安装和传播电感,接下来是三种不同情况的设计。图2表示的是各种设计情况对回路电感量的引入情况:

图2 最佳的和最差的电容布局

情况1-差的设计

设计人员不关注电源分配网络(PDN)的设计。

孔的间距没有优化。

电源和地平面间的距离没有优化。

孔到电容引脚之间的走线距离较长。

对于整个回路电感大小来讲,回路电感主要来自所布的线,因为与其它两种情况比较,差的设计的线长是它们(较好的设计和非常好的设计)的5倍。从安装电容的底层到最近平面的距离也是回路电感大小的主要因素,因为这是没有优化的(10mil),走线对整个回路电感大小的影响非常大。同样,因为设计人员在电源和地之间用了10mil的电介质材料,那么回路电感的次要因素来自传播电感。过孔间的距离没有优化的效果相对于小孔的长度就没有那么显著,孔的影响在比较长的过孔时会变得更大。

情况2-好的设计

设计人员关注了部分电源分配网络(PDN)的设计。

孔的间距有所改善,孔的长度保持不变。

电源和地平面间的距离有所改善。

过孔到电容引脚之间的走线距离经过了优化。

走线的回路电感依然还是整个回路电感的主要贡献者。好的设计的走线回路电感要比差的设计情况的走线回路电感小2.7倍左右,因为设计人员减小了电介质的厚度,从10mil减小到了5mil,传播电感减小了一半。由于减小了过孔间的距离,过孔的影响有了一点点改善。

权衡多路设计的情况

在一块有多路外设的PCB打样板上,你的设计就不能再共享一个供电电源。这也许需要你通过你的设计去执行DDR的电源接口,联合各种I/O口的电源轨迹,或者联合各种接收端的电源轨迹以减少PCB的BOM成本和PCB的布局复杂度。

电源轨迹共享增加了PDN的复杂度,同时在PCB上和die的位置处也增加了大量的噪声。对于多路的情况,设计电源的分配解决方法主要有两步:

1、低频解决方法

2、高频解决方法

在非常低频的时候,第一步确保VRM的大小是否适合处理各种电流的需要。

低频去耦一定要考虑清楚各种组合电源供电电流的情况。Bulk电容一定要选择能覆盖目标阻抗所覆盖的频段,做到精确的知道频率范围是有困难的,因为这有一个区域超过了阻抗曲线。这是在die上给定的电源区域,建立在自己的最大电流消耗上,而不是与其它路电流相关联的由同一个供电电源供电组合的电流消耗。对于设计,bulk电容去耦的频率范围估计是从DC到大约5~10MHz。

这个例子是电源共享在核心电源供电(Vcc)和PCI Express hard IP Block(VccHIP)电源供电,例外的原因是:

VCC的电流会比VCCHIP的大很多。

对比VCC和VCCHIP,VCC的BGA的过孔电感会比VCCHIP低很多。

对比VCC和VCCHIP,VCC的截止频率会比VCCHIP低很多。

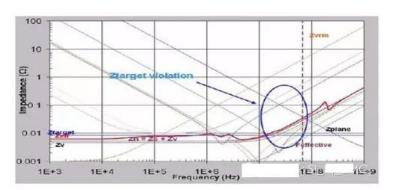

因此,对于电源设计情况,在BGA过孔处使用最高截止频率去耦是不适用的。如图3所示的是VCC、VCCHIP电源路组合阻抗曲线不符合目标阻抗的情况,相当于不符合VCCHIP的截止频率去耦,这是因为去耦电容效果被限制了。

图3 VCCHIP的截止频率阻抗曲线

在这种情况下,你必须基于PCB去耦项目用整个瞬态电流来计算目标阻抗曲线,相当于电源路截止频率的最大的电流消耗。在VCC和VCCHIP电源路共享的例子中,你必须用VCC电源路的截止频率。如图3所示为核心电源去耦的截止频率的组合电源路的阻抗曲线。对于核心电源,用沿着BGA的球或者过孔的(VCC+VCCHIP)的总电流得到阻抗曲线。那么你可以检查核对结果是否符合单个电源设计指导的目标阻抗。

基于同样的去耦项目与图4-A一样,图4-B所示为VCCHIP电源的阻抗曲线。但是,当得到这条曲线时,只有对于VCCHIP需要考虑电流消耗和BGA过孔数。如图4-B所示,直到VCCHIP电源的截止频率,VCCHIP的阻抗曲线都达到了目标阻抗。

最终的去耦项目必须达到各自目标阻抗的频率。如果存在一些特殊的违反设计目标的情况,可以尽量小的调整以优化去耦项目。

遇到类似的情况,可以根据VCC和VCCHIP的例子对任何供电电源组合进行优化。

在一块PCB板上,当有多个FPGA需要从同一个电源供电时,你可以使用相似的方法来应对这种情况。对于设计低频解决方案一定要用芯片的总电流消耗,对于高频解决方案设计,一定要用其中一个芯片的电流消耗。你可以使用同样数目的电容给其他芯片在高频情况时去耦。

- 相关推荐

- 热点推荐

- pcb

- 华强pcb线路板打样

-

PCB设计规则2016-08-13 5808

-

怎样去放置实时钻表来加速PCB设计?2021-07-22 1881

-

电源pcb设计2018-03-05 14840

-

pcb开窗怎么设计_PCB设计怎样设置走线开窗2018-05-04 40972

-

PCB设计中怎样消除反射噪声2019-08-17 3830

-

PCB设计电源平面应该怎样考虑哪些因素2019-08-23 2010

-

PCB的电源分配网络设计怎样来权衡2019-08-27 854

-

PCB设计的布线效率怎样来提高2019-08-31 2334

-

EAGLE CAD怎样做更简单的PCB设计2019-09-10 10454

-

如何使用pads专业管理来衡量整个pcb设计过程2019-10-24 2740

-

PCB原理图和PCB设计之间的关键差异2020-11-03 14645

-

开关电源PCB设计参考2022-12-29 4086

-

电源PCB设计实例2023-05-05 3444

-

DC电源模块的 PCB设计和布局指南2024-03-05 3125

-

PCB设计与PCB制板的紧密关系2024-08-12 1949

全部0条评论

快来发表一下你的评论吧 !