使用宏单元自动进行模拟/混合信号设计

描述

模拟和混合信号设计通常被认为是系统级芯片(SoC)设计中的重要瓶颈。事实证明,手动密集型过程难以自动化,因此很难获得模拟设计生产率的提高。

此外,与数字设计相比,模拟设计生产率难以衡量。您可以根据晶体管的数量来衡量数字生产力,但对于模拟设计,这是一个极具误导性的指标。复杂的混合信号模块可能需要数万个晶体管,而不是数字模块中的数百万个晶体管。

然而,这些街区所消耗的面积占整个集成电路面积的20%以上。技能不在于生成晶体管,而在于理解这些有源器件与片上无源元件(如电阻器和电容器)以及连接它们的金属轨道之间的关系。

数字设计师能够制造使用高度自动化的综合和布局工具。标准单元设计技术的使用支持了高水平自动化的动力,因为工具供应商能够使用标准单元为许多不同过程的工具提供通用基础。

在模拟设计中,没有真正标准的细胞。有标准功能,如偏置发生器和运算放大器。但是这些功能有许多不同的体系结构和拓扑结构,每个功能都必须针对特定的过程进行调整。

自动化仍可用于模拟设计

这并不意味着您无法使自动化工作。合成是模拟设计的两阶段过程。第一部分,也是最难自动化的部分,是拓扑选择和电路优化过程。第二种是生成各个电路元件并将其布置在物理设计中。

第一部分是大部分工程技能所在。很难生产出能够做出如此高水平决策的综合工具以及经验丰富的模拟设计师。

第二个是手动布局中的大部分繁琐,以及简单易犯错误的地方可以制作。这是设计综合的第二部分,其中定制自动化技术可以对生产力产生重大影响。

在成本范围的两端,许多模拟布局编辑器都有编程接口,可让设计人员实现自动执行结构和电路工作的函数库。有些人使用模糊的专有脚本语言,但有一些使用流行的C语言,使许多工程师可以访问它们,并在新工程师开始设计时帮助避免学习曲线。

这些工具还允许工程师构建允许输入和微调宏参数的用户界面。用户界面和底层代码可能与设计人员想要的一样复杂。

在编写模拟单元生成器宏时,最高效率在于将使用的组件和单元在许多项目中都有很多,这样可以收回投入的设计时间。

但这不是唯一的考虑因素。如果设计可能会随着时间的推移而发生变化,则参数化单元可以显着减少使设计适应新工艺所需的返工。即使设计过程不太可能改变,设计通常也需要标准部件上的许多小型变体。

同样,参数化的组件和单元可以相当容易地进行调整以实现这些变体,而无需为每个变体创建和运行新脚本。同样值得注意的是,特别是对于新工艺,代工厂通常几乎每周更改设计规则,需要更改布局规格的线宽和间距等。可以快速轻松地修改宏以适应这些规则变化。/p>

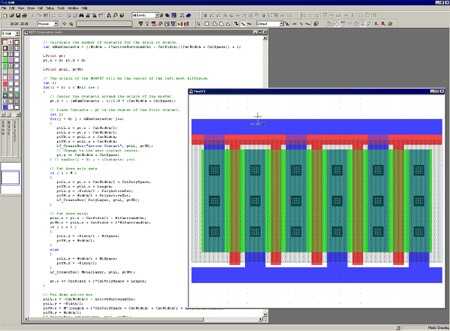

图1—可以快速修改宏以适应流程变化或创建零件变体。第一眼看到,编写宏来创建参数化组件和单元格似乎只适用于更复杂的组件。然而,工艺限制意味着即使是电阻器,电感器和电容器也需遵守相当数量的设计规则,以确保在代工厂的工艺限制范围内能够以所需的精度创建它们。

此外,在许多模拟电路中,例如放大器,如果要避免不需要的偏移电压,设备之间的良好匹配与实现精确的绝对值同样重要,并且需要良好的屏蔽来保护关键节点免受干扰。在开发布局时,这些注意事项适用于主动和被动组件。

即使是简单的组件也需要手动创建

电阻器

对于小电阻器,可以使用直线段;一些过程也支持'狗骨'形状。直段电阻器的最终电阻值取决于段的长度,宽度,厚度,薄层电阻和薄层电阻率。

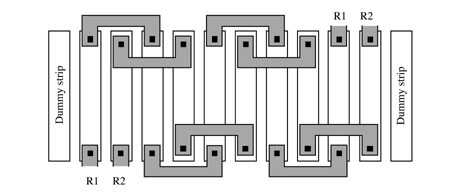

折叠蛇形结构通常用于较大的电阻值,以实现更好的匹配并最大限度地减少硅芯片面积。在这里,拐角会引起匹配问题,因为它们对工艺变化更敏感,并且使用金属而不是多晶硅来制造匝数以实现最佳匹配是一种好的做法。

因此,蛇形电阻器由一系列矩形段构成,为了在电阻器之间进行精确匹配,必须从顶部和底部看到相同的几何形状。当在主电阻器段的每一侧上形成虚拟电阻器时,湿法和干法蚀刻工艺都会导致底切效应不太明显。

如图2所示,Interdigitization是一种缓解流程变化以实现更好匹配的常用方法。显然,电阻器的布局可能涉及许多参数,更好的模拟工具有助于创建电阻发生器,每次运行宏时都可以输入参数,以快速生成所需的电阻。

图2—诸如具有虚设条带的叉指式蛇形电阻器之类的结构非常复杂,足以保证投入时间来编写发生器宏。

电容器

IC中的电容器是平行板型的。大多数是金属 - 绝缘体 - 金属(MIM)结构。在精度很重要的情况下,“真实”电容器元件外部的虚设元件再次经常用于通过减轻底切效应来提高工艺精度。一些较新的工艺允许在电容器周围使用虚设带而不是虚设电容器;这可以减少避免工艺可变性问题所需的硅面积。

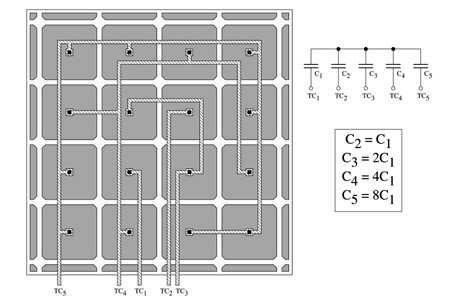

MIM电容器的实际尺寸受到可由较低层维持的金属重量的限制,因为金属的重量可以在中间比在边缘周围更多地压缩氧化物层。这和诸如氧化物厚度之类的工艺变量意味着电容器通常需要被分解成更小的元件,通常布置在共同的质心结构中。

这里存在折衷,因为较大的单个电容器在金属边缘处表现出较少的边缘效应,而电容器矩阵中边缘的总长度增加会增加该问题并且意味着必须使用更多的硅面积。然而,通过适当的互连,多元件方法具有消除两个或更多个电容器之间的不匹配的附加益处,因为可以布置布局使得过程变量均等地影响每个电容器。这些组件需要花费很长时间手工绘制,但编写一个生成这种电容器元素矩阵的宏是一件简单的事情。

图3—编写一个生成电容器元素矩阵的宏是一件简单的事情,例如在这种常见的质心结构中。

电感器建立一个电感发生器是一个类似的事情。在这种情况下,发生器宏将使用螺旋,轨道宽度和间距的匝数来创建电感器。宏可以在其他层中添加连接,以确保电感器可以轻松连接到电路的其余部分。

电感器通常由顶层金属制成,大多数工艺允许最高金属厚度。使用较厚的金属可以最大限度地降低电阻并最大化电感的Q因子。

寄生和杂散电容(横向和纵向)都会降低电感的Q因子。通过仅使用产生大部分电感的外螺旋可以在一定程度上缓解该问题,并且避免使用对电感贡献很小但对寄生效应更显着的内螺旋。对于更高的电感值,如果在布局中采取措施以最小化交叉耦合和电容,则可以在彼此之上创建电感器并且并联连接。

在电感器下方创建带图案的屏蔽也很有用。交叉耦合然后在屏蔽中产生与电感器中的电流极性相反的电流,从而最小化电感器到衬底的电容并保持Q因子。

再一次,显然简单组件可以从宏生成中受益匪浅;在IC设计中创建高Q值电感器时,可能需要处理的参数比第一次印象所能提供的要多得多。

晶体管

更复杂的元件在哪里C语言的强大功能,加上底层模拟工具的丰富编程接口,带来了最大的好处。基本晶体管易于绘制,实际上从一种设计复制到另一种设计。然而,具有高工艺容差的精心匹配的电路将是更复杂的元件。

使用宽,多指状晶体管通常更好,精度至关重要。在匹配的设计中,两个晶体管的指状物将相互交叉。这种结构很容易理解,但是很乏味且容易出错。

在实践中,所讨论的关于布置无源元件的大多数问题都适用于晶体管,复杂度更高;常见的质心结构,端部虚设备的使用,匹配的互连以及保护环的可能使用都需要考虑在内。宏可以在这里节省很多时间,同时保证每个阱和栅极的连接到正确的电源和信号线,它们是适当的宽度,并且器件具有适当的阱和栅极间距特性。

一旦晶体管发生器的基本库到位,特别是那些创建匹配元件的库,就可以使用电流镜和类似结构自动扩展宏的使用以构建本地电压源。有些人已经采取了更多措施,实施了完整的常用电路,如偏置发生器。尽管是最困难的选择,但这种方法在编程复杂性方面接近于细胞合成。拓扑—由设计人员决定。

通常,在参数化单元内可以非常容易地适应工艺变化,可能的例外是双极晶体管。这些都是与流程相关的,因此修改单元格需要做更多的工作。

设计,购买或免费使用

许多EDA供应商的设计流程免费提供标准构建模块的参数化单元。供应商自己提供它们,或者代工厂可能。其他供应商通常会出售一些标准组件,并为其他供应商提供开发服务。或者,设计人员可以选择创建自己的。

对于经验丰富的C编程器,可能会在几个小时内创建一个简单的电阻器或电容器,更复杂的晶体管可能需要长达几天的时间。使用频率,所需的组件或单元变体的数量,铸造过程的可控性以及过程或设计规则变化的可能频率将是决定前期努力是否会产生有价值的回报的关键决定因素。节省时间,或减少设计错误。

总结

虽然模拟设计师没有大量的工具他们对数字逻辑工程师的处置,并不意味着大部分流程无法实现自动化。即使是看似简单的无源组件也需要定义大量参数以适应组件变体,工艺可变性和潜在的设计规则变化,因此布局自动化在这里甚至是有益的。

参数化组件和单元的开发需要模拟设计团队的更多前期投资,或者可以增加EDA供应商开发的成本,但结果非常值得并确保设计人员可以使用他们来之不易的知识和经验来获得最佳效果,而不是花费宝贵的时间来简单地推动多边形。

Tanner EDA的产品经理Nicolas Williams与客户和开发部门紧密合作,生产EDA解决方案对于今天的设计问题。他还为产品开发,IC设计,设计套件开发和产品方向做出了贡献。他的专业领域是模拟EDA和模拟,混合信号和RF IC设计。

-

混合信号示波器的原理和应用2024-12-26 839

-

ETM嵌入式跟踪宏单元有哪些功能2023-10-30 2285

-

国产模拟/混合信号芯片厂商基本信息统计2021-02-23 9469

-

米尔科技Versatile Express 的软宏单元模型介绍2019-11-14 1819

-

免费模拟/混合信号设计和仿真2019-10-24 4259

-

如何使用mat专业的模拟混合信号分析工具设计2019-10-18 4906

-

混合信号设计的模拟工具2019-07-03 2469

-

请问如何进入汇编中断程序中的汇编宏单元进行调试?2018-10-30 3017

-

ADC SAR SEQ组件使用的宏单元数量多于数据表规格?2018-10-25 3130

-

采用标准单元库和阵列方法的混合模拟/数字ASIC设计2018-02-07 731

-

混合信号示波器探测模拟和数字信号的方法2017-10-15 927

-

小卫星信号处理单元模拟器设计2011-06-22 957

-

模拟和混合信号产品模拟应用学报2009-09-30 544

全部0条评论

快来发表一下你的评论吧 !