通用的交流信号电平移位器电路的介绍

模拟技术

描述

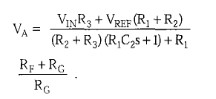

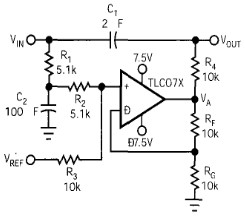

信号可由多种信号源产生,其中不少信号源与诸如TTL等最常用的接口电压不兼容。人们通常使用电容来耦合AC信号,因为电容耦合能滤除直流分置电平。但是电容耦合有时不适用,这是因为被耦合的信号电压在地电平上下摆动,所以必须增加直流偏置,以使被耦合的信号与接口电压兼容。此外,被耦合的信号所含的直流电压分量VDC随脉冲宽度变化而变化。当被耦合的信号振幅较大时,这种直流变化会对接口电压产生干扰。本电路能测量直流偏置,对电容耦合的信号进行相应补偿,并增加直流电平调节功能,从而能实现信号接口 (图1)。R1和C2构成低通滤波器(f3dB=0.312 Hz),用以测量输入信号的直流分量。其转移方程如下:

当R1+R2=R3和RF=RG时,VDC就转移至输出信号VA,这是由于VDC被乘以1/2(2)=1,即增益为1。相同电阻值的输出电压包含了VREF;这样,输出信号的电平就被移位了VREF,而不是VREF加上VDC。当输入信号的占空比变化,而不是输出电压随占空比变化时,运算放大器使输出电压电平保持恒定不变。VDC的增益必定为1,以便抵消交流耦合后的电压漂移。参考电压的增益可能大于1。例如,若R1+R2=3R3和RF=3RG,则直流分量为1/4(4)=1,而参考电压增益为3/4(4)=3。VREF可能为正电压也可能为负电压,因此可以用本电路来获得TTL、CMOS或ECL逻辑电平。C1和R4构成的时间常数必须足够大,以便使最低频率信号能够无失真地通过。只要运算放大器能驱动R4而不损失过多信号振幅,对R4的阻值没有严格要求。在有些情况下,可以将R4的阻值设为消除近端反射所需的驱动点阻抗。本电路可以按照配置情况方便地耦合400MHz数据,但是数据率取决于由R4和被驱动电路输入阻抗所构成的时间常数。

图1 本电路是一种通用的交流信号电平移位器;它符合任何一种接口标准。

-

基于运放实现交流信号的平移2022-10-12 4725

-

AC信号电平移动电路2011-01-02 2690

-

请问如何选择合适的电平移位器?2020-08-11 2316

-

交流信号电平移位电路资料分享2021-05-14 1692

-

电平移位电路(采用运算放大器TLC07X)2007-12-06 10048

-

新型的电平移位电路设计2011-06-13 1575

-

LTC6752,200MHz时钟恢复/电平移位2018-06-29 1379

-

AD8385:带电平移位器的10位、12通道抽取LCD DECDRIVER<sup>®</sup>数据表2021-04-20 783

-

ADSY8401:带VCOM、NRS缓冲器和高压边沿检测器的LCD电平移位器数据表2021-04-30 901

-

AN-224:利用AD7769实现输入/输出电平移位2021-05-20 1359

-

LTC6406阻抗匹配电平移位演示电路差动放大器2021-06-07 826

-

单端口HDMI/DVI电平移位器CS5218AN2021-08-10 882

-

单端口HDMI/DVI电平移位器/中继器CS5218中文数据手册2022-03-07 1111

-

CS5218单端口HDMI/DVI电平移位器/中继器中文资料2022-05-23 816

-

全方面解析应用于GOA TFT-LCD面板中的高压电平移位器-iML7272A2025-05-14 916

全部0条评论

快来发表一下你的评论吧 !