逻辑分析仪探头的物理形式

电子说

1.4w人已加入

描述

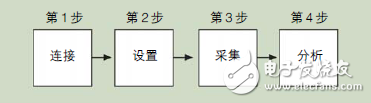

逻辑分析仪连接、采集和分析数字信号。使用逻辑分析仪分成四步:连接、设置、采集、分析。

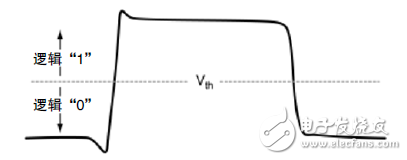

逻辑分析仪一次可以捕获大量的信号,这是其较示波器的主要优势。采集探头连接到SUT上,探头在内部比较器上,把输入电压与门限电压(Vth)进行比较,作出与信号逻辑状态(1或0)有关的决策。门限值由用户设置,范围为TTL 电平到CMOS、ECL 和用户自定义门限。

逻辑分析仪探头分成许多物理形式:

※通用探头,带有“飞线束”,用于点到点调试;

※高密度多通道探头,在电路板上要求专用连接器,探头能够采集高质量信号,对SUT的影响最小;

※使用无连接器探头的高密度压缩探头的连接方式,这种探头建议用于要求更高信号密度或无接器探头连接机制的应用,以迅速可靠地连接被测系统。

逻辑分析仪探头阻抗(电容、电阻和电感)成为被测电路上整体负荷的一部分,所有探头都表现出负荷特点。逻辑分析仪探头给SUT引入的负荷应达到最小,并为逻辑分析仪提供准确的信号。

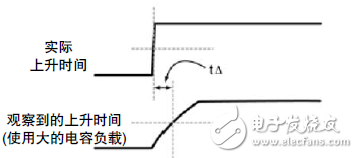

探头电容一般会“滚降”信号跳变边沿,这种滚降会降慢边沿跳变:

为什么电容这么重要呢?因为边沿越慢,越过电路逻辑门限的时间越晚,进而会在SUT 中引入定时误差。随着时钟速率提高,这个问题会变得更加严重。

在高速系统中,探头电容过高可能会使SUT不能运行,应一直选择总电容最低的探头。还应指出的是,探头夹和引线束会提高其连接的电路上的电容负荷。应尽可能使用正确补偿的适配器。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

逻辑分析仪探头在保持数字信号完整性中的作用2024-01-31 1264

-

逻辑分析仪是干啥用的 逻辑分析仪的主要用途 逻辑分析仪的应用场景2023-09-19 5600

-

探头在逻辑分析仪中作用是什么?2021-05-07 1877

-

如何使用逻辑分析仪来探测高速数字系统?2021-04-13 1848

-

逻辑分析仪探头如何实现正确连接,需注意哪些问题2020-08-07 6031

-

浅析逻辑分析仪的原理2019-06-28 2291

-

逻辑分析仪工作原理2018-04-02 3892

-

逻辑分析仪选型参数有哪些_逻辑分析仪有哪些技术指标_逻辑分析仪有什么推荐的?2017-12-20 6426

-

容易被忽略的逻辑分析仪探头2016-04-28 3199

-

如何选择和使用合适的逻辑分析仪2016-01-20 1170

-

逻辑分析仪年初扫盲2016-01-11 2299

-

逻辑分析仪的原理和应用2008-11-27 4124

全部0条评论

快来发表一下你的评论吧 !