怎样在PCB设计中消除反射噪声

描述

什么是反射噪音?它对定制PCB的功能有什么影响?如何通过更好的设计实践来缓解它?

这篇文章是受到“信号完整性院长”启发的系列文章之一,Eric Bogatin博士在Altium Live 2018上的主题演讲。

该系列的其他文章包括:

什么是电感以及它如何应用于接地反弹?

如何减少接地反弹:使用PCB设计降低噪声最佳实践。

最小阻抗路径:如何使用返回路径实现更好的PCB设计

本文重点介绍反射噪声以及如何通过智能布局减少噪声选择。

什么是反射噪声?

每当我们从PCB上的一个数字集成电路向另一个数字集成电路发送信号时,我们就会改变状态。信号线。状态的变化以及电磁场中伴随的变化可以描述为当波在电路中移动时的波。波浪是将能量从一个位置传递到另一个位置的现象,导体引导传播路径。

当电线的电位发生变化时,这是对电线周围磁能的一种艺术印象。

当反射噪声产生时电磁波遇到从一个介质到下一个介质的边界。当波遇到边界时,部分能量作为信号传播,部分能量被反射。

这个动画说明,当波浪从一种介质传播到另一种介质时,并非所有能量都被传输 - 一部分能量被反射回其源头。

对于电气工程师来说,发生这种边界的介质通常用其电阻来描述;也就是说,边界是阻抗变化的地方。

阻抗由电阻和电抗元件组成。电阻器将电路的能量作为热量耗散。电路中的可恢复能量存在于渗透并围绕导体,电感器和电容器的电磁场中。

每当电路中的阻抗发生变化时,一定量的反射将会发生。反射波将返回下一个边界(阻抗发生变化的位置)并再次反射。

此1D波形图显示了两点之间反射的波脉冲。能量随时间/距离衰减。

该过程将无限期地持续,直到能量被电路吸收或消散到环境中。

为什么反射噪声成问题?

对于信号线,驱动器和接收器上会有反射点。工程师的工作是尽量减少反射信号的数量,并通过阻抗匹配最大化传输信号的数量。

如果不可能,额外的能量需要在积累和淹没之前消散。输出带有噪声的信号。

如果反射脉冲的能量在下一个脉冲产生之前没有消散,那么能量将累积并增加一种称为叠加的现象。幸运的是,信号在通过电阻元件时会衰减。所以一个简单的串联电阻将消除大多数振铃。

评估数字信号中的噪声

傅里叶定理教导任何波或波脉冲都可以分解成一系列正弦和/或余弦波。如果你想更深入地了解这个概念,我推荐这个视频在伊利诺伊大学的Bill Hammack的谐波分析仪上。

如果你有一个足够小的上升/下降时间,一个脉冲可以保持数十个小振幅波。

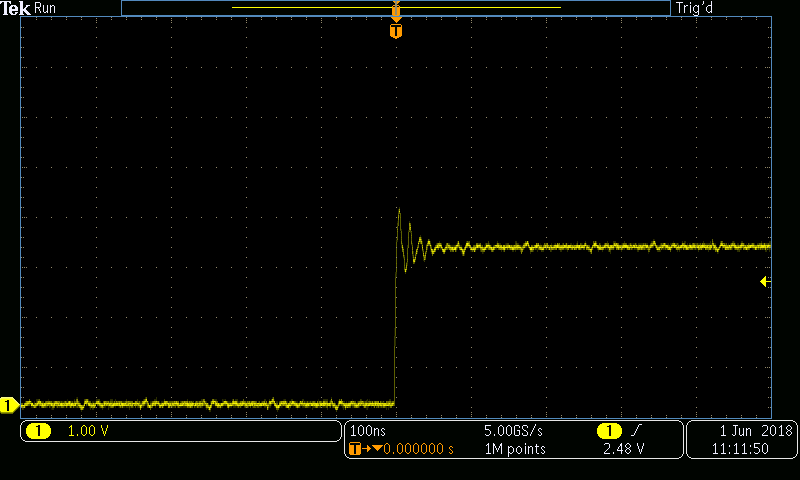

在下图中,您可以看到无阻尼数字信号切换逻辑状态从低到高。

在TI Lightcrafter上捕获的无阻尼数字信号(黄色,通道1),因为它将逻辑状态从低切换为现在看看下面的图像,其中左图显示了复合波脉冲通过逐渐叠加的减小幅度的奇次谐波而产生的复合波脉冲,现在看看下面的图像。原始波。对于实际感兴趣的信号,我们可以将波形分解为一系列正弦波。

如上图所示,真正的数字信号具有较大的带宽,并且该能量的任何部分都可能在电路中产生共振。这与具有非常窄的带宽且易于计算共振的RF信号形成对比。

如果你设法产生驻波,你将产生巨大的噪声源,可以压倒附近的任何信号线

这个gif表明在特定波长反射的波(橙色)可以与其反射相结合(蓝色)创建一个高振幅驻波(绿色)。这种现象将发生在1/2波长的奇整数倍处,其中波长是迹线长度的两倍。

如何降低反射噪声

您可以使用几种方法来管理设计中的反射噪声。以下是您可以使用的一些技术的概述。

保持恒定阻抗

您应该考虑的第一件事是如何保持跟踪的恒定阻抗只要有可能。请记住:当阻抗发生变化时会发生反射。

计算迹线的阻抗

为了保持恒定的阻抗,你要'我需要能够计算出迹线的阻抗。您的PCB程序应该允许您这样做,但也有在线工具可供使用。

一旦确定了跟踪和空间宽度,请沿着路线维护它们。

迹线的一致性

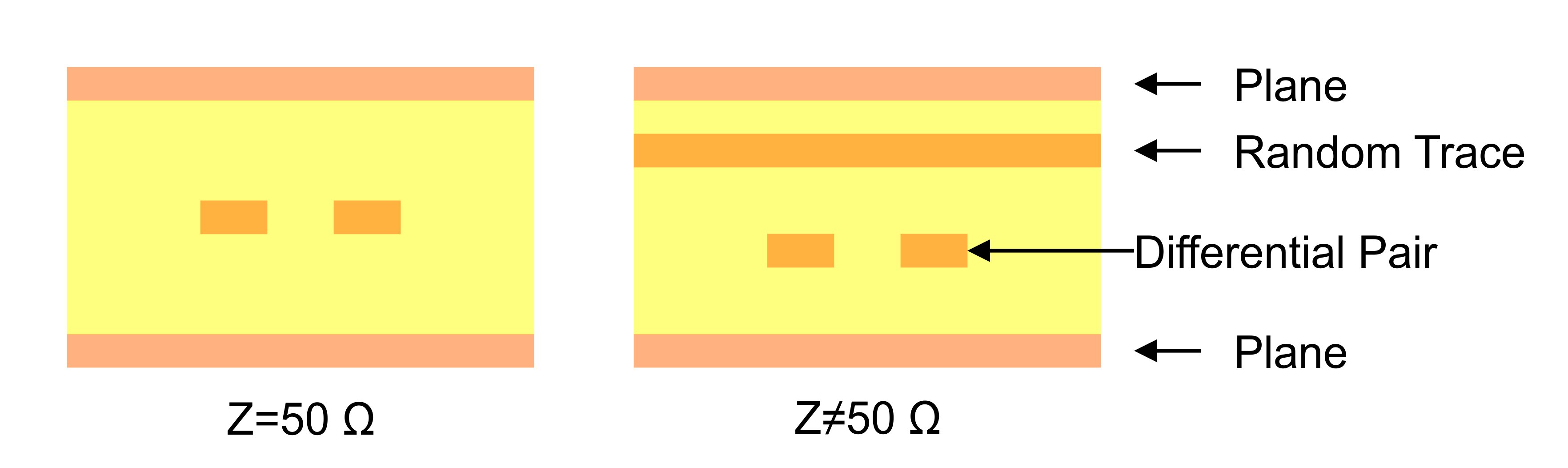

要保持差分对或单端迹线的恒定阻抗,必须保持恒定的迹线宽度,恒定间距和常数与所有其他导体分离。如果使用随机轨迹在阻抗控制对上进行路由,则会改变阻抗并创建反射点。

使用阻抗变化的阻抗匹配电路

当你必须改变时阻抗(例如从线性放大器到天线),使用阻抗匹配电路(使用史密斯图表,在线工具等计算......)。

减少反射点

您还可以考虑如何首先减少反射点的出现。

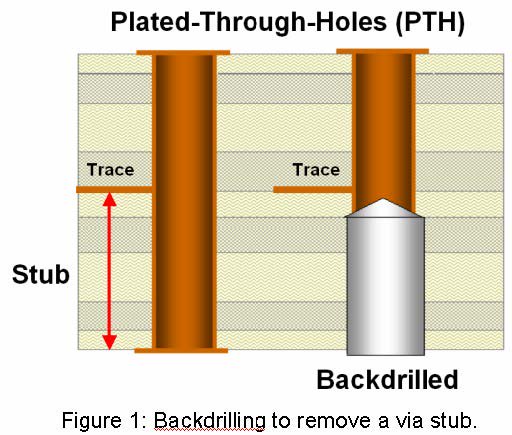

在电路板边缘观察过孔

对于高速电路设计人员来说,Vias可能是个问题。如果通孔超出信号走线延伸到未使用的层,则电路的阻抗会突然改变。在电路板边缘的过渡处,存在阻抗不匹配,因为迹线离开通孔(~50-150欧姆)并进入空气(~377欧姆)。这会在该位置产生反射点,严重降低信号。

反钻您的过滤器

解决方案是让您的PCB制造商“反钻”您的过孔在未使用的外层上从板上移除通孔。反钻通过显着改善逻辑转换。

来自Sanmina-SCI的反钻过孔

缓解现有反射噪声

使用阻尼电阻

另一项重要技术是在所有驱动信号源附近串联使用阻尼电阻,并具有快速上升/下降时间。这有时被称为缓冲电阻。

任何发生的信号反射都将每次通过电阻器都会快速衰减。这些通常是靠近驱动信号源(例如,时钟源,GPIO等)放置的<100Ω电阻。

一般的想法是创建一个阻尼电路 - 信号上升到适当的逻辑电平一次,没有过多的过冲和振铃。

摘要

对于高速信号线,保持恒定阻抗对于设计工作电路至关重要。将信号从一个IC移动到另一个IC时,请使用阻尼电阻以防止振铃。

如果您有其他意见或问题,请在下面分享!

- 相关推荐

- pcb

- 华强pcb线路板打样

-

PCB设计中降低噪声与电磁干扰的窍门2019-05-31 0

-

如何消除WM8978PCB设计中老存在的噪声?2019-07-23 0

-

高频PCB设计过程中的电源噪声的分析及对策2010-01-02 1108

-

PCB设计相关经验分享及PCB新手在PCB设计中应该注意的问题2013-09-06 1191

-

PCB设计中怎样消除反射噪声2019-08-17 2775

-

技术 | 如何解决PCB设计中的阻抗匹配问题2019-06-21 6883

-

PCB设计中,快速消除PCB布线的方法步骤2019-07-21 27883

-

pcb设计当中emc的接地该怎样设计2019-10-25 3129

-

PCB设计中的反射噪声怎样消除2019-08-20 4579

-

如何消除PCB设计中的电源噪声干扰2020-03-22 6833

-

PCB设计:消除过孔至过孔耦合噪声的技巧2020-09-18 3327

-

信号完整性分析及在高速PCB设计中的应用2022-07-01 515

-

降低PCB设计中噪声与电磁干扰24条2023-07-04 637

-

如何在PCB设计中克服放大器的噪声干扰?2023-11-09 713

-

在PCB设计中,如何避免串扰?2024-02-02 1866

全部0条评论

快来发表一下你的评论吧 !