为敏感电路设计清洁电源的基本规则概述

描述

低功耗,高性能电路经常受到电源相关问题的困扰。这种常见的情况经常是由于神话(或误用)的经验法则。

这些经验法则常常导致我们走向错误的方向,让事情变得更糟而不是更好。在本文中,我将重点介绍工程师最常犯的一些错误,并分享一些为敏感电路设计清洁电源的基本规则。应用这些规则将导致更高的性能,更低成本的设计和更少的设计迭代。

什么是敏感电路?

敏感电路是那些可以容易因电源噪声而降级。这些电路通常包括振荡器,LNA,收发器,混频器和ADC。我可能会收到许多读者添加到我的列表中的电子邮件,并且理所当然,所以请将这些作为一些示例而不是全面的列表。

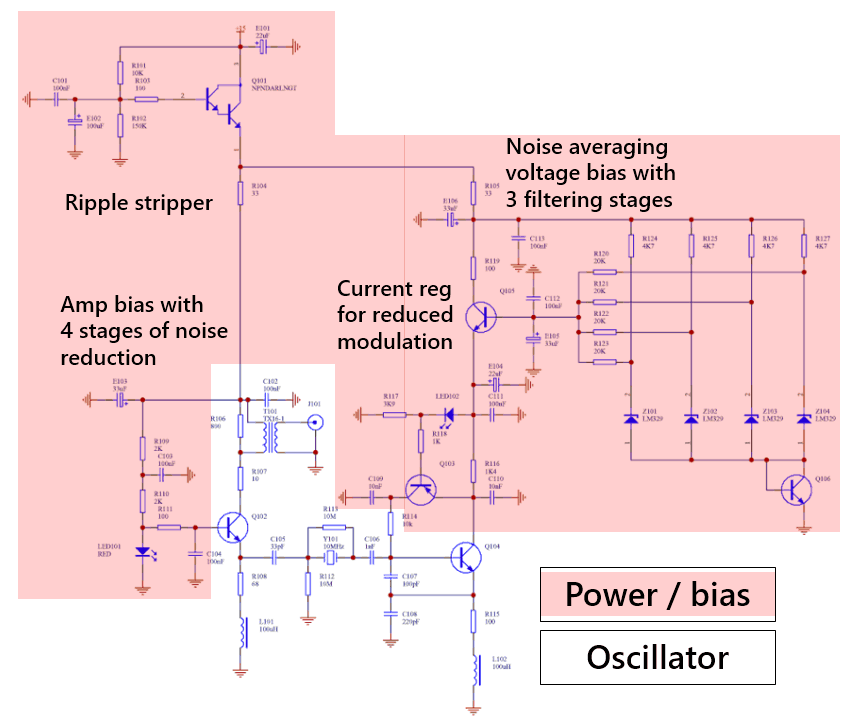

经验丰富的振荡器设计人员非常了解与之相关的挑战。电源。这在图1所示的振荡器原理图中非常明显。本设计中大约75%的元件与电源有关,而25%的元件与振荡器有关。

图。 1电路与白色振荡器有关,而电源电路则突出显示。

敏感电路对什么敏感?

显而易见的答案是电路对电源噪声敏感,对吗?图1中的振荡器电路可以表示为只有两个连接(或RF用户端口)的电路 - 电源输入和振荡器输出,因此您可能会得出噪声显然是由电源产生的结论供应。这个明显的结论是工程师在为敏感电路设计电源时所犯的最常见错误的原因。另外两个重要问题是噪声来自何处以及它是如何实现的?

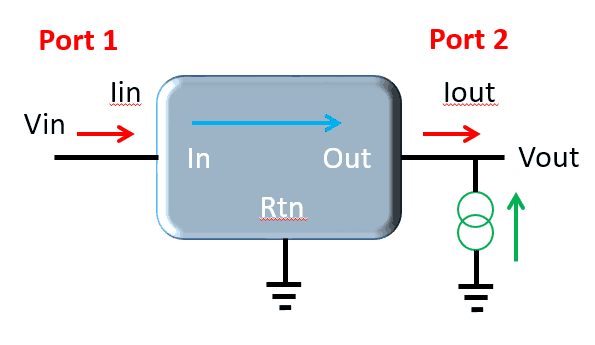

电源也可视为只有两个连接(或端口)的电路 - 电源输入和电源的输出。这种简单的视图,如图2所示,无论电源是包括电压调节器,无源噪声滤波器还是仅连接在电源输入和输出之间的导线,都是有效的。电源输出端的噪声是通过不同路径流向输出端的独立噪声源的总和。例如,电源输入端存在的电压噪声流过输出端。该路径定义为电源抑制比或PSRR。因此,电源的品质因数是PSRR,并且更高的PSRR性能导致在电源输出处出现的输入噪声更少。电源内部也会产生噪声。

对于开关稳压器,这很明显,但即使是线性稳压器也会产生噪声,并非所有稳压器都是相同的。因此,第二个品质因数是自发电源噪声。第三个噪声路径是电源呈现有限的非零输出阻抗的结果。电源输出的电流变化乘以电源阻抗,导致电源输出电压噪声。这些电流扰动可以由敏感负载电路,共享电源输出的其他电路产生,或者甚至由于耦合到电源输出的辐射电磁场产生。这导致了第三个品质因数;电源的输出阻抗。

图2简单的电源视图突出了三个主要的噪声源和路径,导致三个品质因数。

电源输出端的噪声量化为电源输出的总和。来自这三条独立路径的噪音。

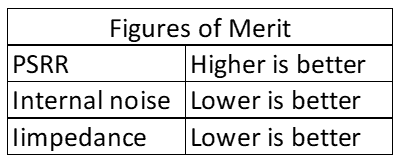

从前面的讨论和公式1中,我们可以总结出三个电源的优点,为敏感电路供电,尽管这些品质因数也广泛适用于其他电路。

工程师在这些应用中最常犯的错误

解决(1)需要至少三个数据:

电源噪声对敏感电路性能的影响

敏感电路产生的噪声电流。

敏感电路的阻抗

最常见的错误是设计没有这三个数据的电源。最常见的一个原因是尽管这些信息很关键,但它很少(如果有的话)作为电路规范或数据表的一部分提供,因此需要设计人员进行测量。获取这些数据对于设计具有成本效益的合适电源非常重要

明确的胜利之路

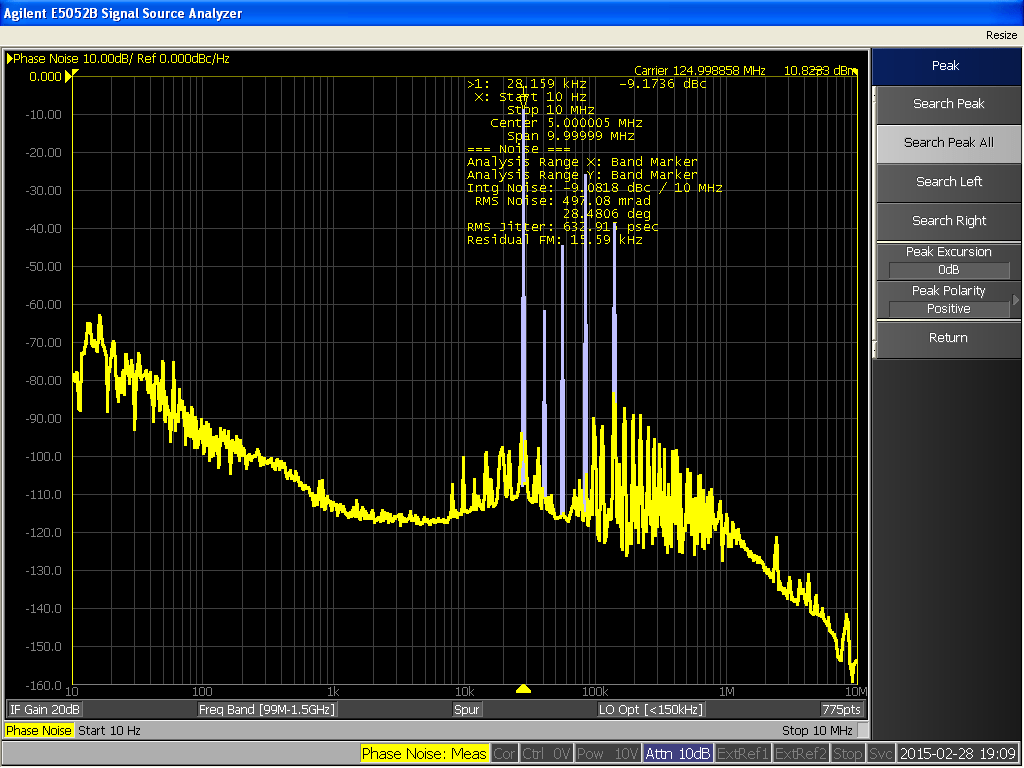

Don‘在获得或测量敏感电路对电源噪声的灵敏度之前,请执行任何其他操作。这通常涉及在洁净工作台电源和敏感电路之间连接Line Injector设备(https://www.picotest.com/products_J2120A.html)。在监视敏感电路的输出时调制线路注入器,在图3所示的示例中为振荡器。电源由20mV,28kHz正弦波调制。测量结果显示由电源调制信号产生的振荡器输出中的噪声杂散,以及调制信号的一些谐波。

Fig。 3使用线路注入器设备将20mV,28kHz正弦波添加到电源中,并监控产生的杂散。标记在-9dBc处表示峰值,而基数约为-110dB。 20mV噪声产生的杂散幅度为100dB。

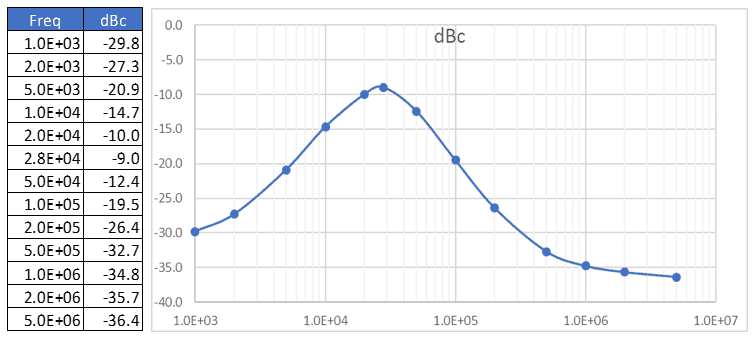

这个调制电源和监测产生的杂散的过程在很多频率上重复,结果列表并绘制成图,如图.4。

图4电源以多个频率进行调制,同时记录振荡器输出中的相应噪声杂散。结果以图形方式显示,突出显示了PLL的灵敏度。

图4中的图表显示被测振荡器对30kHz时的电源噪声最敏感。该响应是振荡器内部的锁相环(PLL)的典型响应。最大灵敏度的频率是PLL电路设计的函数,可以是几kHz到几十MHz的任何值。

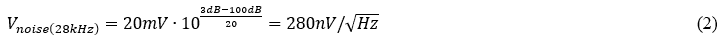

图3中的杂散幅度约为100dB,从大约-110dBc延伸到峰值为-9dBc。由于电源噪声导致3dB降级,28kHz时的电源噪声密度限制为最大值:

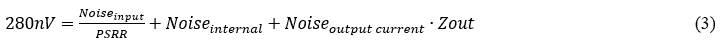

可以使用相同的步骤确定许多其他频率的电源噪声密度,从而提供与频率相关的噪声预算。代入(1)允许在三个噪声源之间分配噪声。

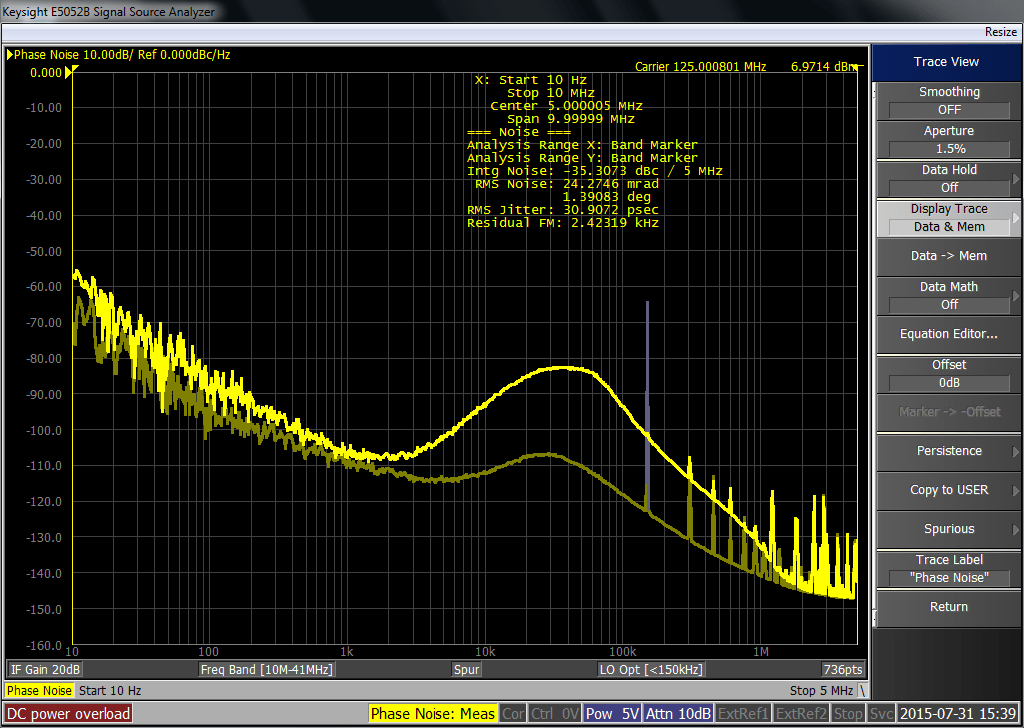

图5中测量的相位噪声曲线显示了低噪声低阻抗线性稳压器的结果,该稳压器直接通过2Ω串联电阻为振荡器供电。在这种情况下,这两条曲线在28kHz处的差异大约为26dB。同样,允许3dB降级会导致最大电源阻抗:

最小PSRR由输入到电源时的最大噪声确定供应为:

超过这些要求超过几分贝不会提高性能,因此无法证明更昂贵的电源。

图5振荡器相位噪声使用低阻抗电源测量,并且在电源和振荡器之间串联2Ω。额外的2Ω导致28kHz时相位噪声出现26dB的差异。》

第三种常见的失误是(不恰当地)添加铁氧体磁珠和陶瓷电容来过滤噪声或纠正由此引起的不足。前两个错误。评估敏感电路的输入阻抗非常重要,因为敏感电路内部通常有陶瓷电容。铁氧体磁珠在低频时可以非常电感,从而提高了电源的阻抗,因此需要电容来抵消电感。所需的电容可以由上面(4)中计算的磁珠电感值和输出阻抗确定。例如,使用电感为2uH的磁珠:

电容器的ESR应近似等于(4中计算的电阻) )以此为例:

请注意,所需的电容可能非常大。 降低 ESR和/或电容将导致阻抗谐振和降低的电路性能。最后一个考虑因素是该滤波电容的ESL可以与敏感电路内部的任何陶瓷电容共振。假设滤波电容ESL为2nH(对电解电容合理猜测),则保持低Q值以避免阻抗谐振,要求陶瓷电容为:

同样,如果该陶瓷电容器的ESR为0.14Ω,与(4)和(7)一致,则可实现最佳性能。这可能需要一个外部串联电阻或一个ESR控制的陶瓷电容。

结论

如果按照以下方法设计敏感电路的最佳电源很简单我在这里概述了三个步骤。

首先,获取电路电源灵敏度的数据。这通常意味着自己获取数据或要求供应商以类似于我在此处显示的形式提供数据。

其次,使用测量来确定电路对电源电阻的敏感度。/p》

第三,确保你知道电路输入电阻的阻抗。

参考文献

S 。 M. Sandler,时钟功率优化取决于抖动控制,电子设计2012年9月9日www.electronicdesign.com/analog/clock-power-optimization-depends-jitter-control

S上。 M. Sandler,对时钟抖动进行故障诊断并识别PDN灵敏度, EEWeb 2016年4月11日www.eweweb.com/blog/eeweb/troubleshooting-clock-jitter-and-identifying-pdn-sensitivities

Keysight如何设计Power Integrity YouTube视频系列www.keysight.com/find/how-to-videos-for-pi

解决时钟抖动问题, Keysight解决方案手册http://literature.cdn.keysight.com/litweb/pdf/5992-1645EN.pdf?id=2767985

低相位噪声设计:Crystal Oscillatorshttp://www.ko4bb.com/~布鲁斯/CrystalOscillators.html

- 相关推荐

- 热点推荐

- 敏感电路

-

什么是敏感电阻呢?敏感电阻包含哪些电阻器呢?2024-03-06 4273

-

为敏感电路提供过压及电源反接保护!2023-10-16 1498

-

通过Intel Curie进行运动敏感电路控制2023-06-19 710

-

无需阻塞二极管即可保护敏感电路免受过压和反向电源连接的影响2023-01-29 1810

-

DN497 - 为敏感电路提供过压及电源反接保护2021-03-19 1315

-

无需隔离二极管就可保护敏感电路的解决方案2021-03-18 718

-

什么是敏感电阻,敏感电阻的种类特点是什么2020-12-31 2507

-

什么是敏感电阻_敏感电阻种类特点2020-04-16 6010

-

敏感电阻的种类有哪些2020-01-11 10322

-

如何为敏感电路提供过压及电源反接保护?2018-10-29 2546

-

从应用实例看干扰敏感电路系统设计要点2018-09-28 2198

-

低噪声硅微陀螺敏感电容电荷读出电路设计_卢月娟2017-03-19 696

-

电路设计--含有耦合电感电路的计算2017-02-28 1108

-

同步电路设计技术及规则—华为2016-05-05 933

全部0条评论

快来发表一下你的评论吧 !