如何对接口芯片8255进行扩展

接口/总线/驱动

描述

一般说来,可编程接口芯片都有存储器及地址线,所谓可编程就是指CPU用指令将某数据写入接口芯片的某个存储器,接口芯片在接到CPU送来的数据后,自动翻译该数据,然后执行该数据所代表的动作。

不同的CPU对接口芯片的处理方式不同,某些CPU将接口芯片的存储器和CPU本身使用的存储器区别对待,将对接口芯片存储器的操作称为I/O操作,而对CPU本身使用存储器的操作称为存储器操作,并且I/O操作和存储器操作使用不同的指令,这种方式叫I/O端口的独立编址方式。

这种方式的优点是I/O端口不占用存储器的地址空间,存储器空间和I/O空间独立 ,缺点是CPU中要单独设置I/O端口访问指令,增加CPU的复杂度,INTEL公司的8086系列就是采用的这种结构。

另一种处理方式为将接口芯片的存储器当外部数据存储器对待,而不需要单独设置I/O端口的访问指令,这种方式称为统一编址,8051就是采用的这种方式。

下面我们介绍一下接口芯片8255。

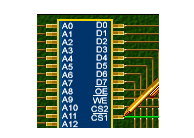

8255是一个并行接口扩展芯片。它有一个8位的待扩展并行接口D0-D7,三个扩展后的8位并行接口PA,PB,PC。四个存储器,PA口存储器,PB口存储器,PC口存储器和控制口存储器,这四个存储器由它的两条地址线AO,A1来选择。

当A1A0为00的时候,8255将D0-D7与PA接通

当A1A0为01的时候,8255将D0-D7与PB接通

当A1A0为10的时候,8255将D0-D7与PC接通

当A1A0为11的时候8255将D0-D7与内部控制寄存器接通

假设将两片8K的数据存储器和一片8255混合扩展成CPU的外部数据据存储器,它们的片选信号的接法采用译码方式 。

译码器74139的输入端接CPU的P2.5和P2.6。

当P2.6和P2.5为00时,译码器输出端YO有效,选中第一片数据存储器,可知第一片存储器的逻辑地址为0000H-1FFFH以及8000H-9FFFFH,每个物理单元有两个逻辑地址

当P2.6和P2.5为01时,译码器输出端Y1有效,选中第二片存储器,第二片存储器的地址为2000H-3FFFH以及0AOOOH-OBFFFH。

当P2.6和P2.5为10时,译码器输出端Y2有效,选中8255,,则8255的逻辑地址4000H-5FFFH,以及0C000H-0DFFFH。

当P2.6和P2.5为11时,译码器输出端Y3有效,没有存储器被选中,即这种情况下的地址为无效地址,包括6000H-7FFFH,和0E000H-OFFFFH。

来源;21ic

-

8255芯片资料详情2012-08-27 11798

-

AT89C52芯片与外部扩展8255A芯片连接问题2016-06-05 6946

-

有大神知道什么芯片可以扩展4个I/O口吗?(比如8255芯片,可以扩展3个)2018-04-16 5482

-

如何用8255实现接口扩展?2022-01-24 928

-

掌握可编程I/O接口芯片8255的接口原理使用2022-02-16 1334

-

8255并口扩展实验2008-09-26 6585

-

基于8051的Proteus仿真-8255实现接口扩展2016-09-01 864

-

可编程并行接口82552018-04-17 1646

-

8255可编程并行IO接口芯片的扩展仿真及程序资料合集免费下载2019-05-16 1341

-

8255接口芯片的引脚图及引脚功能的详细资料概述2019-09-08 25357

-

如何对并行接口芯片8255进行扩展设计2019-12-19 3480

-

使用8255芯片实现接口扩展的仿真电路图免费下载2019-12-30 1319

-

使用8255芯片实现接口扩展的程序和工程文件免费下载2020-09-02 1045

-

使用单片机和8255芯片实现接口扩展的程序和工程文件免费下载2021-03-19 1085

-

基于AT89C51单片机用8255实现接口扩展Proteus仿真及程序2023-05-05 939

全部0条评论

快来发表一下你的评论吧 !