关于嵌入式FPGA内部的原始构造块

可编程逻辑

1395人已加入

描述

(文章来源:EEPW)

FPGA中的可编程逻辑块是查找表(LUT),它可以通过编程实现任意布尔函数:4个,5个或6个输入具有一个或两个输出。

在Flex Logix EFLX阵列中,LUT是一个双4输入LUT,它可以组合形成一个5输入LUT。LUT输出可以任意存储在触发器中。LUT通常被分组为具有进位逻辑的四个组,以便于加法器和移位器。另一个可编程逻辑块是MAC(乘法累加器)或DSP加速器块。

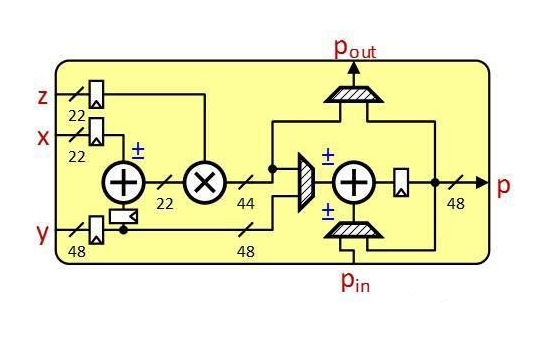

在Flex逻辑EFLX阵列中,有一个22位预加器,一个22x22乘法器和一个4位后置加法器/累加器。 MAC可以组合或级联以实现快速DSP功能。

可编程逻辑块由设置LUT数值的配置位编程,选择是否旁路使用触发器,是否激活进位逻辑等。配置位还对MAC的操作进行编程。通常在FPGA中,配置位从外部闪存加载。对于嵌入式FPGA,它是相同的,因为几乎所有的SoC都有一个从外部闪存引导的ARM/ARC /MIPS等处理器。同样的闪存用于存储嵌入式闪存的配置位。

可编程逻辑块接收输入并将输出发送到互连网络,该互连网络允许从FPGA架构中的任意逻辑块可编程地进行连接。互连结构同样也由配置位编程。互连结构通常是FPGA架构的主体。嵌入式FPGA的主要区别是互连结构的设计。最佳互连使用较小的面积和较少的金属层,同时提供资源的高利用率。

与FPGA芯片不同,嵌入式FPGA中没有PHY/SERDES/PLL。嵌入式FPGA中有一个I/O环,但它是真正简单的数字互连到芯片的其余部分。嵌入式FPGA有成百上千的互连,它们可以在芯片内全速运行。这种I/O宽度和带宽的增加是将FPGA嵌入到芯片的巨大优势。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

嵌入式fpga是什么意思2024-03-15 3677

-

fpga与嵌入式的区别 嵌入式和fpga开发有什么关系2024-03-14 9468

-

对嵌入式FPGA的详解2021-10-21 1043

-

FPGA中嵌入式块存储器的设计2021-08-04 923

-

FPGA实现嵌入式系统2021-07-30 1337

-

如何构造运行良好的嵌入式设备的驱动程序?2019-09-25 1673

-

关于FPGA的嵌入式系统的设计问题2017-11-24 1126

-

精通嵌入式Linux编程—构造自己的GUI环境2017-10-30 1026

-

基于FPGA的嵌入式块SRAM的设计2017-01-19 893

-

FPGA与嵌入式系统的区别2013-10-12 6055

-

关于FPGA的can总线嵌入式设计2013-02-06 2979

-

如何用FPGA实现嵌入式系统2009-04-02 8020

-

NI LabVIEW 8.6 全面简化嵌入式系统原型构造与发2008-08-12 847

全部0条评论

快来发表一下你的评论吧 !