PCB走线对信号时延的影响分析

EDA/IC设计

描述

信号在媒质中传播时,其传播速度受信号载体以及周围媒质属性决定。在PCB(印刷电路板)中信号的传输速度就与板材DK(介电常数),信号模式,信号线与信号线间耦合以及绕线方式等有关。随着PCB走线信号速率越来越高,对时序要求较高的源同步信号的时序裕量越来越少,因此在PCB设计阶段准确知道PCB走线对信号时延的影响变的尤为重要。本文基于仿真分析DK,串扰,过孔,蛇形绕线等因素对信号时延的影响。

1.引言

信号要能正常工作都必须满足一定的时序要求,随着信号速率升高,数字信号的发展经历了从共同步时钟到源同步时钟以及串行(serdes)信号。在当今的消费类电子,通信服务器等行业,源同步和串行信号占据了很大的比重。串行信号比如常见PCIE,SAS,SATA,QPI,SFP+,XUAI,10GBASE-KR等信号,源同步信号比如DDR信号。

串行信号在发送端将数据信号和时钟(CLK)信号通过编码方式一起发送,在接收端通过时钟数据恢复(CDR)得到数据信号和时钟信号。由于时钟数据在同一个通道传播,串行信号对和对之间在PCB上传输延时要求较低,主要依靠锁相环(PLL)和芯片的时钟数据恢复功能。

源同步时钟主要是DDR信号,在DDR设计中,DQ(数据)信号参考DQS(数据选通)信号,CMD(命令)信号和CTL(控制)信号参考CLK(时钟)信号,由于DQ的速率是CMD DDR2/ DDR3.DDR4预计在2015年将成为消费类电子的主要设计,随着DDR信号速率的不断提高,在DDR4设计中特别是DQ和DQS之间传输时延对设计者提出更高的挑战。

在PCB设计的时候为了时序的要求需要对源同步信号做一些等长,一些设计工程师忽略了这个信号等长其实是一个时延等长,或者说是一个‘时间等长’。

2.传输时延简介

Time delay又叫时延(TD),通常是指电磁信号或者光信号通过整个传输介质所用的时间。在传输线上的时延就是指信号通过整个传输线所用的时间。

Propagation delay又叫传播延迟(PD),通常是指电磁信号或者光信号在单位长度的传输介质中传输的时间延迟,与“传播速度”成反比例(倒数)关系,单位为“Ps/inch”或“s/m”。

从定义中可以看出时延=传播延迟*传输长度(L)

其中v为传播速度,单位为inch/ps或m/s c为真空中的光速(3X108 m/s)

εr为介电常数PD为传播延迟,单位为Ps/inch或s/m TD为信号通过长度为L的传输线所产生的时延L为传输线长度,单位为inch或m

从上面公式可以知道,传播延迟主要取决于介质材料的介电常数,而传播时延取决于介质材料的介电常数、传输线长度和传输线横截面的几何结构(几何结构决定电场分布,电场分布决定有效介电常数)。严格来说,不管是延迟还是时延都取决于导体周围的有效介电常数。在微带线中,有效介电常数受横截面的几何结构影响比较大;而串扰,其有效介电常数受奇偶模式的影响较大;不同绕线方式有效介电常数受其绕线方式的影响。

3.仿真分析过程

3.1微带线和带状线传输时延

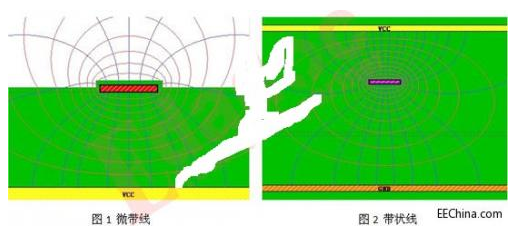

PCB中微带线是指走线只有一个参考面,如下图1;带状线是指走线有2个参考面,如下图2。

带状线由于电磁场都被束缚在两个参考面之间的板材中,所以走线的有效介电常数为板材的介电常数。

微带线会导致部分电磁场暴露在空气中,空气的相对介电常数约为1.0006,板材如常规FR4的介电常数为4.2,那么微带线的有效介电常数在1和4.2之间,可以利用下面的公式计算微带线的有效介电常数「Collins,1992」:

εe = (εr +1)/2 + (εr -1)/2(1+12H/W)-1/2 + F -0.217(εr -1)T/√WH 3.1 F = 0.02 (εr -1)(1-W/H)2 (W/H 1) 3.2

其中,εe为有效介电常数,εr为电路板材料的介电常数,H为导线高于地平面的高度,W为导线宽度,T为导线厚度。

图4微带线层叠与时延

图5带状线层叠和时延

在图4和图5的层叠结构下,1000mil的走线时延差=179.729ps-147.954ps=31.775ps,可以看出这个差距是非常大的。在做源同步的DDR同组等长时候只考虑物理等长会带来很严重的‘时间不等长。

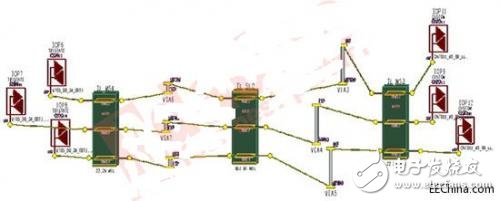

3.2走线和过孔传输时延

在PCB设计时候,经常会遇到走线换层,走线换层必须借助于过孔。但长度相等的过孔和走线之间的时延并不相等。过孔的时延可以用式3.3表示

TD_via=√LC 3.3

其中TD_via表示信号经过过孔的时延,L表示过孔的寄生电感,C表示过孔的寄生电容。从式3.3可以看出寄生电容和寄生电感都会导致过孔的传输时延变大。而不同过孔结构寄生参数也会发生改变。下面通过仿真分析过孔时延和传输线时延时间的偏差。

图6过孔结构及寄生参数

如图6所示过孔结构时延可以根据式3.3计算出:

TD_via=√LC=sqr(0.4021pf*1326.2pH)=23.1ps式3.4

由式3.4可以看出,结构如图6所示过孔的传输时延为23.1ps.而对于普通FR4板材的微带线,1.6mm走线传输时延约为11ps,对于带状线约为12.5ps.通过计算可以看出相同长度的走线和过孔之间的时延相差是非常大的。因此对设计工程师来讲设计的时候尽量做到以下两点:

1)需要做等长的信号要尽量走同层,换层时需要注意总的长度要保持相等并且每层走线都需要等长。

2)需要等长的信号走相同走线层可以保持过孔的时延一致,从而消除过孔时延不一致带来的影响。

3.3串扰对信号时延的影响。

PCB板上线与线的间距很近,走线上的信号可以通过空间耦合到其相邻的一些传输线上去,这个过程就叫串扰。串扰不仅可以影响到受害线上的电压幅值,同时还会影响到受害线上信号的传输时延。

图7串扰拓扑图

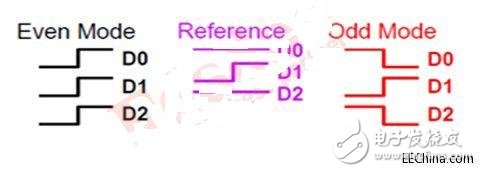

如图7串扰拓扑图所示,假设有3根相互耦合的传输线,中间的一根线(图8中D1)为受害线,两边的线(图8中D0

1,假设两边的攻击线中没有信号,即不存在串扰,此种情况作为参考基准线(Reference);2,假设攻击线和受害线切换状态一致,此种情况为偶模(Even Mode)

3,假设攻击线和受害线切换状态相反,此种情况为奇模(Odd Mode)

图8串扰仿真中激励

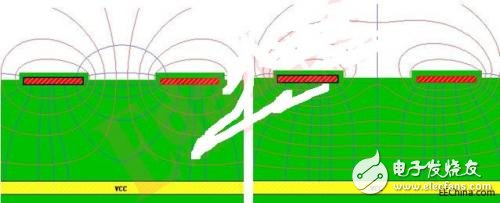

奇偶模式空间电磁场分布(如图9)

图9奇模电磁场分布图10偶模电磁场分布

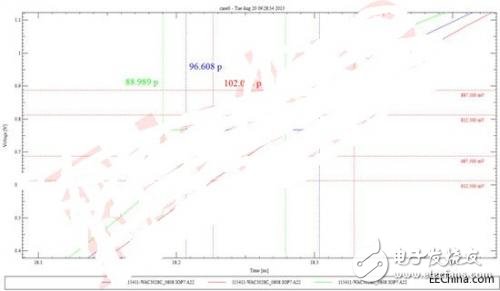

仿真结果如下图11所示,其中蓝色为第一种激励所对应的参考基准线,其周围没有其它信号线的影响;红色线为第二种激励所对应的接收端波形;绿色为第三中情况所对应的接收端波形。绿色波形最早到达接收端,而红色的波形最后到达接收端,是由于奇模的传输速度比偶模块。

图11串扰仿真结果

从上面的仿真结果可以看出信号线周围的攻击线会对信号线的传输时延到来影响,如果设计处理不当,导致传输时延偏差较大最终会导致系统工作不稳定。在设计的时候要尽量减小这种影响,可以从以下几点考虑:

1,拉大线间距。线间距越大,相邻走线间的影响就越小,走线间距尽量满足3W原则。

2,使耦合长度尽量短。相邻传输线平行走线长度越长串扰越大,走线时候尽量减小相邻线平行走线长度;对于相邻层走线尽量采用相邻层垂直走线。

3,走线尽量走在带状线。微带线的串扰相对带状线较大,带状线走线可以减小串扰的影响。

4,保持完整回流平面,避免跨分割,走线和参考面尽量紧耦合。

3.4绕线方式对信号时延的影响

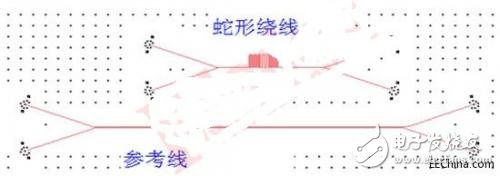

在PCB设计时候,有些设计人员为了满足等长要求会对走线进行绕线,很少有设计人员会考虑到不恰当的绕线也会影响传输线时延。为了验证绕线对传输线时延的影响,我们公司信号完整性团队(SI组)设计出测试板进行实测。如下图12所示,蛇形绕线和参考直线走在相同的走线层,两者线宽线间距以及物理长度完全相同,蛇形绕线的局部放大图如下图13所示。

图12蛇形绕线和参考走线

图13蛇形绕线局部放大图

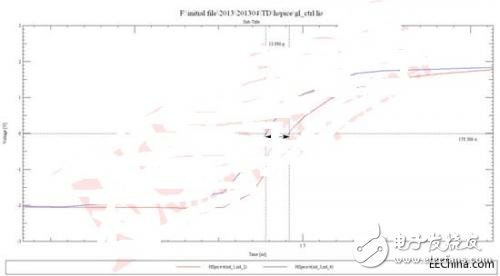

实测结果如下图13所示,其中红色线为参考走线,蓝色的线为蛇形绕线的走线,从结果可以看出,蛇形绕线的信号传输速度会比直线参考线的速度要快,两者相差了13.89ps.这是由于蛇形绕线靠的太近,平行的耦合长度太长,信号在蛇形绕线上的自耦合导致信号传播速度较快。

图13实测结果

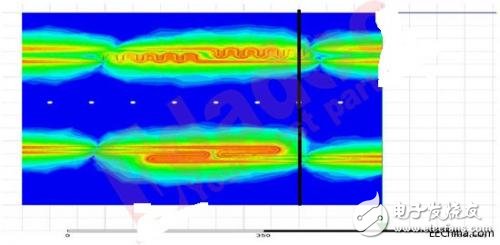

通过3D电磁场仿真软件也可以看出这种蛇形绕线和直线间传输速度不同,如下图14所示:两种不同的绕线是物理等长的,可以看出下面一种绕线方式由于绕线靠的较紧,而且平行耦合长度也长,可以看出下面一种绕线方式信号传输的会快一点

图14仿真结果

从上面的仿真测试可以看出,不同绕线方式对信号时延影响还是比较大的,为了减小由于绕线带来的时延的影响,可以考虑以下几点:

1,在PCB设计时候尽量减少不必要的绕线,比如串行信号差分对和差分对之间没有必要做等长。

2,增大绕线间间距,尽量满足单根绕线间距大于5H(H为线到最近参考面的距离),差分绕线大于3H(H为线到最近参考面的距离)。

3,减小绕线间平行走线长度。

4.小结

在PCB设计时候要将等长的设计观念逐步向等时设计转变,在对时序或者等长要求高的设计尤其需要注意串扰,绕线方式,不同层走线,过孔时延等方面对时序的影响。丰富的SI(信号完整性)知识和正确的仿真方法可以帮助设计去评估PCB板上的传输时延,从而提高设计的质量。

来源;互联网

-

高速PCB信号走线的九大规则2024-01-08 2725

-

详解PCB走线与信号完整性问题2023-04-03 3329

-

PCB直角走线的影响2022-02-11 2901

-

PCB板上多长的走线才是传输线?2020-11-06 7368

-

走线高速信号走线的九大规则2020-02-14 13694

-

PCB设计高速模拟输入信号走线方法及规则2018-05-25 10217

-

信号在PCB走线中传输时延分析2017-12-01 2301

-

浅谈信号在PCB走线中传输时延2017-11-29 2620

-

高速pcb信号走线的经典规则让pcb设计不再难2017-11-25 9015

-

PCB走线与摆件规则2016-07-21 3057

-

信号在PCB走线中关于串扰 , 奇偶模式的传输时延2015-01-05 6353

-

信号在PCB走线中传输时延(下)2014-10-21 3049

-

PCB板蛇形走线的作用2009-11-27 1205

-

PCB布线中的蛇形走线2009-09-13 5994

全部0条评论

快来发表一下你的评论吧 !