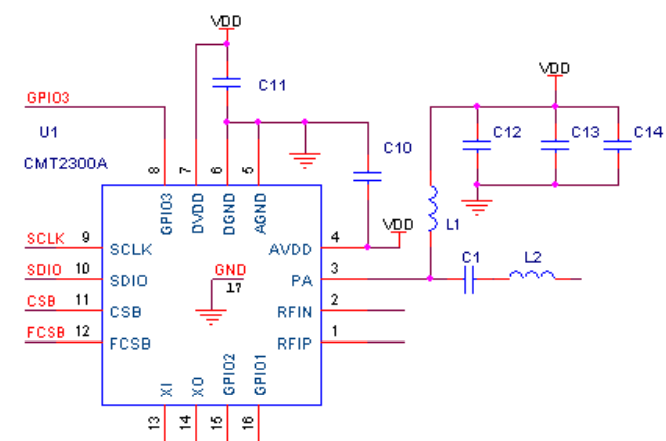

使用CMT2300A芯片设计射频匹配网络的数字信号和电源滤波电路与铺地

电子说

1.4w人已加入

描述

数字信号(包括串口和 GPIO 口)的走线注意事项如下:

1. 数字信号应尽量远离晶体和 RF 走线。

2. 数字信号应尽可能用地围起来,以减少相互串扰。

3. 在布线不合理或走线太长情况下,串口 CSB,FCSB,SDIO,SCLK 管脚容易受到干扰,功率输出(20dBm)越大,工作频率越低,受干扰的概率越大。

电源滤波电路设计

为了减轻电源上的噪声纹波对芯片的影响,及 PA 输出对电源的影响,用户应当在以下几处设计滤波电容。

1. C10 靠近芯片的 AVDD 管脚处。

2. C11 靠近芯片的 DVDD 管脚处。

3. C12, C13 靠近扼流电感, 建议 C13 保留以应对高次谐波。

4. C14 根据 PA 输出功率和供电电路性能,推荐值 4.7 - 10uF。

铺地设计

说明如下:

1. 参考地层:射频走线需要在相邻层有大片的连续地做参考平面,以实现高效的功率输出和最佳接收灵敏度。

2. 射频走线两侧包地并打过孔到参考地平面以减小杂散辐射。

3. 各层地网络打过孔到参考地层,减小回路路径,从而使回路的辐射减少。

4. 线路板边沿尽量铺地,且过孔间距不超过 λ/10,从而减小辐射和增强抗 ESD 能力。

5. IC 衬底一定要有几个过孔到地层,有利于提升芯片的射频性能指标。

6. 晶体电路对干扰敏感,用包地隔离。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

DP4330A与CMT2300A的区别资料2025-11-28 1030

-

如果要使用数字信号隔离芯片将AD7606对数字系统隔离,应该如何铺地?2025-04-16 4031

-

CMT2300A 433MHz Sub-1GHz无线收发芯片2022-12-29 1233

-

CMT2300A 433MHz无线收发芯片2022-11-11 2323

-

超低功耗Sub-1GHz性价比首选方案:CMT23002020-12-02 3512

-

为什么说CMT2300A是Sub-1GHz超低功耗的射频收发器2019-11-26 4503

-

使用CMT2300A芯片设计开关射频匹配网络电路的详细概述2019-10-04 10631

-

CMT2300A的开关射频匹配网络电路设计2019-09-27 7064

-

数字信号射频发射与接收基础2019-03-04 2022

-

CMT2300A 超低功耗Sub-1GHz射频收发器的详细中文资料免费下载2018-08-30 4064

-

CMT2300A无线数据收发模块资料2017-10-19 7129

-

数字信号处理之数字滤波2015-12-30 752

-

数字信号处理—数字滤波2015-12-29 700

全部0条评论

快来发表一下你的评论吧 !