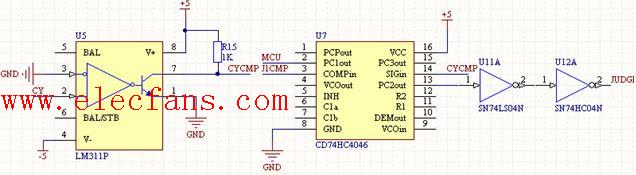

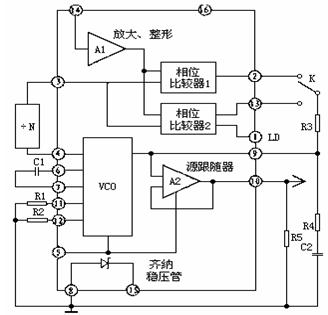

过零比较和相位比较电路原理图

信号处理电子电路图

359人已加入

描述

过零比较和锁相环相位比较器电路原理图如图

现在常使用集成电路的锁相环CD4046,是通用的CMOS锁相环集成电路,其特点是电源电压范围宽(为3V-18V),输入阻抗高(约

1脚相位输出端,环路入锁时为高电平,环路失锁时为低电平。2脚相位比较器Ⅰ的输出端。3脚比较信号输入端。13脚相位比较器Ⅱ的输出端。14脚信号输入端。对相位比较器Ⅱ而言,当14脚的输入信号比3脚的比较信号频率低时,输出为逻辑“

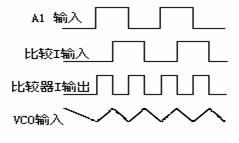

图2.13 比较器输出波形图

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

过零比较器的输出电压由什么决定2024-08-06 3135

-

求助,关于过零比较器过零点多次触发的问题2023-11-27 792

-

绘制电路原理图OpAmp比较器的sch库下载2021-12-06 980

-

过零比较器电路的用途_过零比较器原理介绍2018-02-26 77725

-

过零比较器的原理及特点详细介绍2018-02-24 98387

-

用比较器把正弦波转换成方波电路_过零比较器波形转换电路2016-09-05 189306

-

TLV3501过零比较器电路设计2016-08-08 41969

-

仪器仪表· 常用电路 过零比较电路2012-08-09 3310

-

过零比较器电路图2011-10-26 23965

-

迟滞比较器,迟滞比较器原理图分析2010-03-22 36099

-

绝对值相位比较器电路图2009-07-02 2540

-

过零比较器电路2009-05-15 10970

-

过零比较电路图2009-05-08 2356

-

迟滞比较器电路图,原理图2009-04-27 7666

全部0条评论

快来发表一下你的评论吧 !