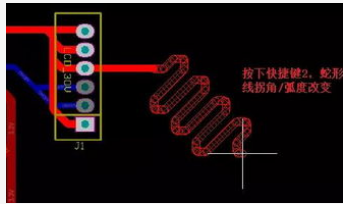

高速PCB设计中几种蛇形线的处理方式介绍

EDA/IC设计

1078人已加入

描述

1.尽量增加平行线段的距离(S),至少大于3H,H指信号走线到参考平面的距离。通俗的说就是绕大弯走线,只要S足够大,就几乎能完全避免相互的耦合效应。

2.减小耦合长度Lp,当两倍的Lp延时接近或超过信号上升时间时,产生的串扰将达到饱和。

3.带状线(Strip-Line)或者埋式微带线(Embedded Micro-strip)的蛇形线引起的信号传输延时小于微带走线(Micro-strip)。理论上,带状线不会因为差模串扰影响传输速率。

4.高速以及对时序要求较为严格的信号线,尽量不要走蛇形线,尤其不能在小范围内蜿蜒走线。

5.可以经常采用任意角度的蛇形走线,能有效的减少相互间的耦合。

6.高速PCB设计中,蛇形线没有所谓滤波或抗干扰的能力,只可能降低信号质量,所以只作时序匹配之用而无其它目的。

7.有时可以考虑螺旋走线的方式进行绕线,仿真表明,其效果要优于正常的蛇形走线。

来源;互联网

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

PCB布线中的蛇形走线2009-09-13 5994

-

蛇形走线用在哪里,一文告诉你2023-03-22 4089

-

谈谈走线方式蛇形线2012-12-18 3059

-

PCB设计处理蛇形线时的7点建议2014-12-09 1944

-

layout中蛇形线和差分线的使用与比较2018-09-21 3237

-

蛇形走线在PCB设计中的作用2018-11-23 2596

-

pcb蛇形走线2019-05-22 3388

-

PCB设计者必看之AD布蛇形线方法2020-06-24 7277

-

PCB蛇形线在高速系统中的主要作用2023-04-13 1067

-

PCB设计中布线的介绍从直角走线,差分走线,蛇形线等三个方面来概述2018-07-06 7105

-

高速PCB设计中的走线技巧2019-07-01 6678

-

PCB设计蛇形线处理要注意什么问题2020-01-22 2450

-

PCB特殊走线技巧——蛇形线2022-02-10 2079

-

PCB设计中蛇形走线的作用2023-03-30 6548

-

高速PCB设计中的射频分析与处理方法2023-11-30 2341

全部0条评论

快来发表一下你的评论吧 !