如何在Quartus II中创建一个4位加法器

电子说

描述

步骤1:启动Quartus

1如果尚未安装Quartus,请在您的计算机上安装。

注意:由于我使用的是校园计算机,因此不必安装Quartus。遵循安装向导,一切正常。

2)从主窗口中打开Quartus。

3)应出现项目向导。单击创建一个新项目。

参见图片

4)第一页告诉您有关项目向导的信息。单击下一步转到下一页。

5)选择要工作的目录。

注意:任何目录都可以。只是在这里保存文件。最好为您执行的任何项目创建一个文件夹。

6)将项目命名为4BitAdder。这还将显示为顶层设计实体。

7)单击到下一页。

8)我们将从头开始,除了程序中包含的基础知识之外,因此请再次单击“下一步”。

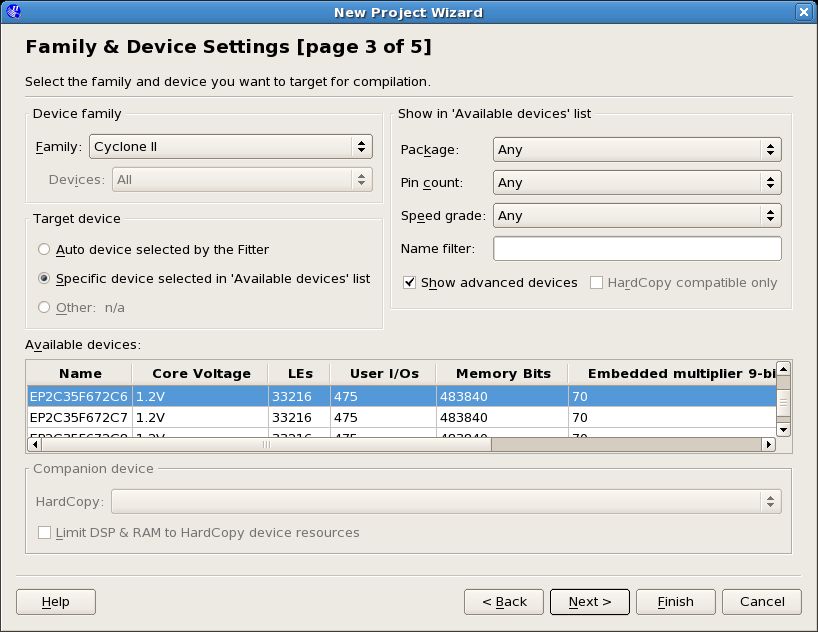

9)选择您拥有的FPGA的家族名称。 (旋风,地层等)。

10)您的设备在滚动栏中将具有特定名称。选择它并点击完成。最后两页将保持不变。

a)要弄清楚设备的系列名称和特定名称,请在FPGA上找到处理器。它是上面写有ALTERA的更大芯片。

b)姓氏将在第二行显示,且打印尺寸比ALTERA稍小。 c)姓氏下方是设备的特定名称,其中包含字母和

请参见图片

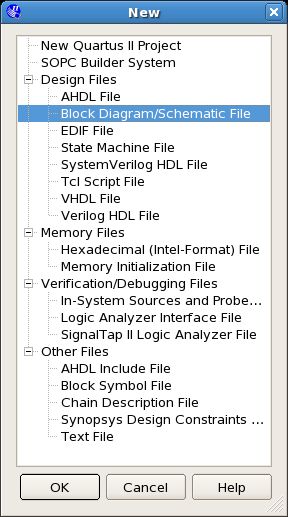

11)该项目将加载空白屏幕,显示Altera Quartus II。在左上角,单击“文件”,然后从出现的下拉菜单中单击“新建”。

12)从出现的窗口中选择“框图/原理图文件(BDF)”。屏幕将变为白色,并带有小点。

请参见图片

13)立即将文件保存为名称4BitAdder。出现保存屏幕时,该文件应默认为该名称。

注意:要保存,请单击文件,然后另存为。添加零件后,也可以单击工具栏中的软盘进行保存。

警告:请经常保存。已知计算机和软件会崩溃。为了避免丢失信息和重做步骤,请随时考虑保存文件。

此文件将是主项目所在的位置。较小的组件将在其他文件中创建并制成一个块,其中仅看到输入和输出,而没有所有的门和混乱。这些块较小,为项目创建的混乱程度较小。

步骤2:时钟发生器

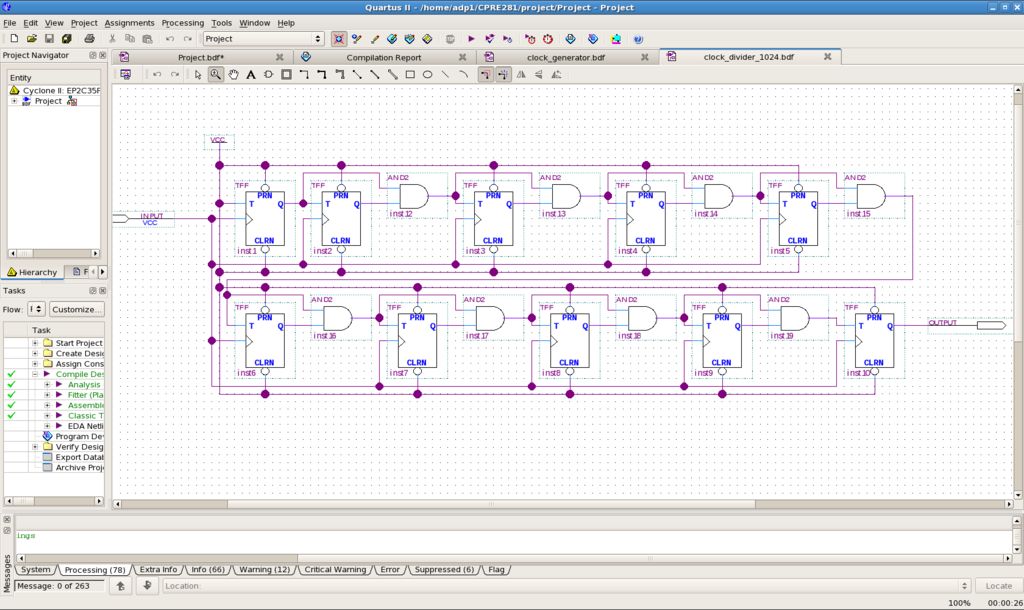

时钟驱动整个电路。最初,时钟产生于10MHz,对于我们的使用而言太快了。时钟将使用T触发器按比例缩小。您的时钟频率可能不同。检查一下它的频率,并调整T触发器的数量。我们的电路=(10 ^ 7)/(2 ^ 28)。将时钟设置为正确的频率可确保添加过程不会太快且不会超出您的控制范围。

1)开始一个名为clock_divider_1024的文件。文件-》新建

b)选择BDF

c)以给定名称保存

2)在该空间中放置10个T型触发器。

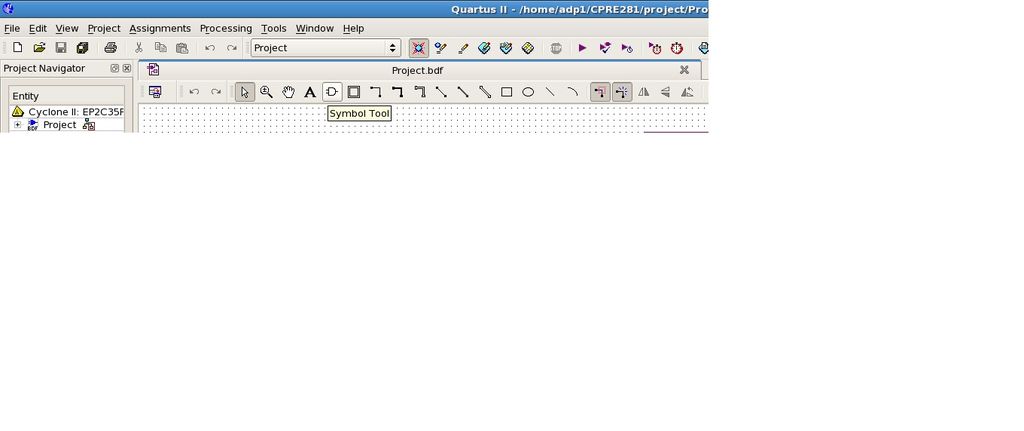

a)1)要添加组件,请单击工具栏中的符号工具。 (它看起来像是D,左侧有两根电线,右侧有一根。)

参见图片 a)2)您也可以双击空白区域以打开符号窗口。

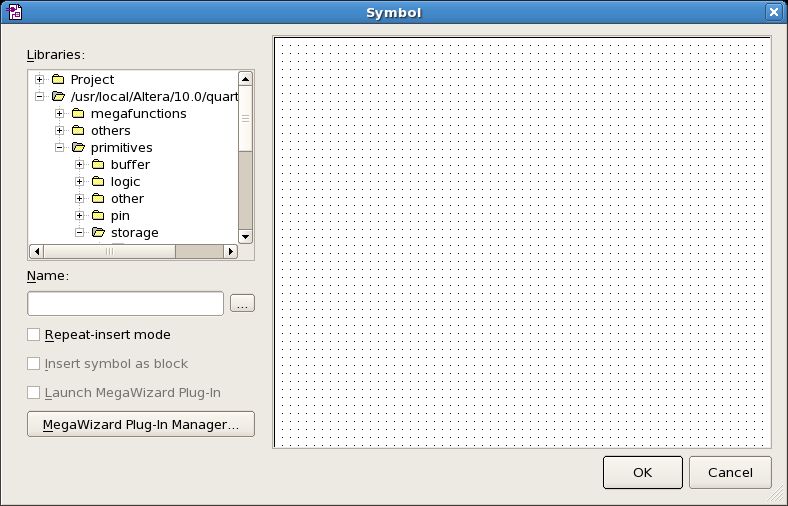

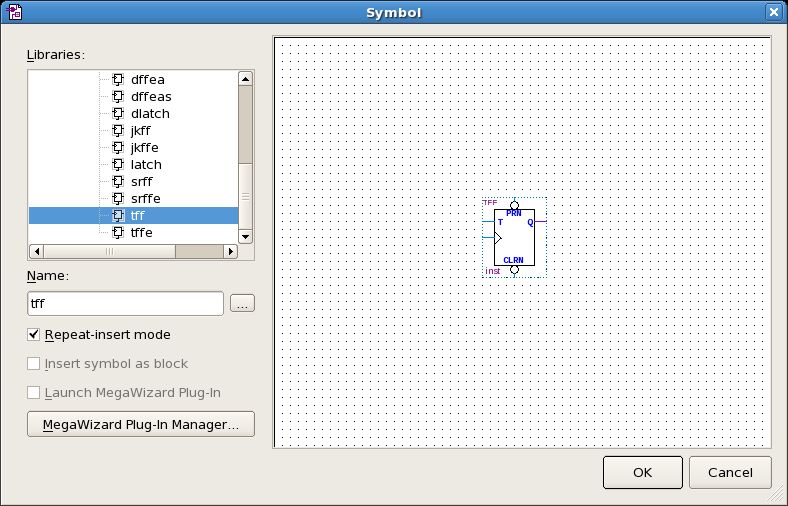

b)符号窗口加载了两个库。一个将项目中所有的文件都制作成更简单的块。另一个是Quartus随附的默认库。单击默认库旁边的+展开。

请参见图片。c)我们的组件位于基本文件夹下。单击+将其展开。

d)触发器在存储文件下。单击+将其展开。

e)选择tff。 f)由于需要倍数,因此单击选项“重复插入模式”。

g)按OK,然后在空白处单击以添加T型触发器。 (单击一次)

注意:要停止任何命令或离开新窗口,请按退出键。

请参见图片

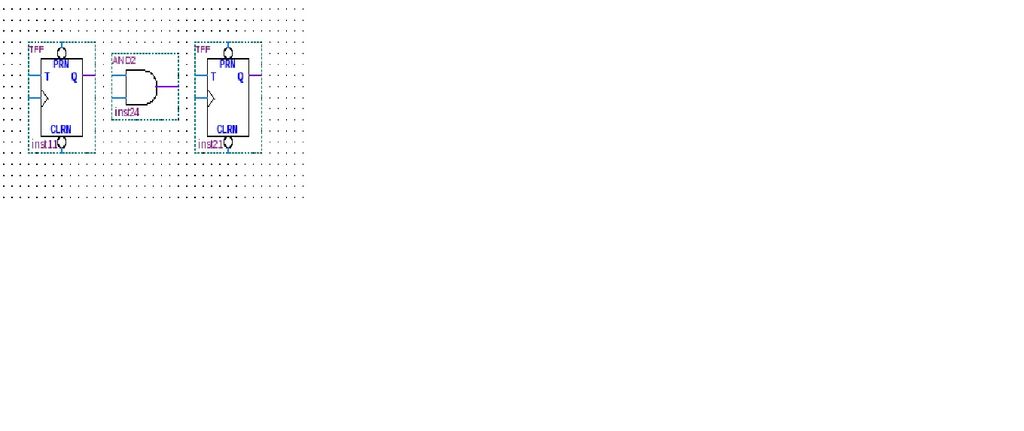

3)将触发器分成两个水平行,每行5个。在触发器之间留出大约2块空间。

注意:对于这些指令,1块区域将与触发器相同。

请参见图片

4)添加8个2输入与门。 》 a)像打开T触发器一样打开符号窗口。 b)文件夹仍应展开。通过单击+展开逻辑文件夹。c)选择AND2。我们想要倍数,因此请确保单击选项“重复插入模式”。

d)单击以添加AND门。

5)将AND门置于每个触发器之间,从第二个触发器之后开始。

注意:最好从左到右进行电路流动。

a)如果您已经添加了AND门并且需要排列它们,只需单击并拖动即可。将鼠标左键放到要打开门的位置。

6)在第一个触发器之前添加一个输入引脚。

a)引脚位于PIN文件夹下。展开它以选择输入选项卡。

7)通过双击pin_name并更改它来标记输入引脚CLK_IN。

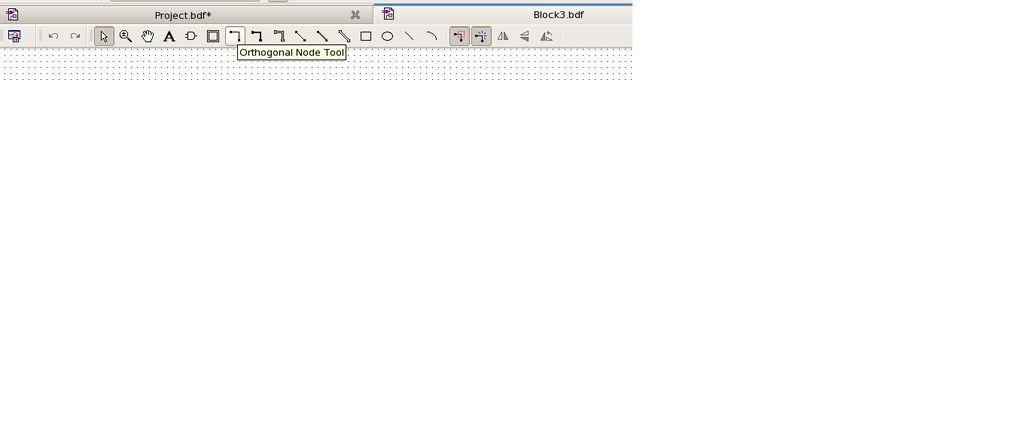

8)单击正交节点工具。

请参见图片

9)连接T触发器上每个三角形的输入引脚,也称为时钟输入。 a)单击并拖动以创建导线。确保电线连接到每个组件上的电线。

警告:当三根或更多根电线以直角相交时,会形成一个“节点”。该节点看起来像一个点。请注意哪些电线正在相互连接。

10)从零件清单中添加VCC。

a)VCC位于“ other”文件夹下。

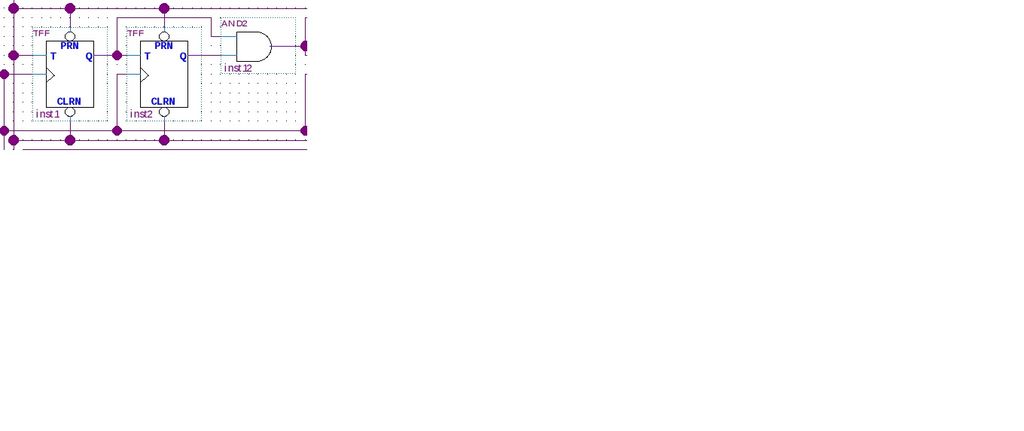

11)使用正交节点工具,将VCC连接至T的T。第一个触发器以及每个触发器的PRN和CLRN。

12)将第一个触发器的Q连接到第二个触发器的T。

参见图片

13)连接每个AND门的一个输入。

14)将“与”门的另一个输入连接到它前面的触发器的T。

15)将“与”门的另一个输入连接到它前面的触发器的T。《15》

16)添加一个输出引脚。

参见图片

17)标记输出引脚CLK_OUT。

18)将最后一个触发器的Q连接到输出引脚。

T触发器用作时钟分频器。通过将第一触发器的T连接到VCC(高电压),第一触发器在每个时钟周期将其输出Q(从1切换为0或反之亦然)。 Q连接到第二个触发器的T,因此第二个触发器的Q仅在其T为1且时钟从0变为1时才切换其值。从那里开始,每个其他触发器都需要在每个触发器之前在将其从0更改为1之前,它的值为1。每个时钟周期的周期变得更长,从而降低了时钟的速度。

19)保存文件。

20)使文件可用作块,单击“处理”,然后分析当前文件。

21)分析完文件后,单击文件,向下进行创建/更新,然后从旁边显示的菜单中单击“为当前文件创建符号文件”。 。

我们的电路现在已被制成一个隐藏了内部零件的块,并且仅显示输入和输出。仅当在其他文件中使用原始电路时,才会更改原始电路。要在另一个项目中使用,必须将每个电路文件的.bdf和.bsf文件复制到该项目的文件夹中。

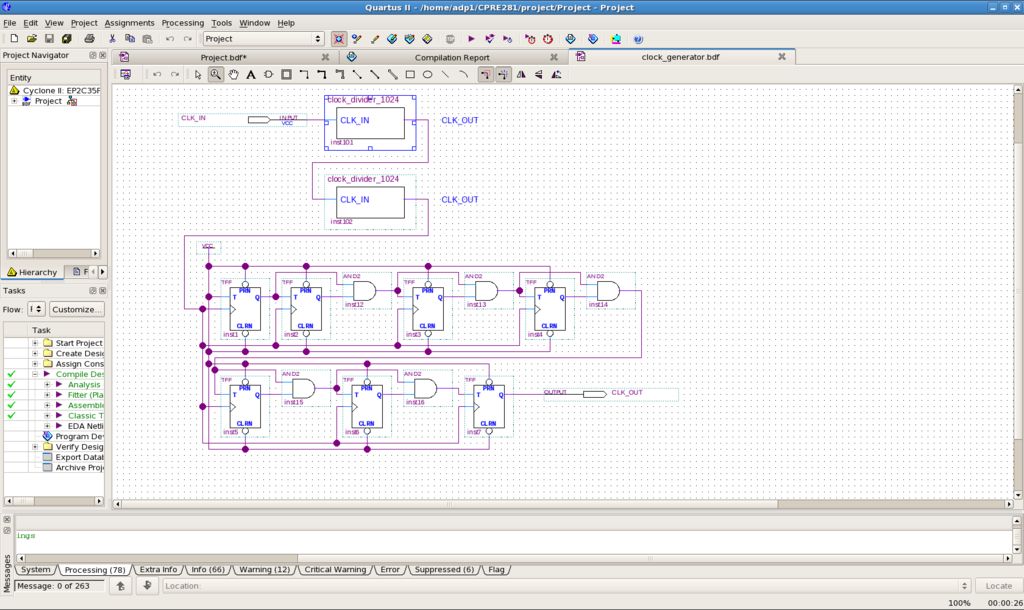

22)打开一个新文件(bdf),并将其命名为clock_generator。

23)在其中添加2个

a)在组件窗口中,展开4BitAdder文件夹。 b)选择clock_divider_1024并将其添加到文件中。

24)从clock_divider_1024文件中,复制整个电路并粘贴到新文件中。

25)将触发器的数量减少到8个,与门的数量减少到6个。

这可以通过以下方法完成:a)删除第8个触发器之后的所有内容, 将第8个触发器的Q连接到输出引脚。 c)删除将第8个触发器的T连接到其后的AND门的导线。 br》 26)删除将CLK_IN连接到第一个触发器的导线。

27)将CLK_IN连接到一个Clock_divider_1024的输入(左侧)。

28)将同一clock_divider_1024的输出(右侧)连接到输入29)将第二个clock_divider_1024的输出连接到第一个触发器的时钟输入(三角形)。

30)确保将VCC连接到每个触发器的PRN和CLRN,如下所示:以及电路的第一个触发器的T输入。

参见图片

31)保存文件。

32)分析文件。 (处理-》分析文件)

33)为文件创建符号。 (文件-》创建/更新-》创建符号)

34)在文件4BitAdder中,添加clock_generator。

步骤3:状态机

状态机跟踪我们正在处理的位置,以便可以轻松地进行下一步。我们的状态机将跟踪装载数量,发送每个位以进行加法并显示最终结果。

1)打开一个名为State_machine的新BDF。

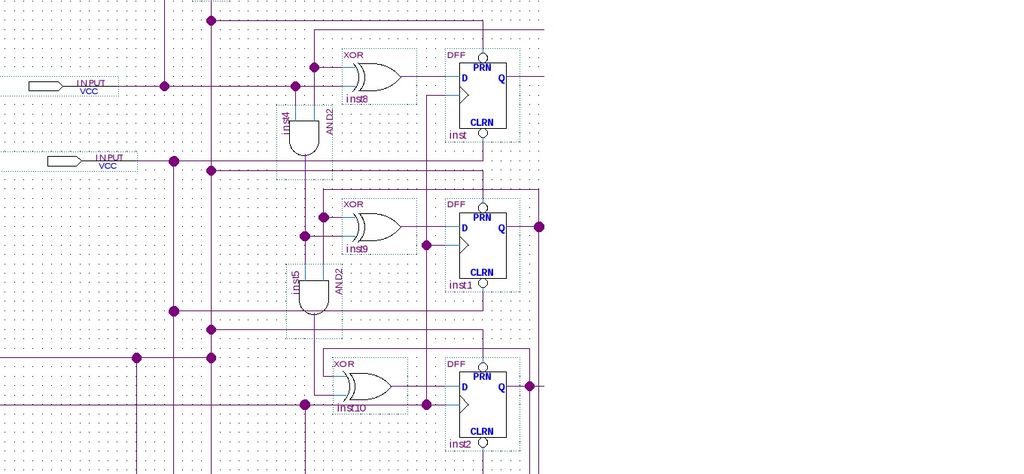

2)在垂直列中使用3D触发器添加符号工具。在它们之间保留1块空间。3)在每个D触发器的左侧添加3个2输入XOR门。少于一个空间是必要的,但要留出一些空间。

4)使用正交节点工具,将每个XOR门的输出(右侧)直接连接到D触发器D的右侧。

5)在顶部和底部两个XOR门的下方和下方添加2个2输入与门。

6)旋转每个AND门,使2个引脚朝上。要旋转,请单击在组件上

b)右键单击组件以显示菜单。 c)选择一个选项以翻转或旋转组件。

7)将每个“与”门的一个输入连接到一个输入。

8)将每个“与”门的另一个输入连接到其上方的“异或”门的另一个输入。

9)将每个D触发器的Q输出连接到以下一个: XOR门的输入直接在其左侧。

请参见图片

10)AND门的输出应连接至AND和XOR门的输入,该输入不与D的Q连接。触发器。

注意:一个XOR输入从D fli连接到Q。 p触发器和与门的输入。另一个XOR输入连接到AND门的另一个输入,以及如果它上面有一个AND门,则其上面的AND门的输出。

11)对于第三个XOR门,一个输入将连接到

12)另一个输入连接到右侧D触发器的Q。

参见图片《13》 13)添加VCC引脚。

推荐的位置是到当前组件的左上角

14)将VCC连接到每个D触发器的PRN。

15)在到目前为止的左边添加3个输入引脚3个块。

16)第一个输入引脚控件。

17)将第一个输入引脚连接到连接第一个XOR门和第一个AND门的导线。不要将它连接到连接到D触发器Q的导线。

18)将第二个输入引脚标记为“清除”。

19)将第二个输入引脚连接到每个D触发器的CLRN。

20)标记第三个输入引脚“时钟”。

21)连接第三个输入引脚。每个D触发器的时钟输入(三角形)的输入引脚。

22)加3

23)标记第一个输出引脚Select1。

24)将select1连接到第一个D触发器的Q。

25)标记第二个输出Select2。

26)将select2连接到第二个D触发器的Q。

27)标记第三个输出引脚select3。

28)将select3连接到第三个D触发器的Q。

参见图片

29)保存文件。

30)分析文件。

31)为文件创建符号。

32)在4BitAdder的clock_generator右侧添加state_machine。

步骤4: 7段显示器

我们也希望加法器也看起来像计算器。计算器显示要添加的数字及其总和。为了在板上显示我们的数字,我们的7段显示器将采用我们数字的二进制表示形式,并将其显示在典型的数字显示器上。

1)用二进制写出数字0-9,以及每个数字如何影响

注意:这些条在顺时针方向上标记为AG。每个输出A-G都会受到输入0000-1001的影响。 (完整的7段显示器使用十六进制,0-9和AF执行0-F,但我们将不需要它。如果以后要重用它,对AF进行编程将非常有用。我将介绍7的完整实现-段显示。)在对7段显示进行编程时,输出0对应点亮的条,而1则表示不点亮。

请参见图片

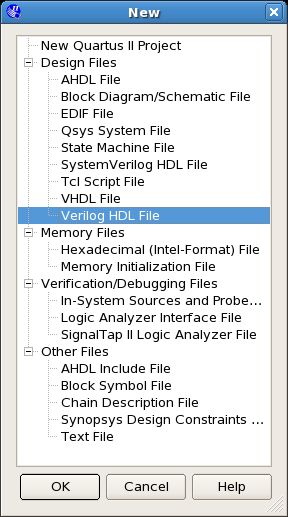

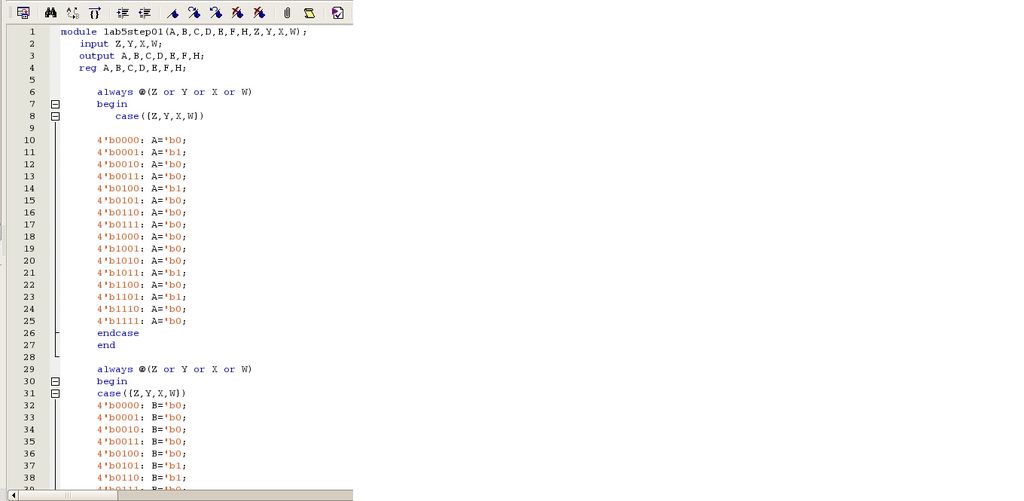

2)创建Verilog HDL文件。

请参见图片

此文件将与其他文件不同。每个段的输出将以二进制形式特别说明。该文件将被编码。

3)另存为7_segment_display。

4)在第一行中,输入“ module 7_segment_display(A,B,C,D,E,F,G,W,X,Y ,Z);”。

注意:AG是我们的输出,与数字时钟中的7段相对应。 W-Z是我们的输入,对应于我们二进制数的每个数字。这些区分大小写。保持相同。

5)在第二行中,输入“输入W,X,Y,Z;”。

6)在第三行中,输入“输出A,B,C,D,E

7)在第四行上,输入“ reg A,B,C,D,E,F,G;”。

8)跳到第六行。

9)输入“总是@(W或X或Y或Z)”。

10)在第7行,输入“开始”。

11)第8行将说“ case({W,X,Y, Z})”。

第6-8行将在每种情况下开始。每种情况都包含不同的输入可能性以及每个输入的输出结果。

12)跳到第10行,输入“ 4‘b0000:A =’b0;”。

13)在线在11中,输入“ 4‘b0001:A =’b1;”。

“ 4‘b”告诉计算机我们的输入将是4位二进制数字,而不是十进制,十六进制或八进制。对于每个给定输入,都给出A的输出,该输出只能有1个小数,对应于2个可能的输出。

14)使用上面显示的输入/输出表,并完成输入的情况A.

15)输入完所有大小写后,就可以在第26行输入了。

16)在第26行输入了“ endcase”。

17)在第27行输入了“

请参见图片

18)跳到第29行,对输出B开始相同的过程。

19)为了使代码易于阅读,请在每个输出的外壳之间保留空格。 》 20)如果按照建议保留空格,则在完成输出G的格时,下一个空行将是第161行。

21)在该空行上,输入“ endmodule”。

22)保存文件。

23)分析文件。

24)创建7_segment_display的符号。

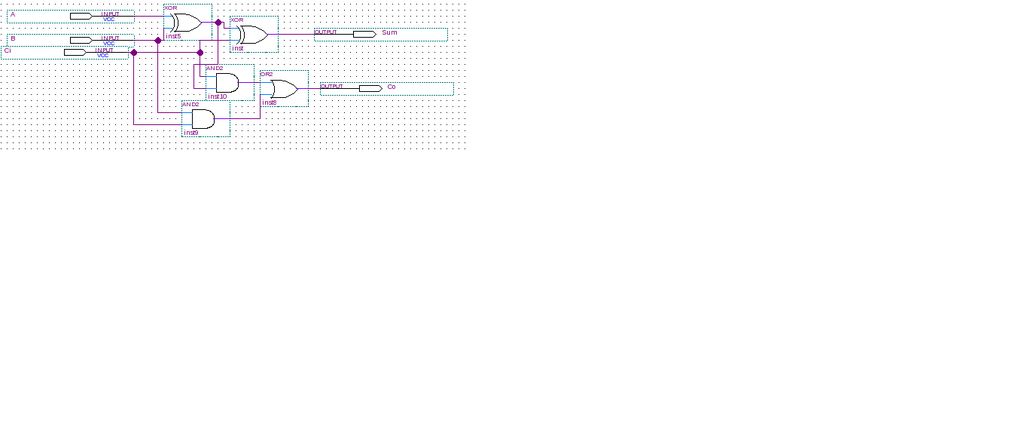

步骤5:Full_adder

完整加法器是在整个程序中进行实际加法的设备。该组件接收两位并执行按位加法。加法运算首先经过0的位置,然后经过1的位置,依此类推。如果前一个进位有进位,则也必须添加进位。半加法器不考虑先前数学运算中的进位。

1)创建一个新的BDF。

2)将其另存为Full_adder。

3)将2个XOR门并排添加到文件中。

4)在右XOR门下方添加2个2输入与门。 “与”门应垂直排列。

5)在2个“与”门的右边添加一个2输入“或”门,大约在两个垂直门之间。

6)将一个“或”门的输出连接到另一个XOR门的一个输入。

7)将同一根导线连接到顶部AND门的一个输入。

8)将那个AND门的另一个输入连接到右XOR门的另一个输入。 br》 9)将“与”门的输出连接到“或”门的输入。

请参见图片

10)在垂直线的左边添加3个输入引脚。

11 )标记顶部引脚A。

12)将A连接到左侧XOR门的一个输入和底部AND门的一个输入。

13)标记第二个引脚B。

14)连接B

15)标记第三个引脚Ci(进位)。

16)将Ci连接到连接到XOR门的另一个输入的导线(进位)。右XOR门与顶部AND门的输入。

17)添加2个输出引脚。

18)标签一个总和。

19)连接总和到右XOR门的输出。

20)标记第二个Co(执行)。

21)将Co连接到OR门的输出。

参见图片

22)保存该文件。

23)分析该文件。

24)为full_adder创建一个符号。

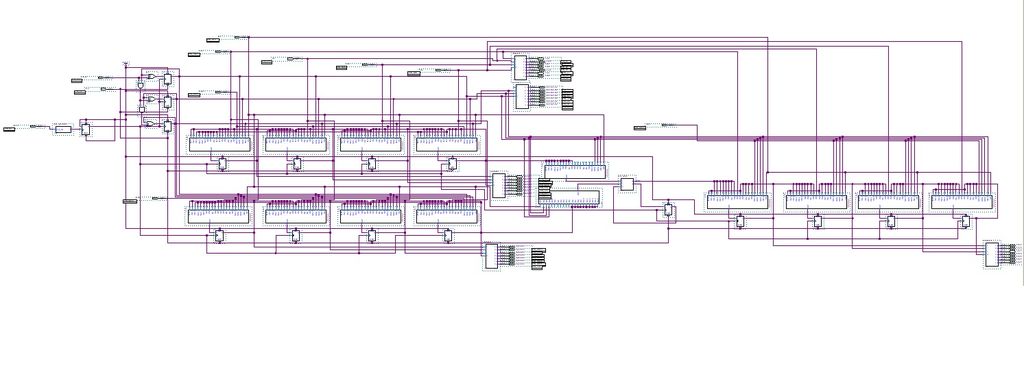

步骤6:将其放在一起

4位加法器的所有较小部分均已创建。我们剩下的部分是将组件添加到必要的位置,然后将它们连接在一起(令人困惑的部分)。

到目前为止,我们的4BitAdder中具有clock_generator和state_machine。 (clock_generator应该在状态机的左侧。)

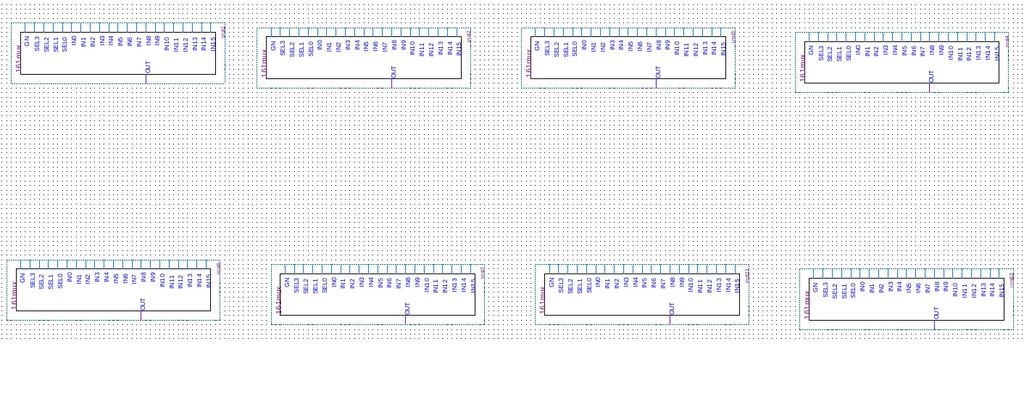

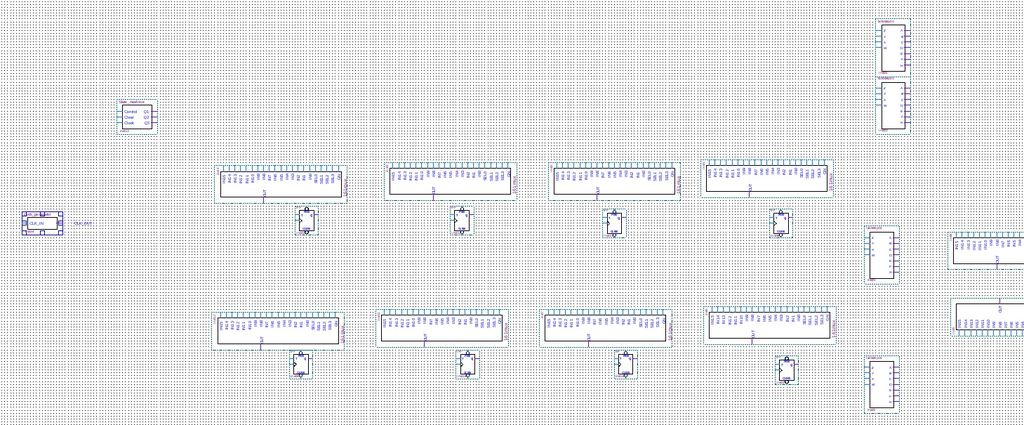

1)添加8个16输入MUX(161MUX)。

a)展开默认库下的other文件夹。 b)展开maxplus2 .c)添加16输入多路复用器。2)将8个MUX排列成两行,每行四长。它们应该在state_machine的右侧(因此也应该在clock_generator的右侧)。如果它们稍微低于state_machine,则更容易。

a)MUX需要旋转,以使一个输出朝下。 b)每个MUX水平之间留出1块空间,并且3-4两行之间垂直分隔。

每组4个MUX接受输入。我们发送到选择输入的信号决定哪个信号将出现在输出上。

3)从左到右标记顶部的MUX RegA3-RegA0,指示数字A的位3位0。

4 )标记底部的MUX RegB3-RegB0。

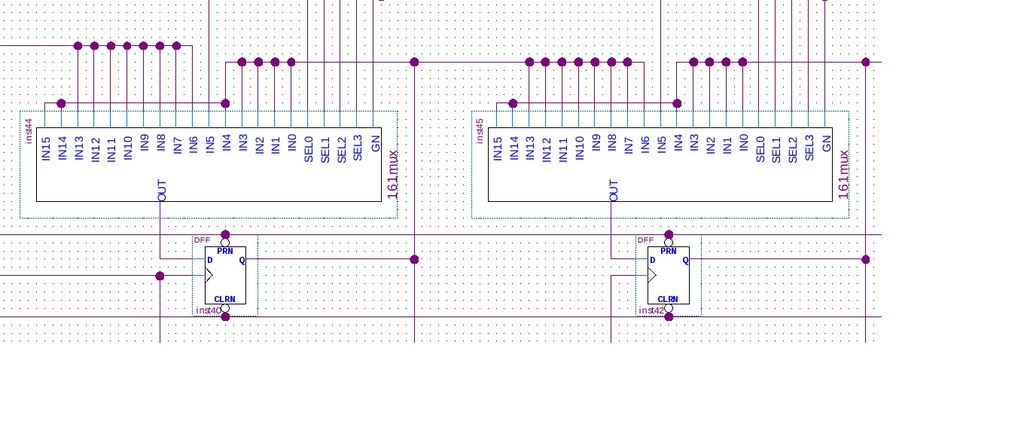

参见图片

5)添加8个D型触发器。

a)每个MUX下方应放置一个触发器。

D型触发器有助于将MUX放在时钟上。 MUX选择的任何信号都将按其方式发送,但是通过添加触发器,它只会在时钟信号到来时发送。

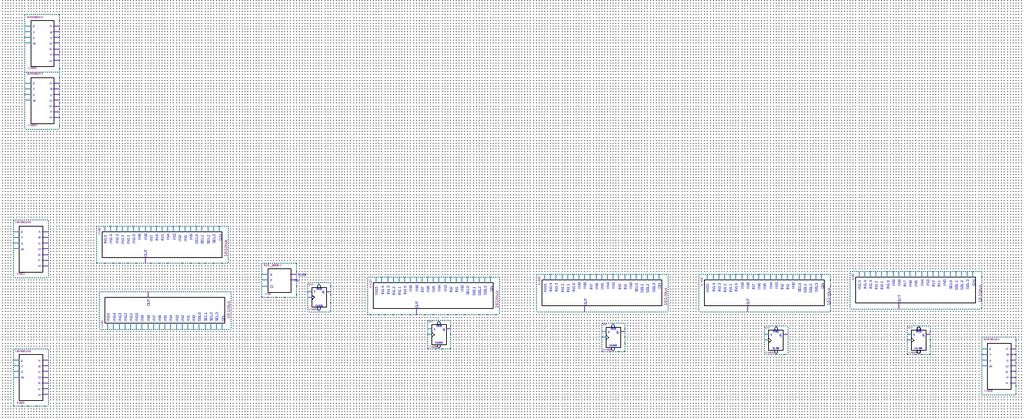

6)加4 7_segment_display。

a)所有四个将被发送。在MUX的右侧,它们与MUX之间大约有3个空间。

b)四个中的两个将位于MUX的上方,但仍保留在MUX的右侧。c)其中一个7_segment_displays将位于两组MUX之间。

d)最后一个将位于底部的MUX组之下。

7_segment_displays将帮助我们了解电路中正在发生的事情。一个让我们看看将要输入的数字。另一个告诉我们状态机在哪里,只有3个D触发器,选择范围是0到7。该组的最后两个显示只是为了确保电路正常工作。 MUX和D触发器用作移位器。如果信号正确,则来自一个MUX的信号将被发送到右侧的MUX。稍后,这还将最右边的位移入加法器。 7_segment_displays会告诉我们每组MUX发出了什么信号。这可以用来解决任何问题。

e)将顶部7_segment_display标记为Number。将第二个显示器标记为StateMachine。

g)将第三个显示器标记为RegA。

h)将第四个显示器标记为RegB。

参见图片

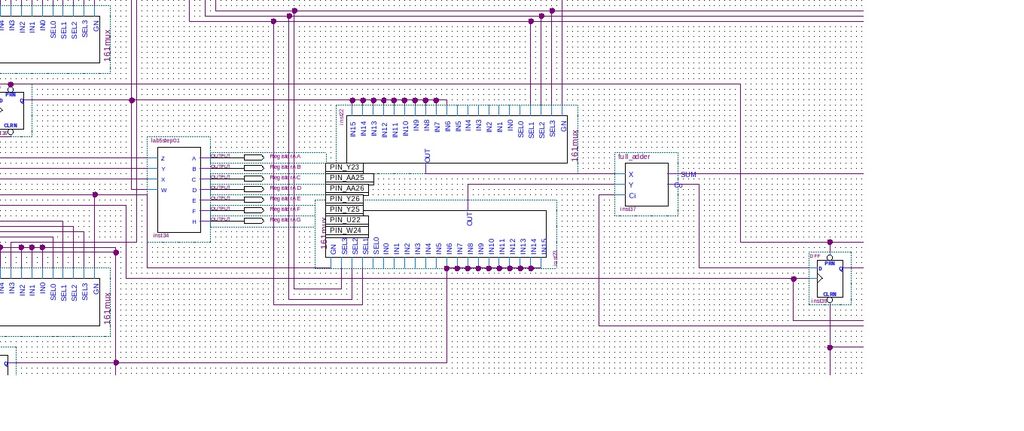

7)再添加两个两个16输入MUX,一个在另一个之上,顶部的输出朝下,底部的输出朝上。 )这些MUX应该在右侧,并且大约在其他MUX组之间。 (对于顶部MUX组,这些MUX也在7_segment屏幕的右侧。标记顶部MUX AddBitA。标记底部MUX AddBitB。

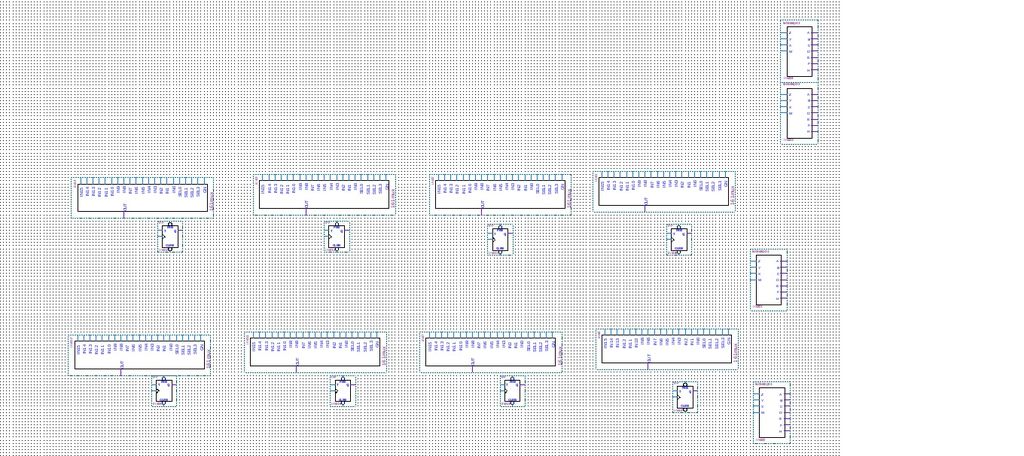

8)将full_adder添加到

9)在full_adder的右边添加一个D触发器,将其放低大约一半。

10)将4个16输入MUX添加到T触发器的右侧。在每个组件之间保留1块空间。

a)从左到右标记MUX RegC3-RegC0。

11)在每个MUX下方添加4个D触发器。

12)在右侧添加7_segment_display

请参见2图片

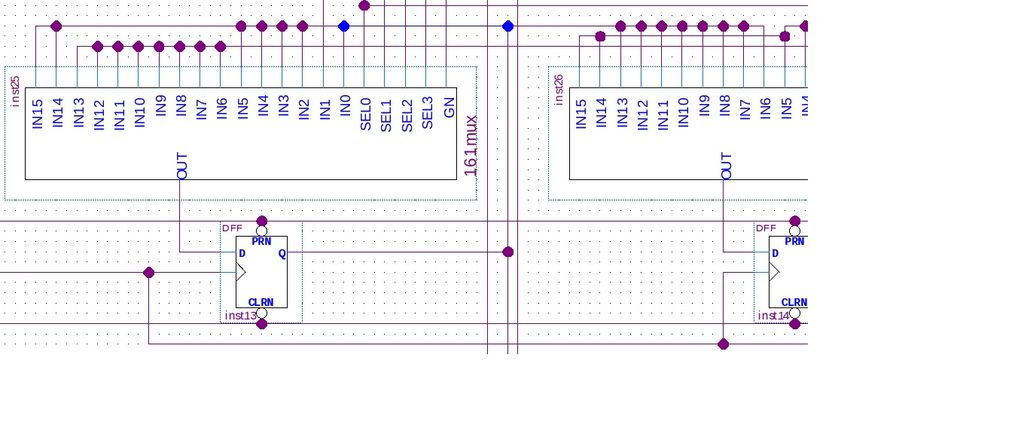

13)将state_machine的输出Q1连接到每个MUX的SEL1。

14)将state_machine的输出Q1连接到7_segment_display标记为StateMachine的输入Z

15)将状态机的输出Q2连接到每个MUX的SEL2。

16)将状态机的输出Q2连接到标记为StateMachine的7_segment_display的输入Y。

17)将状态机的输出Q3连接到每个MUX的SEL3。

18)将state_machine的输出Q3连接到标有StateMachine的7_segment_display的输入X。

19)将每个MUX的输出连接至其下面的D触发器的D输入。 》 20)标有AddBitA和AddBitB的MUX的输出应连接到full_adder的X和Y(一个输出到一个输入)。

21)连接D的Q输出RegA3 MUX下方的触发器连接到RegA3 MUX的输入IN0,IN2-IN5,IN14和IN15。

22)还将相同的Q输出连接到RegA2 MUX的输入IN6-IN13。

23)重复步骤每个RegA2-RegA0下方的D触发器的16和17。

a)RegA2-RegA0的D触发器的Q输出始终连接到其上方和右侧的寄存器的相同输入。类似于RegA3。b)对于RegA0下面的D触发器的第17步,Q连接到RegA3的输入IN6-IN13。

参见图片

24)在RegA3下面的D触发器的Q输出连接。到RegA 7_segment_decoder的输入W。

25)将RegA2下方的D触发器的Q输出连接到RegA的输入X。

26)将RegA1下方的D触发器的Q输出连接到RegA1的输入Y。 。

27)将RegA0下方的D触发器的Q输出连接到RegA的输入Z。

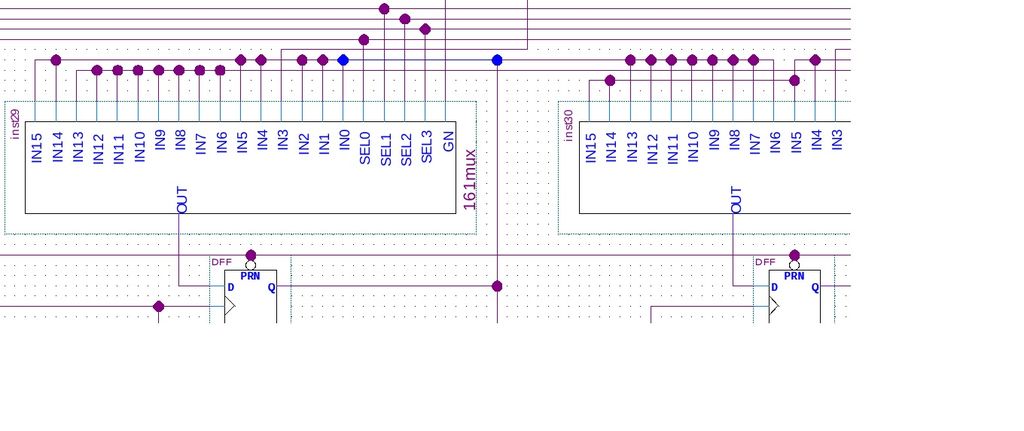

28)将RegB3 MUX下方的D触发器的Q输出连接到输入IN0-IN2,IN4,IN5, RegB3 MUX的IN14和IN15。

29)将相同的输出Q连接到输入IN6- RegB2 MUX的IN13。

30)对RegB2-RegB0以下的D触发器重复步骤23和24。a)RegB2-RegB0的D触发器的Q输出始终连接到寄存器的相同输入b)对于RegB0下面的D触发器的第24步,Q连接到RegB3的输入IN6-IN13。

参见图片

31)连接在RegB3之下的D触发器的输出Q到RegB 7_segment_decoder的输入W。

32)在RegB2之下的D触发器的输出Q连接到RegB2的输入X。

33)将D触发器的输出Q连接到

34)将RegB0下方的D触发器的输出Q连接到RegB0的输入Z。

35)将RegC3 MUX下方的D触发器的Q输出连接到Reg0的输入Z。 RegC3 MUX的IN4,IN14和IN15。

36)将D触发器的相同Q输出连接到RegC2的输入IN6-IN13。

37)对RegC2下面的每个D触发器重复步骤30和31。 -RegC0。

a)RegC2-RegC0的D触发器的Q输出始终连接到就像RegC3一样,位于寄存器上方和右侧的寄存器的输入相同。

b)RegC0的D触发器的Q输出未连接到RegC3的任何输入。

请参见图片

38)将RegC3下方的D触发器的输出Q连接到RegC 7_segment_Decoder的输入W。

39)将RegC2下方的D触发器的输出Q连接到RegC2的输入X。

40)将RegC2下方的D触发器的输出Q连接到RegC。 RegC1之下的D触发器到RegC的输入Y。

41)RegC0之下的D触发器的输出Q连接到RegC0的输入Z。

42)RegA0之下的D触发器的输出Q连接到RegC0的输入到IN6。 AddBitA MUX的-IN15。

43)将RegB0下面的D触发器的输出Q连接到AddBitB MUX的输入IN6-IN15。

注意:这两个MUX的其余输入和SEL0将保留。悬空。这可能会在某些电路中引起问题,但不适用于此电路。请注意,如果确实引起问题,则将输入连接到VCC或GND通常可以解决问题。 VCC类似于1,GND类似于0。

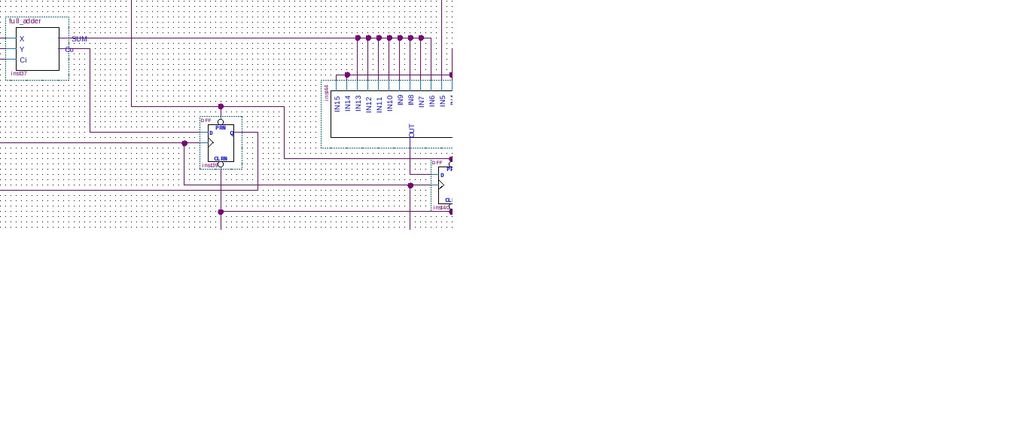

请参见图片《44》将full_adder的输出Sum连接到RegC3 MUX的输入IN6-IN13。

45)将full_adder的输出Co连接到RegC3 MUX的D输入。 D触发器在其右侧。

46)将D触发器的Q输出连接至full_adder的输入Ci。

请参见图片

47)在您所有的左侧添加3个输入引脚

48)将输入标记在clock_generator时钟的左侧。

49)将其连接到clock_generator的输入。

br》 50)将clock_generator的输出连接到每个D触发器的时钟输入。

51)将相同的输出连接到state_machine的时钟输入。

52)在其左侧标记一个输入引脚state_machine Control。

53)将Control连接到state_machine的输入标签控件。

54)将第三个输入引脚标记为Clear。

55)将Clear连接到state_machine的clear输入。

56 )连接相同的清除每个D触发器的CLRN的输入引脚。

57)在RegA3 MUX上方添加6个输入引脚。

58)标记第一个输入引脚LoadA。

59)将LoadA连接到RegA3-RegA0的SEL0。

60)将第二个输入引脚标记为Bit3。

61)将Bit3连接到RegA3的IN1,RegB3的IN3,RegC3的IN5,以及标记为Number的7_segment_display的输入W。

62)标记第三个输入引脚Bit2。

63)将Bit2连接到RegA2的IN1,RegB2的IN3,RegC2的IN5,以及标记为Number的7_segment_display的输入X。

64)标记第四个输入引脚Bit1。

65)连接RegA1的位1到IN1,RegB1的IN3,RegC1的IN5和标有编号的7_segment_display的输入Y。

66)标记第五个输入引脚Bit0。

67)将Bit0连接到RegA0的IN1,IN3 RegB0,RegC0的IN5和标记为Number的7_segment_display的输入Z。

68)标记第六个输入引脚Gn。

69)将Gn连接到每个MUX的输入GN。

70)添加输入销到RegB3 MUX的左侧。

71)将其标记为LoadB。

72)将LoadB连接到RegB3-R的SEL0 egB0。

73)在RegC3 MUX的左侧添加一个输入引脚。

74)在引脚C上标记负载C.

75)将LoadC连接到RegC3-RegC0的SEL0。

76)添加7个输出标记为Number的7_segment_display右侧的引脚。

77)标记输出InputA-InputG。

78)将Number的输出AG连接到其相应的输出引脚。

79)在右侧添加7个输出引脚of 7_segment_display StateMachine。

80)在输出上标记StateMachineA-StateMachineG。

81)将StateMachine的输出AG连接到其相应的输出引脚。

参见图片

82)在7的右侧添加7个输出引脚。 7_segment_display RegA。

83)标记输出RegAA-RegAG。

84)将RegA的输出AG连接到其相应的输出引脚。

85)在7_segment_display RegB的右侧添加7个输出引脚。 》 86)将输出RegBA-RegBG标记。

87)将RegB的输出AG连接到其相应的输出引脚。

88)在7_segment_display RegC的右侧添加7个输出引脚。

89)标记输出SumA-SumG。

90)将RegC的输出AG连接到其相应的输出引脚。

请参见图片

91)保存文件。

92)单击“处理”。

93)转到“开始编译”(此处将花费几分钟。)

程序可能会出现一些警告,但我们的电路仍应正确加载到FPGA。

参见图片

步骤7:引脚分配

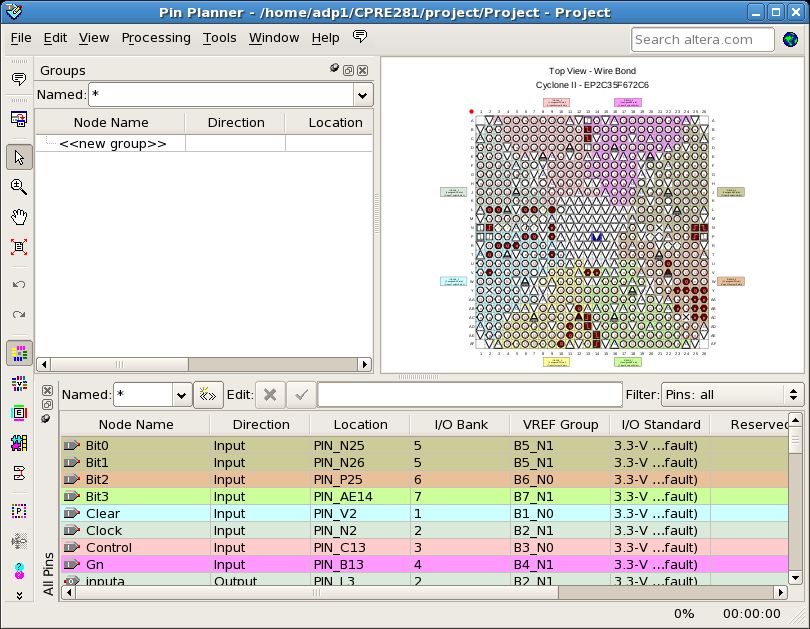

由于完成了项目电路,因此需要将输入和输出引脚分配给FPGA板上的开关和LED。这将是测试电路是否正常的测试。

1)单击“ Assignments”。

2)进入“ Pin Planner”。

将出现一个新窗口,其中包含您输入的所有输入和输出引脚。

请参见图片

3)拿起FPGA手册或在Google上查找设备的引脚分配。

引脚分配应通过所有开关,LED,按钮和7段显示器。每个位置将在同一行中给出。 (例如:PIN_N25)

4)在引脚规划器上找到Bit0-Bit3(应按字母顺序)。

5)选择要为每个引脚使用的开关(我对bit0-使用了switch0-switch3分别为Bit3)

6)在您的手册中找到要使用的开关并找到其位置ID。

7)在引脚规划器中,单击位置框,然后使用下拉菜单选择

8)对于您的输出,请确保该引脚对应于7段显示器的正确段。

9)输入Clock应该连接到内部时钟源。请确保使用可与clock_generator正确缩放的适配器。

注意:确保输入引脚仅是开关和按钮。我们所有的输出应该是7段显示器。

这里是您可以做的一个例子。

•Bit0-Bit3的Switch0-3。

•LoadA

的开关4• LoadB

•LoadC

的开关6•Control

的开关7•Gn

的开关8•Clear的开关17(由于它会复位整个电路,因此我们尝试使其远离开关我们会更定期地移动)

•输入A-InputG的HEX7

•StateMachineA-StateMachineG 的HEX5•RegAA-RegAG

HEX3•RegBA-RegBG

HEX2•SumA的HEX0

责任编辑:wv

-

gztoppower

2022-08-22

0 回复 举报http://house.china.com.cn/sousou/%25CF%25C2%25B7%25D6%252C%2B%25F6%25CE%25CA%25A4%25D3%25E9%25C0%25D6%25B5%25C7%25C2%25BC%25CF%25B5%25CD%25B3B2024.cN%252C%25D6%25DC%25BF%25DA%25CE%25C0%25C9%25FA%25BE%25D6_2s.htm http://house.china.com.cn/sousou/%25CB%25D1%25BA%25FC%252C%2B%25C3%25E5%25B5%25E9%25D3%25C0%25B2%25FD%25D3%25E9%25C0%25D6%25B9%25AB%25CB%25BEB2024.cN%252C%25BB%25E1%25D4%25B1%25B5%25C7%25C2%25BC_2s.htm http://house.china.com.cn/sousou/%25B9%25D9%25B7%25BD%25CD%25F8%25D5%25BE%252C%2B%25C3%25E5%25B5%25E9%25D3%25C0%25B2%25FDB2024.cN_61s.htm http://house.china.com.cn/sousou/%25CA%25D6%25BB%25FA%25D4%25DA%25CF%25DF%252C%2B%25C3%25E5%25B5%25E9%25C5%25B7%25D1%25C7%25B9%25FA%25BC%25CA%25B5%25E3%25BB%25F7%25B2%25BFB2024.cN%252C%25B8%25A3%25D6%25DD%25D2%25BD%25B1%25A3_2s.htm http://house.china.com.cn/sousou/%25BA%25F3%25CC%25A8%252C%2B%25C3%25E5%25B5%25E9%25C3%25E5%25B1%25B1%25D3%25E9%25C0%25D6%25B5%25E3%25BB%25F7%25B2%25BFB2024.cN%252C%25BD%25FA%25D6%25D0%25CE%25C0%25BC%25C6%25CE%25AF_7 收起回复

gztoppower

2022-08-22

0 回复 举报http://house.china.com.cn/sousou/%25CF%25C2%25B7%25D6%252C%2B%25F6%25CE%25CA%25A4%25D3%25E9%25C0%25D6%25B5%25C7%25C2%25BC%25CF%25B5%25CD%25B3B2024.cN%252C%25D6%25DC%25BF%25DA%25CE%25C0%25C9%25FA%25BE%25D6_2s.htm http://house.china.com.cn/sousou/%25CB%25D1%25BA%25FC%252C%2B%25C3%25E5%25B5%25E9%25D3%25C0%25B2%25FD%25D3%25E9%25C0%25D6%25B9%25AB%25CB%25BEB2024.cN%252C%25BB%25E1%25D4%25B1%25B5%25C7%25C2%25BC_2s.htm http://house.china.com.cn/sousou/%25B9%25D9%25B7%25BD%25CD%25F8%25D5%25BE%252C%2B%25C3%25E5%25B5%25E9%25D3%25C0%25B2%25FDB2024.cN_61s.htm http://house.china.com.cn/sousou/%25CA%25D6%25BB%25FA%25D4%25DA%25CF%25DF%252C%2B%25C3%25E5%25B5%25E9%25C5%25B7%25D1%25C7%25B9%25FA%25BC%25CA%25B5%25E3%25BB%25F7%25B2%25BFB2024.cN%252C%25B8%25A3%25D6%25DD%25D2%25BD%25B1%25A3_2s.htm http://house.china.com.cn/sousou/%25BA%25F3%25CC%25A8%252C%2B%25C3%25E5%25B5%25E9%25C3%25E5%25B1%25B1%25D3%25E9%25C0%25D6%25B5%25E3%25BB%25F7%25B2%25BFB2024.cN%252C%25BD%25FA%25D6%25D0%25CE%25C0%25BC%25C6%25CE%25AF_7 收起回复

-

加法器的原理是什么 加法器有什么作用2024-05-23 8608

-

4位加法器的构建2023-07-04 919

-

加法器的原理及采用加法器的原因2023-06-09 6815

-

4位加法器开源分享2022-07-08 956

-

4位加法器的资料分享2022-07-07 1766

-

12位加法器的实验原理和设计及脚本及结果资料说明2019-04-15 3039

-

怎么设计一个32位超前进位加法器?2018-07-09 22346

-

八位加法器仿真波形图设计解析2017-11-24 33865

-

关于Quartus中的加法器2015-01-11 6363

-

两个4位加法器级联构成一个8位加法器 verilog怎么写啊?!!2013-12-03 17170

-

32位浮点加法器设计2013-10-20 4227

-

8位加法器和减法器设计实习报告2013-09-04 2733

-

加法器,加法器是什么意思2010-03-08 5950

-

4位并行的BCD加法器电路图2009-03-28 14698

全部0条评论

快来发表一下你的评论吧 !